PowerSoC:优化开关模式DC-DC转换器的噪声与空间问题

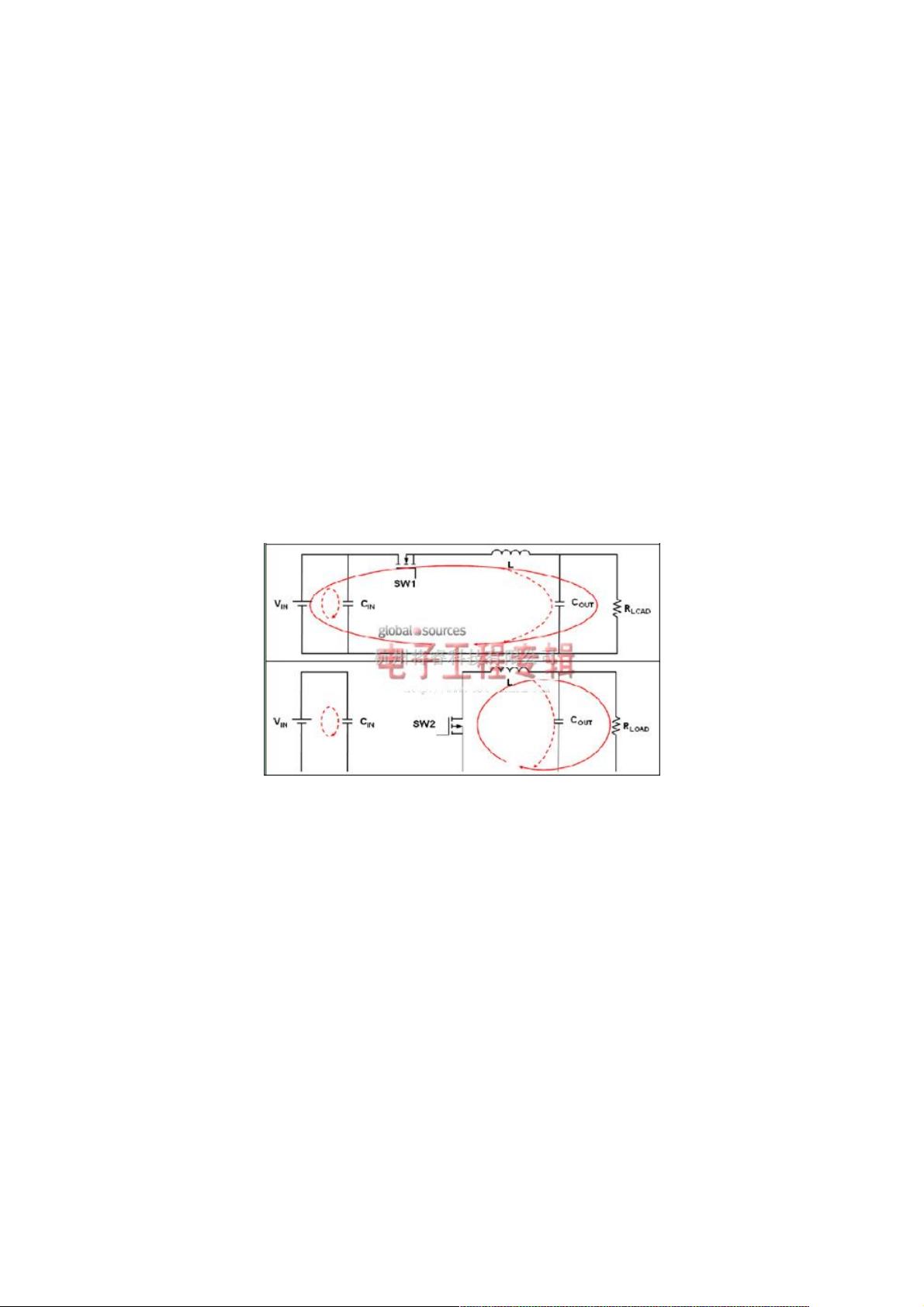

在现代FPGA系统设计中,由于开关模式直流-直流转换器(Switching Mode DC-DC Converter, SMDC)能够显著提升能量转换效率,它们成为了许多应用的首选。然而,这种转换器并非没有挑战,特别是对于高速输入/输出单元,它们往往是噪声源,可能对系统性能造成影响。本文主要关注于解决这些噪声问题,特别是通过PowerSoC技术。 首先,引言部分强调了开关模式DC-DC转换器的优点和缺点。优点在于效率提升,但缺点包括结构复杂、组件增多和占用更多空间,以及对高速电路产生的噪声。文章的焦点在于PowerSoC如何有效管理这些噪声,以确保系统的稳定性并维持高性能。 降压型DC-DC转换器的简单模型由一对MOSFET开关、电感器以及输入和输出滤波电容构成,形成同步工作模式。这个模型直观地展示了转换器的工作原理,即通过开关的交替开闭,电能被存储在电感器中并在需要时释放,同时滤波电容负责滤除高频交流噪声。 本文深入探讨了直流-直流转换器的主要噪声来源,包括输出侧的纹波电压(由于转换过程中电压波动)、输入电源侧的纹波电压(来自电源本身或上游转换器)、辐射性电磁干扰(EMI)和传导性电磁干扰(传导EMI)。为了减少这些噪声,PowerSoC采用了一系列策略,如优化滤波设计、使用低噪声元件、以及利用高级控制算法进行动态调整,确保输出电压的平稳性和电磁兼容性。 通过设计示例,文章展示了PowerSoC如何在保持高效转换的同时,通过创新的解决方案将噪声控制在一个可接受的范围内,使得高速输入/输出单元的表现能够接近或超越线性稳压器。这不仅提升了整个系统的性能,还减少了对系统架构的限制,为FPGA设计提供了更加灵活且高效的电源解决方案。 PowerSoC在电源技术中的应用,特别是在处理开关模式DC-DC转换器的噪声和空间问题方面,显示出了其在现代电子系统设计中的重要角色。通过有效的噪声管理和优化,它不仅提高了能源利用效率,还提高了系统的稳定性和可靠性,为FPGA和其他高性能设备的集成创造了更好的条件。

下载后可阅读完整内容,剩余4页未读,立即下载

- 粉丝: 7

- 资源: 927

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- ExtJS 2.0 入门教程与开发指南

- 基于TMS320F2812的能量回馈调速系统设计

- SIP协议详解:RFC3261与即时消息RFC3428

- DM642与CMOS图像传感器接口设计与实现

- Windows Embedded CE6.0安装与开发环境搭建指南

- Eclipse插件开发入门与实践指南

- IEEE 802.16-2004标准详解:固定无线宽带WiMax技术

- AIX平台上的数据库性能优化实战

- ESXi 4.1全面配置教程:从网络到安全与实用工具详解

- VMware ESXi Installable与vCenter Server 4.1 安装步骤详解

- TI MSP430超低功耗单片机选型与应用指南

- DOS环境下的DEBUG调试工具详细指南

- VMware vCenter Converter 4.2 安装与管理实战指南

- HP QTP与QC结合构建业务组件自动化测试框架

- JsEclipse安装配置全攻略

- Daubechies小波构造及MATLAB实现

信息提交成功

信息提交成功