Xilinx ISE IP核使用教程:从创建到仿真

需积分: 2 147 浏览量

更新于2024-09-11

1

收藏 1.04MB DOCX 举报

“学习Xilinx ISE记录,笔记记录了初学者使用Xilinx IP核进行设计开发的步骤,包括创建工程、调用IP核、生成主程序、综合与实现以及创建仿真文件。”

在数字电路设计中,Xilinx ISE(Integrated Software Environment)是一个广泛使用的工具套件,用于开发基于Xilinx FPGA(Field-Programmable Gate Array)和 CPLD(Complex Programmable Logic Device)的项目。IP核是预先验证过的硬件设计,可以被开发者重复使用,以加速设计流程并提高设计质量。本笔记主要介绍了使用Xilinx ISE集成开发环境和IP核进行设计的基本步骤:

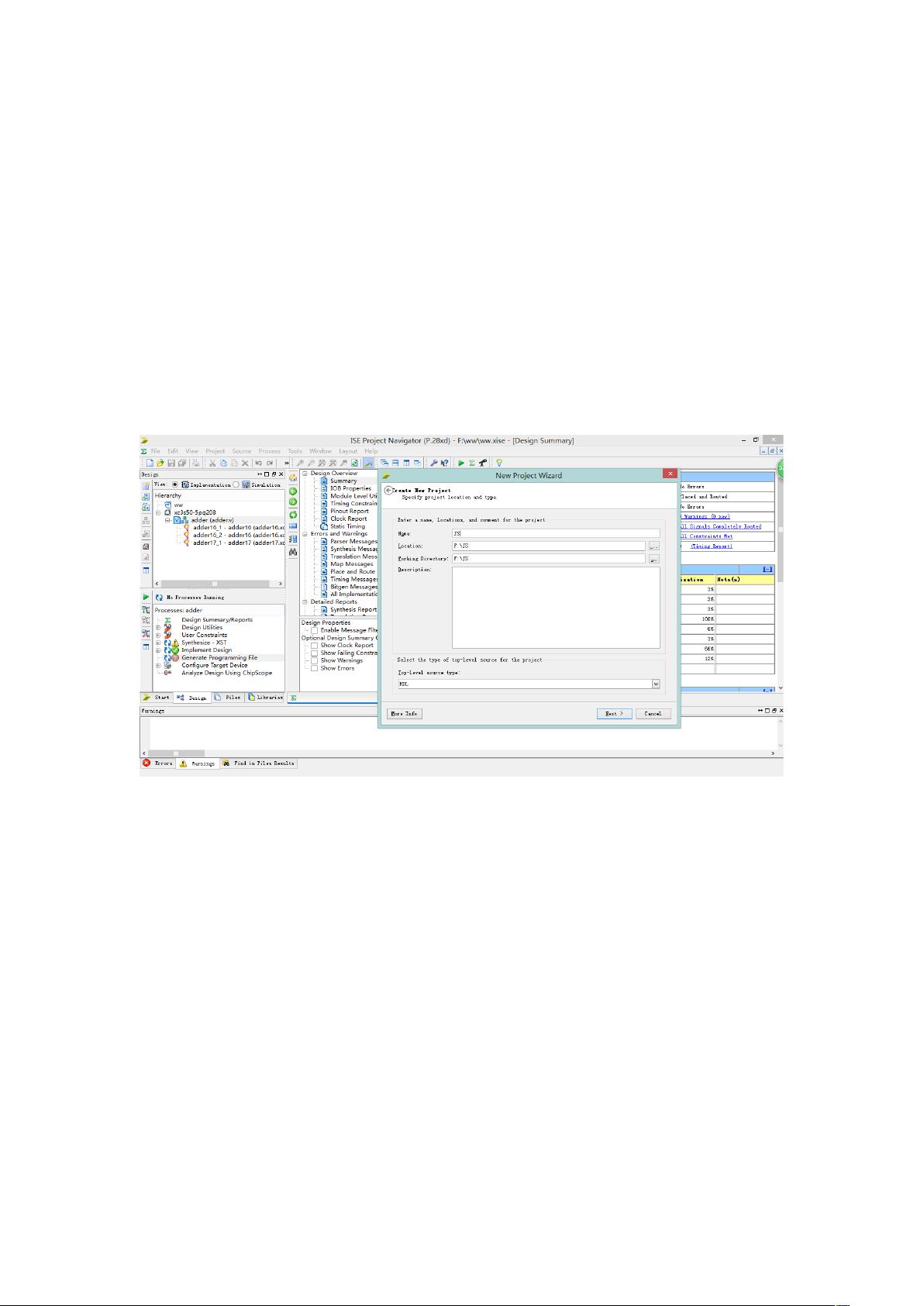

1. **创建工程**:首先,我们需要生成一个工程文件(JS文件),这标志着项目的开始。在这个例子中,选择了FPGA型号xc3s50-5pq208。

2. **调用IP核**:IP核是设计的核心,可以通过右键点击芯片选项来调用。在本例中,选择了加法器(adder)IP核。调用IP核后,需要设置其参数和配置,例如输入和输出端口的数量。

3. **创建IP实例**:创建两个IP核实例,分别命名为adder_16和adder_17,以便在主程序中使用。

4. **创建主程序**:在工程中创建一个Verilog模块(verylogmodule),命名adder,作为主程序,它将调用之前创建的IP核实例。

5. **查看和编辑HDL模板**:通过COREGenerator,查看并编辑IP核的HDL实例化模板,将实例名替换为你自定义的名字,连接输入和输出端口。

6. **编写主程序代码**:将IP核实例的模板代码插入到主程序中,连接输入和输出信号。这一步确保了IP核与主程序的通信。

7. **综合与实现**:完成编码后,需要对adder文件进行综合,这是检查和优化代码的过程,以适应目标硬件平台。随后进行实现,这一步会生成具体的门级逻辑布局。

8. **生成仿真文件**:为了验证设计的功能正确性,创建一个Verilog测试平台(Verilogtestfixture文件),用于对设计进行仿真。在这里,编写了测试文件,定义了输入和输出,以及如何实例化单元测试(UUT)。

9. **编写测试激励**:在测试文件中,定义了各个输入信号(如时钟、输入数据a1、a2、b1、b2)以及期望的输出(c)。这个测试激励将驱动设计并检查其输出是否符合预期。

通过以上步骤,初学者可以理解如何在Xilinx ISE中使用IP核进行设计,从而快速构建复杂的FPGA项目。这个过程中,IP核简化了设计流程,而ISE工具则提供了集成化的环境,使得设计、验证和实现变得更加高效。

195 浏览量

点击了解资源详情

点击了解资源详情

2021-11-24 上传

2011-01-06 上传

2011-10-20 上传

2021-10-07 上传

166 浏览量

102 浏览量