DocID15962 Rev 15 17/142

STM8L151x4/6, STM8L152x4/6 Functional overview

58

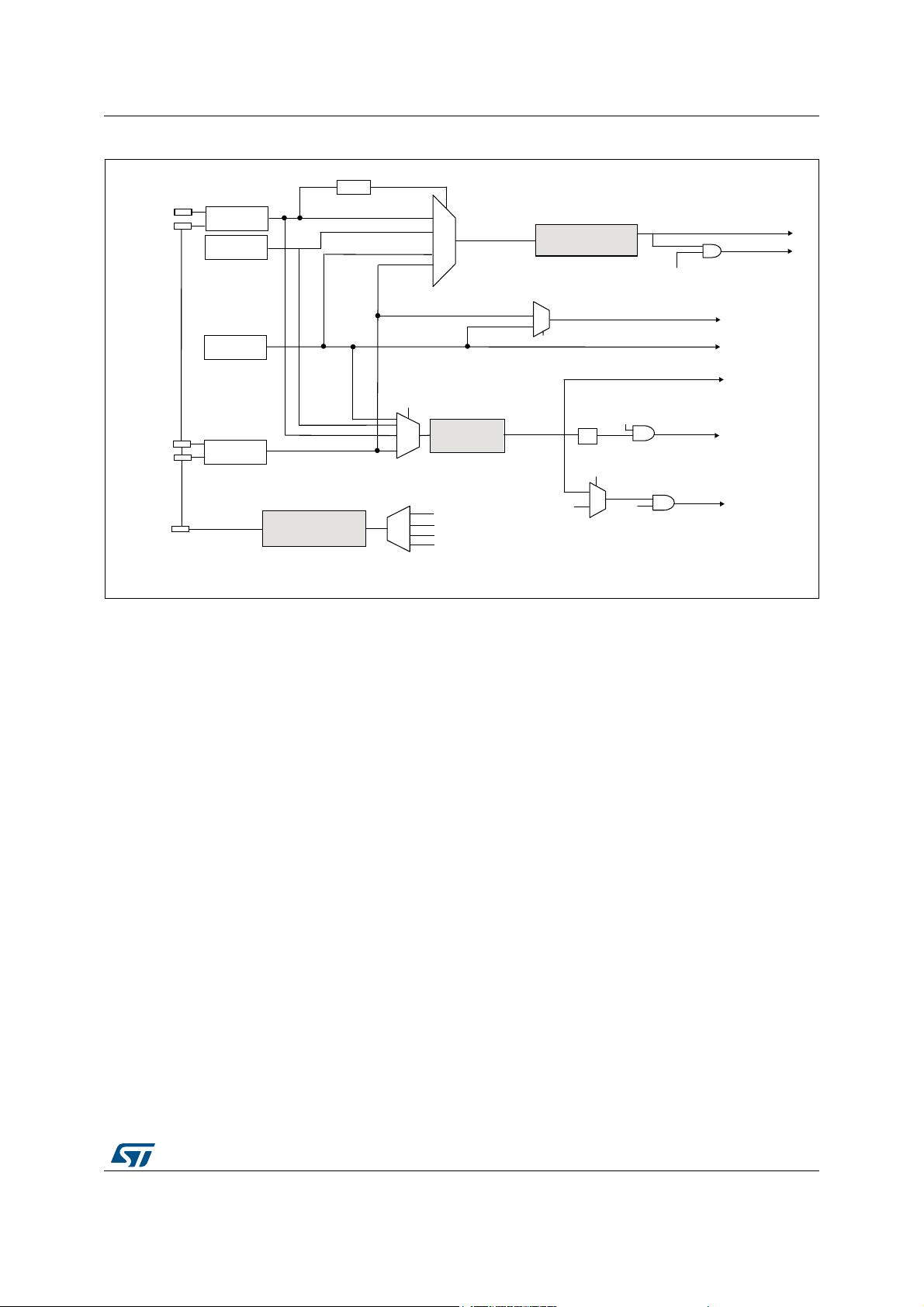

3.3 Reset and supply management

3.3.1 Power supply scheme

The device requires a 1.65 V to 3.6 V operating supply voltage (V

DD

). The external power

supply pins must be connected as follows:

• V

SS1

; V

DD1

= 1.8 to 3.6 V, down to 1.65 V at power down: external power supply for

I/Os and for the internal regulator. Provided externally through V

DD1

pins, the

corresponding ground pin is V

SS1

.

• V

SSA;

V

DDA

= 1.8 to 3.6 V, down to 1.65 V at power down: external power supplies for

analog peripherals (minimum voltage to be applied to V

DDA

is 1.8 V when the ADC1 is

used). V

DDA

and V

SSA

must be connected to V

DD1

and V

SS1

, respectively.

• V

SS2

; V

DD2

= 1.8 to 3.6 V, down to 1.65 V at power down: external power supplies for

I/Os. V

DD2

and V

SS2

must be connected to V

DD1

and V

SS1

, respectively.

• V

REF+

; V

REF-

(for ADC1): external reference voltage for ADC1. Must be provided

externally through V

REF+

and V

REF-

pin.

• V

REF+

(for DAC): external voltage reference for DAC must be provided externally

through V

REF+

.

3.3.2 Power supply supervisor

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset

(PDR), coupled with a brownout reset (BOR) circuitry. At power-on, BOR is always active,

and ensures proper operation starting from 1.8

V. After the 1.8 V BOR threshold is reached,

the option byte loading process starts, either to confirm or modify default thresholds, or to

disable BOR permanently (in which case, the V

DD

min value at power down is 1.65 V).

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To

reduce the power consumption in Halt mode, it is possible to automatically switch off the

internal reference voltage (and consequently the BOR) in Halt mode. The device remains

under reset when V

DD

is below a specified threshold, V

POR/PDR

or V

BOR

, without the need

for any external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the

V

DD

/V

DDA

power supply and compares it to the V

PVD

threshold. This PVD offers 7 different

levels between 1.85

V and 3.05 V, chosen by software, with a step around 200 mV. An

interrupt can be generated when V

DD

/V

DDA

drops below the V

PVD

threshold and/or when

V

DD

/V

DDA

is higher than the V

PVD

threshold. The interrupt service routine can then generate

a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

3.3.3 Voltage regulator

The medium-density STM8L151x4/6 and STM8L152x4/6 embeds an internal voltage

regulator for generating the 1.8 V power supply for the core and peripherals.

This regulator has two different modes:

• Main voltage regulator mode (MVR) for Run, Wait for interrupt (WFI) and Wait for event

(WFE) modes.

• Low power voltage regulator mode (LPVR) for Halt, Active-halt, Low power run and

Low power wait modes.

When entering Halt or Active-halt modes, the system automatically switches from the MVR

to the LPVR in order to reduce current consumption.