环路滤波器设计对芯片测试的影响及ADF4153应用

98 浏览量

更新于2024-08-30

收藏 282KB PDF 举报

"采用芯片测试的环路滤波器设计"

在现代无线通信系统中,小数分频频率合成器(Fractional-N frequency synthesizer)扮演着至关重要的角色,它可以生成精确且可调的射频(RF)信号。然而,为了确保这类芯片在实际应用中的性能,测试过程中必须构建一个完整的锁相环(Phase-Locked Loop, PLL)电路,这通常包括小数分频频率合成器、环路滤波器(Loop Filter, LF)和压控振荡器(Voltage-Controlled Oscillator, VCO)。本文重点探讨了在芯片测试中环路滤波器的设计方法,以提高测试的准确性和效率。

以ADI公司的ADF4153小数分频频率合成器为例,环路滤波器的设计对芯片性能测试的影响尤为关键。环路滤波器的设计不仅仅关系到相位噪声和杂散噪声的测量,还直接影响锁相环的锁定速度、稳态精度以及整体稳定性。在测试过程中,数字部分的性能可通过数字测试手段评估,但输出射频信号的质量,如相位噪声和杂散,必须在锁相环闭环状态下来测量。

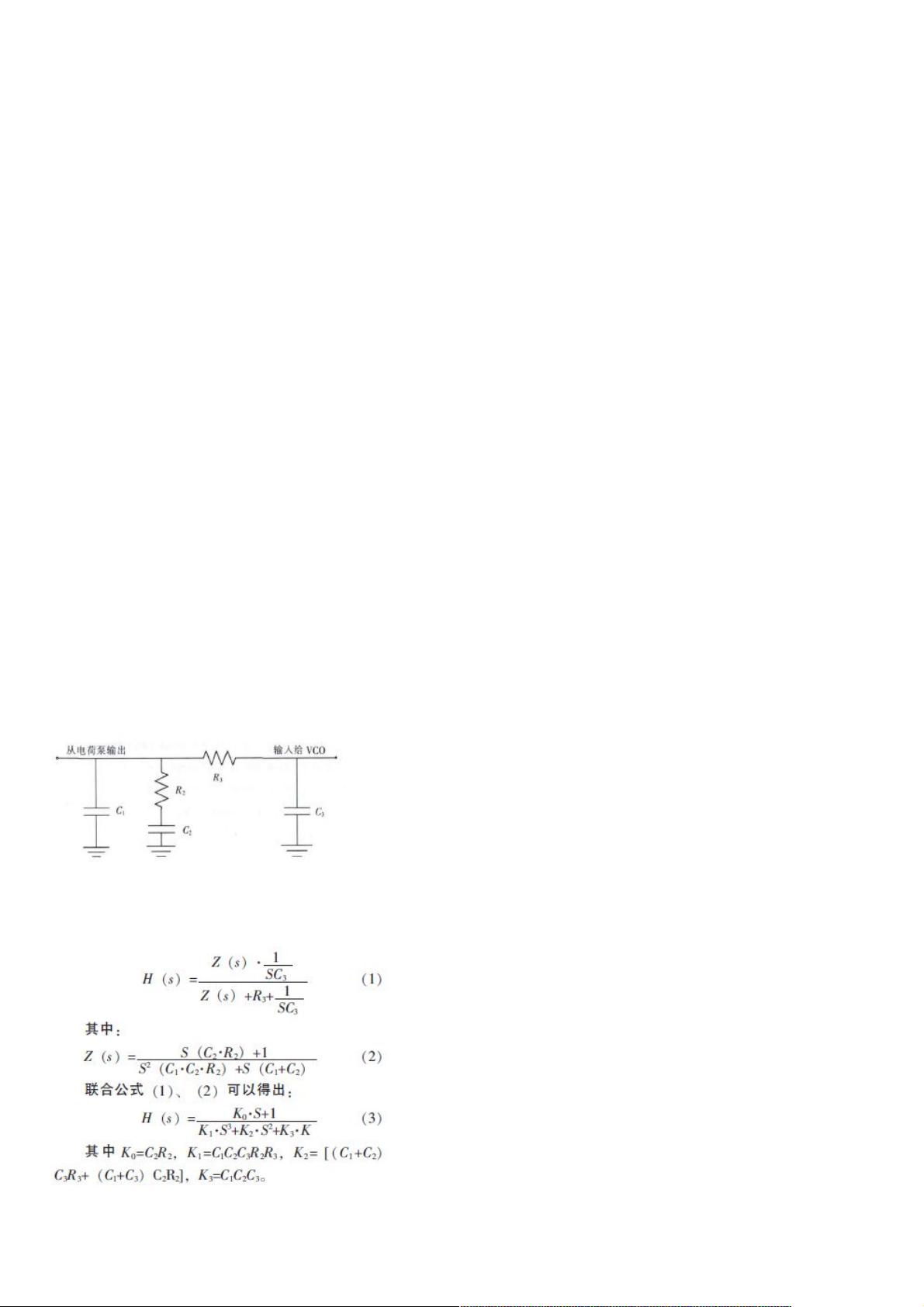

环路滤波器的设计过程包括确定其传递函数、选择合适的元件值以及考虑滤波器的阶数。通常,环路滤波器应设计为低通滤波器,它接收鉴相器输出的高频脉冲信号并过滤掉高频成分,留下一个平滑的直流电压,这个电压控制VCO的频率,进而调整锁相环的输出频率。环路滤波器的参数(如截止频率、带宽和稳定裕度)需与芯片的其他部分紧密匹配,以确保整个系统的最佳性能。

对于ADF4153,设计了一款三阶环路滤波器,该滤波器易于实现且能满足测试要求。三阶滤波器通常能提供足够的滚降率和良好的阻尼系数,从而保证锁相环的快速锁定和良好的相位噪声性能。在实际设计中,滤波器的电容和电感值需要通过模拟软件进行计算和优化,同时考虑到温度漂移和电源噪声的影响。

验证测试结果显示,所设计的环路滤波器成功地配合ADF4153芯片完成了测试,证明了这种方法的有效性。在设计环路滤波器时,除了关注滤波器的电气特性,还需要注意滤波器的物理布局,以减少寄生效应和减小噪声影响。

环路滤波器在小数分频频率合成器的测试中起着核心作用,它的设计直接影响到测试的准确性,也是优化整个锁相环系统性能的关键步骤。通过深入理解环路滤波器的工作原理和设计技巧,可以确保频率合成器芯片在各种应用场合下的性能表现。

2021-07-26 上传

2023-02-24 上传

2020-10-19 上传

2020-08-10 上传

点击了解资源详情

点击了解资源详情

2010-06-01 上传

2021-02-04 上传

2019-09-14 上传

weixin_38661939

- 粉丝: 5

- 资源: 949

最新资源

- 探索AVL树算法:以Faculdade Senac Porto Alegre实践为例

- 小学语文教学新工具:创新黑板设计解析

- Minecraft服务器管理新插件ServerForms发布

- MATLAB基因网络模型代码实现及开源分享

- 全方位技术项目源码合集:***报名系统

- Phalcon框架实战案例分析

- MATLAB与Python结合实现短期电力负荷预测的DAT300项目解析

- 市场营销教学专用查询装置设计方案

- 随身WiFi高通210 MS8909设备的Root引导文件破解攻略

- 实现服务器端级联:modella与leveldb适配器的应用

- Oracle Linux安装必备依赖包清单与步骤

- Shyer项目:寻找喜欢的聊天伙伴

- MEAN堆栈入门项目: postings-app

- 在线WPS办公功能全接触及应用示例

- 新型带储订盒订书机设计文档

- VB多媒体教学演示系统源代码及技术项目资源大全