VHDL语言实现全减器设计与EDA实验报告

"这篇实验报告主要介绍了如何使用VHDL语言设计一个一位二进制全减器,同时涉及了EDA(电子设计自动化)实验的基本流程和QuartusII软件的应用。实验者通过原理图输入法和文本输入法两种方式实现了全减器的设计,并通过真值表来验证其正确性。"

在数字逻辑设计中,全减器是一种基本的逻辑单元,它执行二进制减法运算,包括高位的借位。这个实验的主要目标是让学习者熟悉QuartusII软件,理解EDA设计流程,以及掌握VHDL语言的使用。

**实验目的**:

1. **熟悉QuartusII软件**:QuartusII是一款常用的EDA工具,用于Altera FPGA和CPLD的设计、仿真和编程。实验者需要了解其各个模块的功能,如项目管理、逻辑编译、仿真等。

2. **掌握EDA设计流程**:包括设计输入、逻辑综合、布局布线、仿真验证和硬件实现等步骤。

3. **复习组合电路设计**:全减器是组合逻辑电路的一种,实验者需要运用已有的知识来设计和分析。

4. **系统仿真与硬件测试**:通过软件仿真验证设计的正确性,并学会分析硬件测试结果。

**设计原理**:

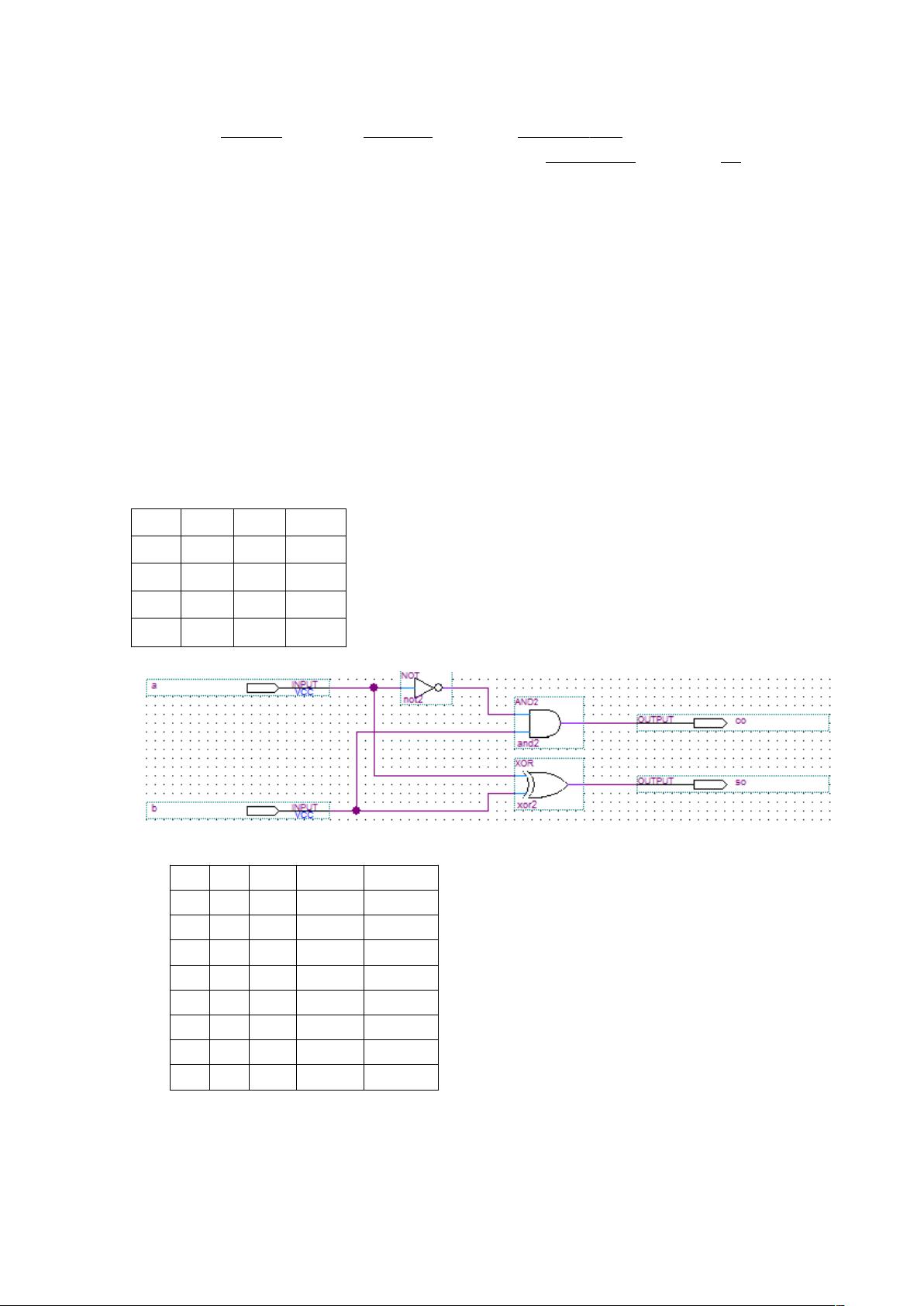

1. **原理图输入法**:全减器由两个半减器和一个或门连接而成。半减器处理两个输入位的减法,而全减器则需要处理低位的借位信号。实验者绘制了半减器和全减器的真值表,然后依据这些表构建了相应的电路原理图。

2. **文本输入法**:使用VHDL语言编写代码来描述全减器的行为。这里,`ENTITY`定义了一个名为`f_suber2`的全减器,有四个输入(a, b, c)和两个输出(F, co)。`ARCHITECTURE`部分定义了逻辑结构,使用`PROCESS`和`CASE`语句根据输入的不同组合来设定输出。

VHDL代码的关键部分如下:

```vhdl

PROCESS(abc)

BEGIN

CASE abc IS

WHEN "000" => F <= '0'; co <= '0';

WHEN "010" => F <= '1'; co <= '1';

...

END CASE;

END PROCESS;

```

这段代码描述了当输入`abc`的所有可能情况时,输出`F`和`co`应如何设置。通过这种方式,VHDL能精确地描述全减器的逻辑功能。

实验要求学生同时使用这两种方法实现全减器,这有助于加深他们对硬件描述语言和逻辑设计的理解,同时也提高了他们的动手能力。通过这样的实验,学生可以更好地准备未来更复杂的数字系统设计。

3811 浏览量

1362 浏览量

4015 浏览量

368 浏览量

109 浏览量

314 浏览量

4852 浏览量

点击了解资源详情

玄墨书生

- 粉丝: 0

最新资源

- 施耐德Twido PLC密码解密软件介绍

- VB.NET自动生成属性插件更新及源码下载

- Jane Quintos演示C#项目 COMP397-W2021-Lesson9a

- 掌握iPhone 3开发:基础教程SDK3.0源码解析

- 掌握108个JavaScript网页特效,打造酷炫页面体验

- QuickReport 2010在Delphi中的Unicode支持与安装

- 详解Tomcat9.0配置服务器包的安装与优化

- 实现自定义标签,有效防止表单重复提交

- AcronisPartitionExpert: 数据安全的硬盘分区管理软件

- Koha插件系统介绍:自动打印保全单功能插件

- C#实现贪吃蛇游戏:自定义颜色与速度

- httpClient与jsoup整合教程:HTTP客户端编程实践

- SpringMVC集成Activiti5.21流程引擎所需jar包介绍

- CY3253 BLDC电机反电势滤波法及其噪声抑制优化

- ASP/VBS/正则表达式/WSH脚本全攻略

- Python实现突触变化跟踪的神经网络模型