使用Cadence Virtuoso设计ASAP 7nm FinFET反相器教程

需积分: 40 18 浏览量

更新于2024-08-05

7

收藏 817KB PDF 举报

"本教程详细介绍了如何使用Cadence Virtuoso进行大规模集成电路设计,特别是基于ASAP 7纳米工艺的原理图设计。课程内容涵盖环境配置、Virtuoso软件的启动、原理图编辑器的使用,以及利用ASAP7 7纳米预测性工艺库构建FinFET反相器。"

在本教程中,我们将学习使用Cadence Virtuoso进行高级半导体工艺(ASAP 7nm)原理图设计的方法。首先,我们需要确保正确配置工作环境。在启动Virtuoso之前,确保你位于`asap7_rundir`目录下,并执行两个关键命令:

1. `$ source tcshrc_cadence`

2. `$ source set_pdk_path.csh`

这两个命令用于设置必要的环境变量,以便Virtuoso能够识别和使用ASAP7工艺开发套件(PDK)。接下来,通过运行`$ virtuoso&`启动Cadence Virtuoso软件。

设计一个基于FinFET的反相器是理解Virtuoso环境和ASAP7 PDK的关键步骤。尽管这个PDK已经预装了一个示例反相器,但我们将自己构建一个,以便更深入地了解该平台。设计FinFET反相器的过程与使用FreePDK45的反相器设计类似,但有一些关键区别,尤其是在处理FinFET结构和运行模拟时。

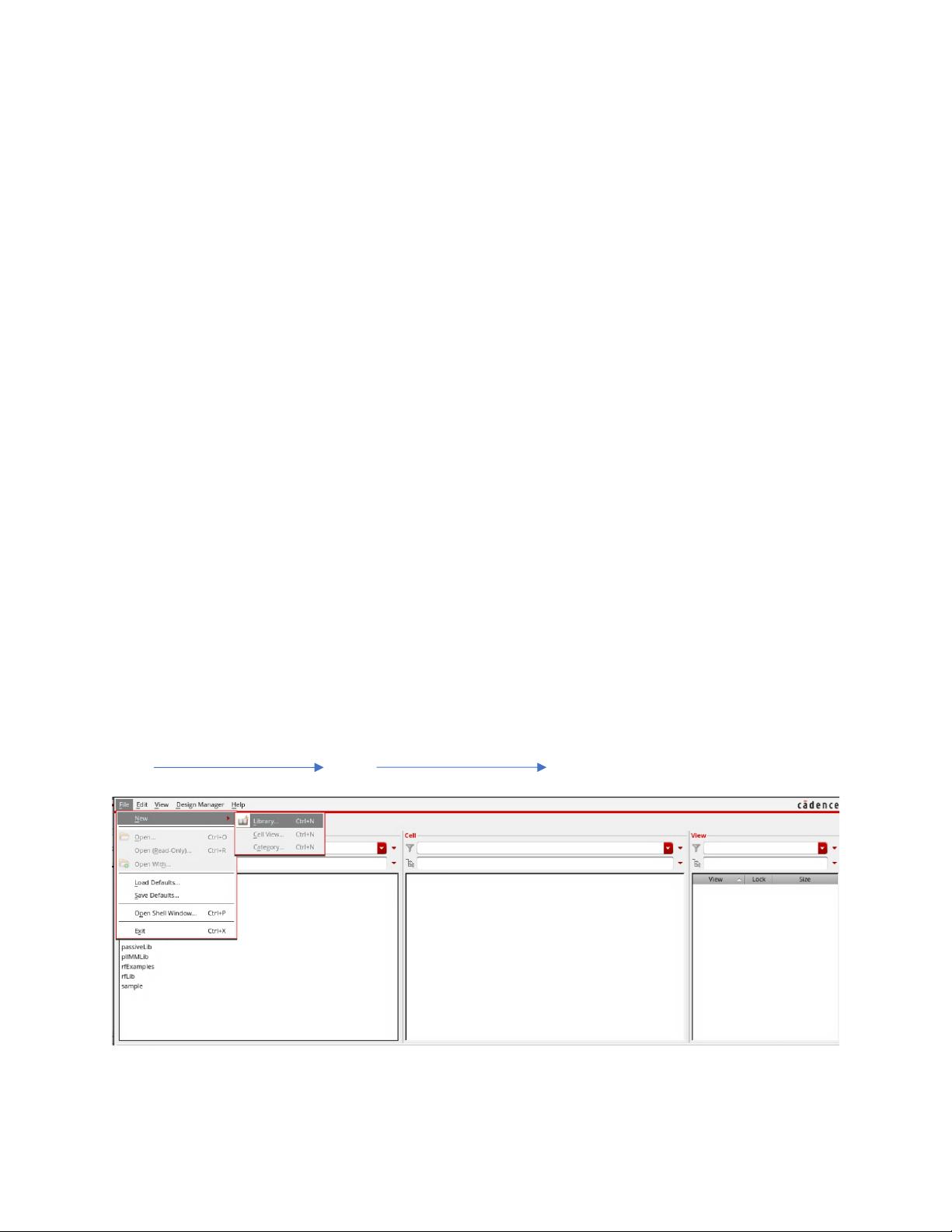

在Virtuoso中创建新的设计库:

1. 打开“Library Manager”窗口。

2. 选择“File”菜单,然后点击“New Library”。

3. 给新库命名,例如“test”。

4. 选择“Attach to an existing technology library”选项。

5. 在弹出窗口中,选择“asap7_Tech”作为技术库,这将使你的设计与ASAP 7nm工艺兼容。

一旦库创建完成,你可以开始设计反相器。在Virtuoso Schematic Editor中,添加ASAP7 PDK提供的FinFET元件,根据工艺特性连接它们,以实现反相功能。设计完成后,必须进行布局和布线,以优化性能和功耗。

在设计验证阶段,我们将利用HSPICE仿真器与Virtuoso的集成。与FreePDK45中的过程相比,使用ASAP7 PDK进行模拟会有显著的不同,因为7纳米工艺涉及到更复杂的物理效应和更精细的参数控制。你需要定义合适的仿真设置,包括输入激励、电压范围、温度条件等,以评估反相器的性能指标,如阈值电压、传播延迟和功耗。

这个教程为学习者提供了在Cadence Virtuoso环境中使用ASAP 7nm工艺进行数字电路设计的基础。通过实际操作,你将掌握如何创建和管理设计库,利用FinFET结构构建电路,以及如何进行高性能模拟,这些都是现代集成电路设计中的核心技能。

2012-06-28 上传

点击了解资源详情

2023-06-12 上传

162 浏览量

106 浏览量

2021-07-10 上传

2023-11-10 上传

qq_21558683

- 粉丝: 0

- 资源: 2

最新资源

- 构建基于Django和Stripe的SaaS应用教程

- Symfony2框架打造的RESTful问答系统icare-server

- 蓝桥杯Python试题解析与答案题库

- Go语言实现NWA到WAV文件格式转换工具

- 基于Django的医患管理系统应用

- Jenkins工作流插件开发指南:支持Workflow Python模块

- Java红酒网站项目源码解析与系统开源介绍

- Underworld Exporter资产定义文件详解

- Java版Crash Bandicoot资源库:逆向工程与源码分享

- Spring Boot Starter 自动IP计数功能实现指南

- 我的世界牛顿物理学模组深入解析

- STM32单片机工程创建详解与模板应用

- GDG堪萨斯城代码实验室:离子与火力基地示例应用

- Android Capstone项目:实现Potlatch服务器与OAuth2.0认证

- Cbit类:简化计算封装与异步任务处理

- Java8兼容的FullContact API Java客户端库介绍