高速数字电路设计:终端与始端匹配详解及阻抗校准策略

需积分: 14 192 浏览量

更新于2024-08-01

收藏 347KB PDF 举报

高速数字电路设计教材深入探讨了高速数字电路中的关键概念和技术,特别是针对阻抗匹配问题。该教材详细地讲解了以下几个关键部分:

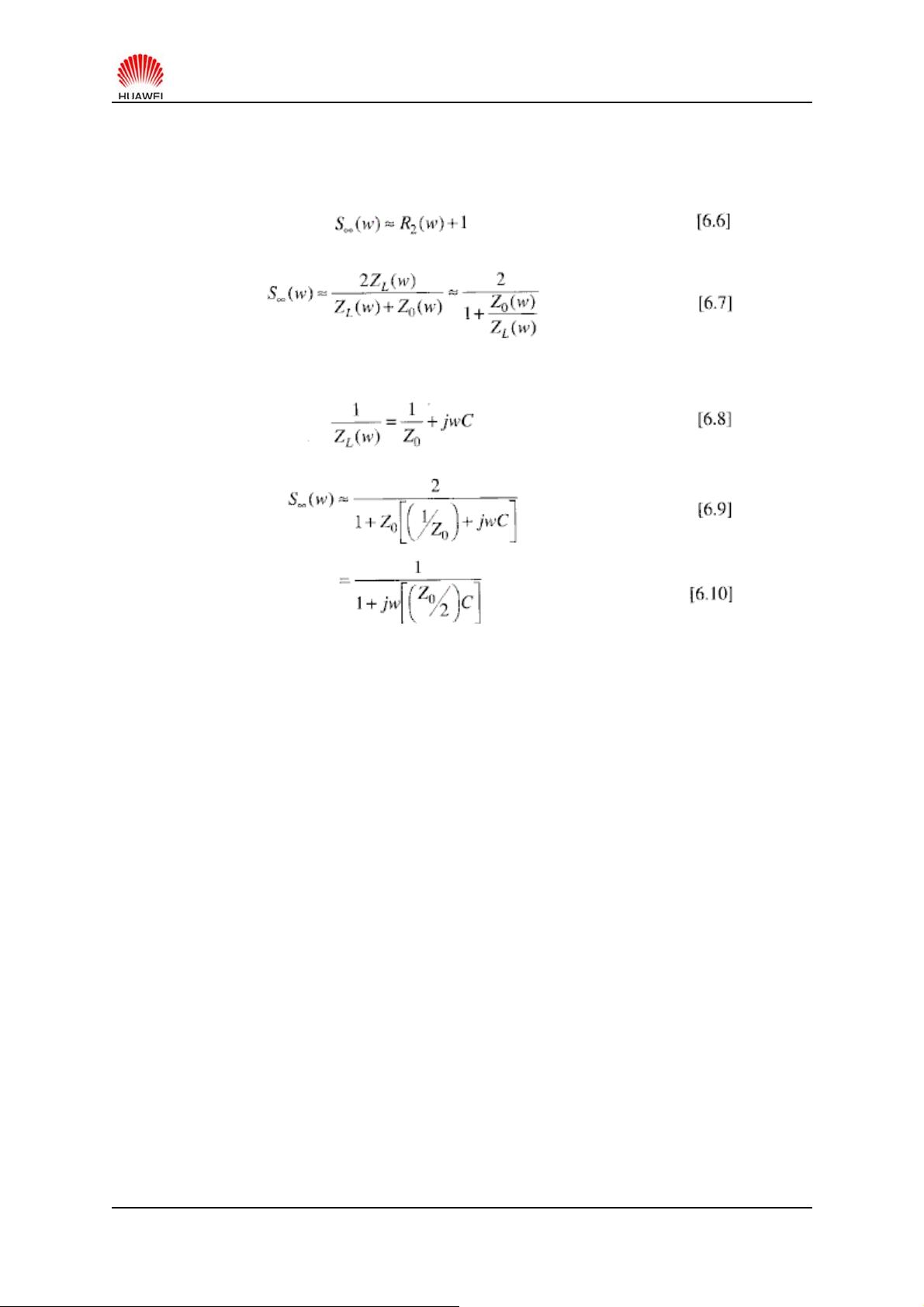

1. 阻抗匹配的重要性:章节6.1至6.6围绕终端匹配和始端匹配展开,这是为了确保信号在长线传输中能有效传播,避免信号反射和振荡。终端匹配是指信号源与传输线直接连接,而始端匹配则在信号源前添加匹配电阻以改善信号质量。

2. 串扰分析:教材特别关注电阻间的串扰,包括排阻间的串扰(6.6.3)、相邻贴片电阻间的串扰(6.6.2)以及相邻轴向电阻间的串扰(6.6.1)。这些内容旨在减少不同元件之间的电磁干扰,提高信号完整性。

3. 匹配电阻特性:6.5节着重讨论匹配电阻的特性,如电感(6.5.3)、功率消耗(6.5.2),以及精确度(6.5.1)。电阻值的选择至关重要,因为不同的阻值会直接影响信号传输的效率和失真。

4. 差分线和终端匹配:章节6.4介绍了差分线的终端匹配方法,包括处理直流不平衡性(6.4.1)和输出驱动电流的考虑(6.4.2),这些都是实现低噪声、高带宽传输的关键。

5. 匹配电路的设计与计算:教材提供了确定匹配电阻的方法,例如通过数学模型来估算反射持续时间(4.3.5节),这对于实际设计中的精确计算十分实用。

6. 匹配器件间的影响:教材强调了匹配器件之间的串扰控制,这是确保整体电路性能的重要环节,尤其是在多层板设计中。

总结来说,高速数字电路设计教材提供了一个全面的框架,涵盖了从理论到实践的阻抗匹配方法,帮助读者理解和解决高速电路中常见的信号传输问题,提高信号传输的稳定性和有效性。

288 浏览量

118 浏览量

点击了解资源详情

2178 浏览量

288 浏览量

143 浏览量

143 浏览量

wzh821

- 粉丝: 1

最新资源

- C#实现程序A的监控启动机制

- Delphi与C#交互加密解密技术实现与源码分析

- 高效财务发票管理软件

- VC6.0编程实现删除磁盘空白文件夹工具

- w5x00-master.zip压缩包解析:W5200/W5500系列Linux驱动程序

- 数字通信经典教材第五版及其答案分享

- Extjs多表头设计与实现技巧

- VBA压缩包子技术未来展望

- 精选多类型导航菜单,总有您钟爱的一款

- 局域网聊天新途径:Android平台UDP技术实现

- 深入浅出神经网络模式识别与实践教程

- Junit测试实例分享:纯Java与SSH框架案例

- jquery xslider插件实现图片的流畅自动及按钮控制滚动

- MVC架构下的图书馆管理系统开发指南

- 里昂理工学院RecruteSup项目:第5年实践与Java技术整合

- iOS 13.2真机调试包使用指南及安装