探索综合与Design Compiler:从逻辑到门级设计的关键步骤

需积分: 50 59 浏览量

更新于2024-07-20

收藏 3.62MB PDF 举报

综合与Design Compiler是集成电路设计过程中至关重要的环节,它涉及将行为描述的电路从高级语言抽象级别转换到实际的物理实现。Design Compiler是Synopsys公司提供的一款核心电路综合工具,专用于处理高级硬件描述语言(HDL)如VHDL或Verilog,将这些描述转换成基于工艺库的门级网表。

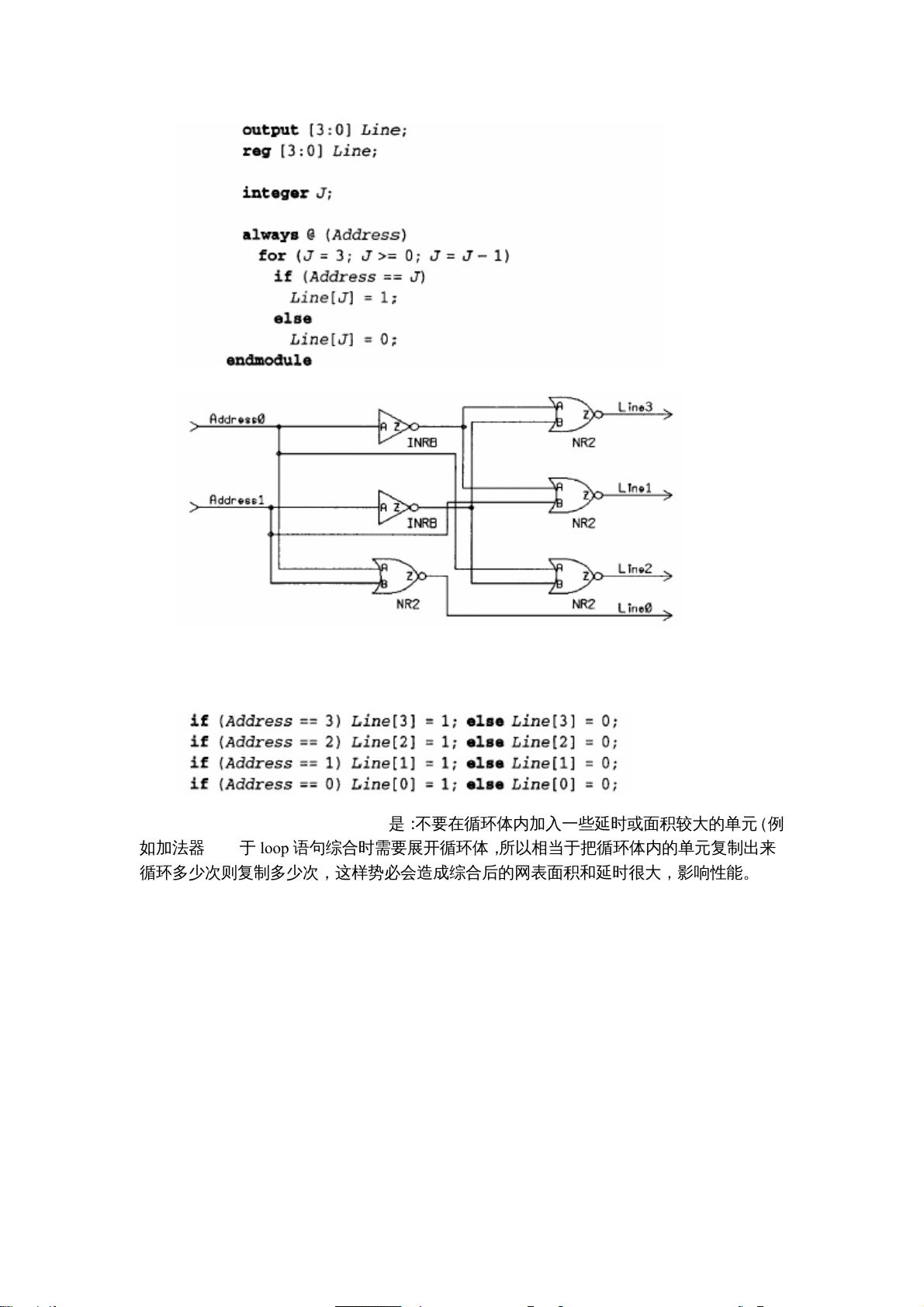

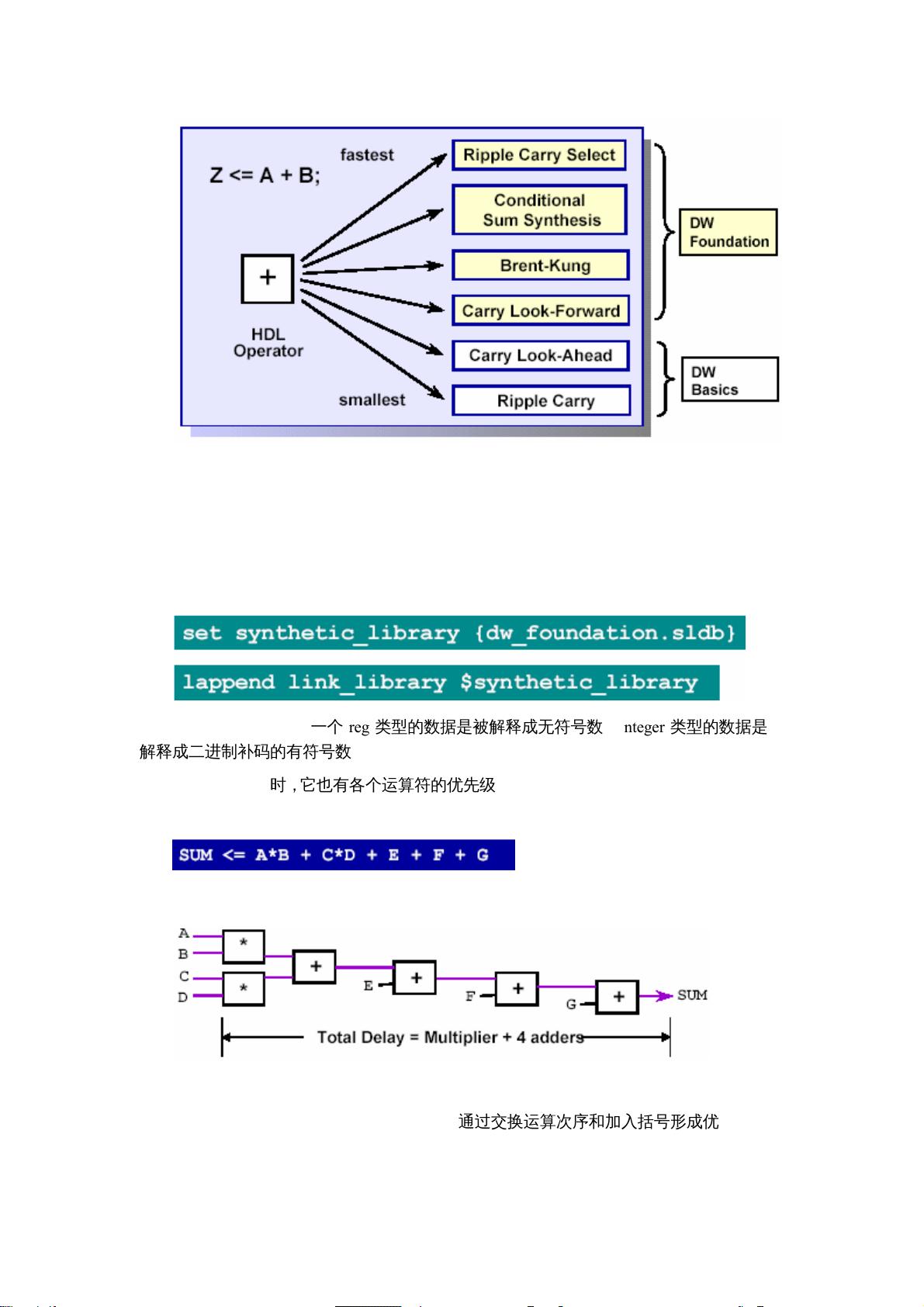

综合的主要过程包括三个阶段:转换、映射和优化。转换阶段将HDL描述转换为工艺无关的RTL级网表,即在这一阶段,设计师的逻辑被抽象为由信号流和逻辑门构成的基本单元。映射阶段则依据特定的工艺库将RTL网表映射到实际的电路布局,确保电路的物理实现符合工艺要求。最后,优化阶段考虑设计约束,如延迟和面积优化,对门级网表进行改进,以达到最佳性能和效率。

逻辑级综合是最早期的形式,设计者使用布尔代数表达式描述逻辑功能,并通过元件实例化(例如,使用触发器或锁存器)来构造电路。例如,一个加法器在逻辑级的描述可能包含一系列的逻辑操作符,这在综合后直接反映在电路结构中。图3展示了逻辑级综合后的电路网表,可以看出原始设计的逻辑结构已经清晰可见。

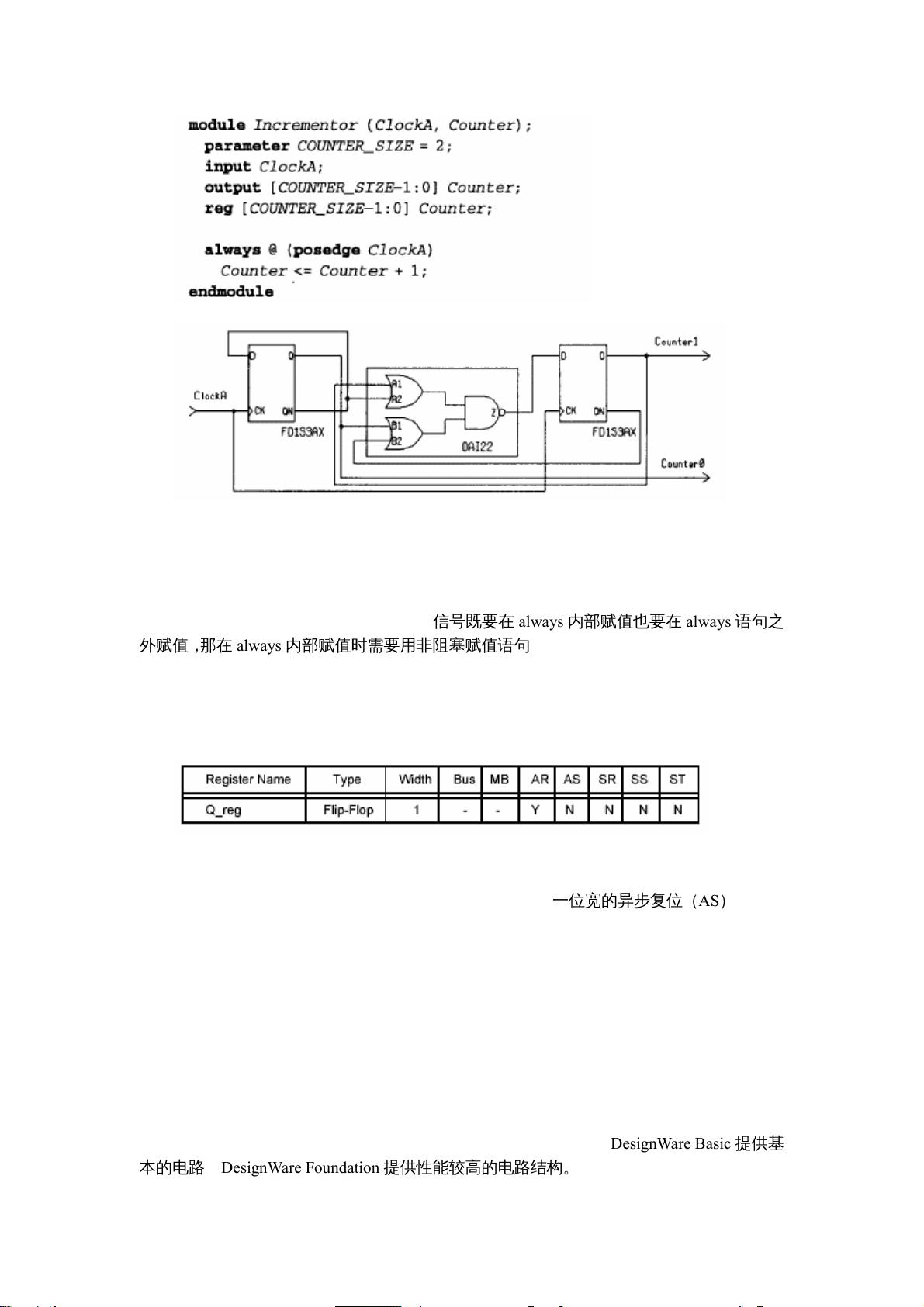

相比之下,RTL级综合更进一步,利用HDL语言的特性,如算术运算符和流程控制语句,来表达电路的数学运算和行为功能。这种方法提供了更高层次的抽象,使得设计者对电路的控制更为细致。

综合的层次不同,设计师的控制程度也不同。逻辑级和RTL级综合允许设计者对电路细节有较多控制,而行为级综合则更多依赖于综合工具的自动优化,减少了设计者的直接干预。综合的目标是在满足功能、速度和面积等要求的前提下,找到最优的电路实现策略。

Design Compiler在集成电路设计中扮演着关键角色,通过逻辑综合将抽象的HDL描述转化为可制造的门级电路,整个过程涉及到多个精细的步骤和不同的抽象层次,以适应设计师的各种需求。理解并熟练掌握这个工具,对于电路设计人员来说至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-01-09 上传

2023-10-23 上传

2021-02-23 上传

2016-04-27 上传

2024-03-04 上传

137 浏览量

HaaaaFra

- 粉丝: 0

- 资源: 3

最新资源

- 基于Python和Opencv的车牌识别系统实现

- 我的代码小部件库:统计、MySQL操作与树结构功能

- React初学者入门指南:快速构建并部署你的第一个应用

- Oddish:夜潜CSGO皮肤,智能爬虫技术解析

- 利用REST HaProxy实现haproxy.cfg配置的HTTP接口化

- LeetCode用例构造实践:CMake和GoogleTest的应用

- 快速搭建vulhub靶场:简化docker-compose与vulhub-master下载

- 天秤座术语表:glossariolibras项目安装与使用指南

- 从Vercel到Firebase的全栈Amazon克隆项目指南

- ANU PK大楼Studio 1的3D声效和Ambisonic技术体验

- C#实现的鼠标事件功能演示

- 掌握DP-10:LeetCode超级掉蛋与爆破气球

- C与SDL开发的游戏如何编译至WebAssembly平台

- CastorDOC开源应用程序:文档管理功能与Alfresco集成

- LeetCode用例构造与计算机科学基础:数据结构与设计模式

- 通过travis-nightly-builder实现自动化API与Rake任务构建