时序逻辑电路设计:从触发器到有限状态机

"本资源主要介绍了时序逻辑电路设计,包括基本D触发器、JK触发器、T触发器、计数器(如基本计数器、同步清零计数器、可逆计数器、进制计数器)、移位寄存器(如基本移位寄存器、预置数串行输出移位寄存器、循环移位寄存器、双向移位寄存器)以及有限状态机的设计。此外,还提到了时序逻辑电路设计中时钟信号的重要性,以及VHDL中描述时钟信号的两种方法。"

时序逻辑电路设计是数字系统设计中的关键部分,它允许电路记住其先前的状态,并根据当前输入和这些状态来产生输出。这种记忆功能主要由触发器实现,例如D触发器、JK触发器和T触发器。D触发器是最基础的类型,它的输出在时钟边沿处更新为输入D的值,无反馈路径,因此具有稳定的存储能力。JK触发器则提供了更灵活的转换规则,J和K输入可以控制触发器在时钟脉冲到来时翻转或保持状态。

在计数器设计中,有多种类型的计数器,如基本计数器、同步清零计数器、同步预置数计数器等,它们可以实现递增或递减计数,或者按照特定的进制进行计数。计数器在数字系统中广泛用于定时和计数任务,例如在计算机的时钟系统、计数器和频率分频器中。

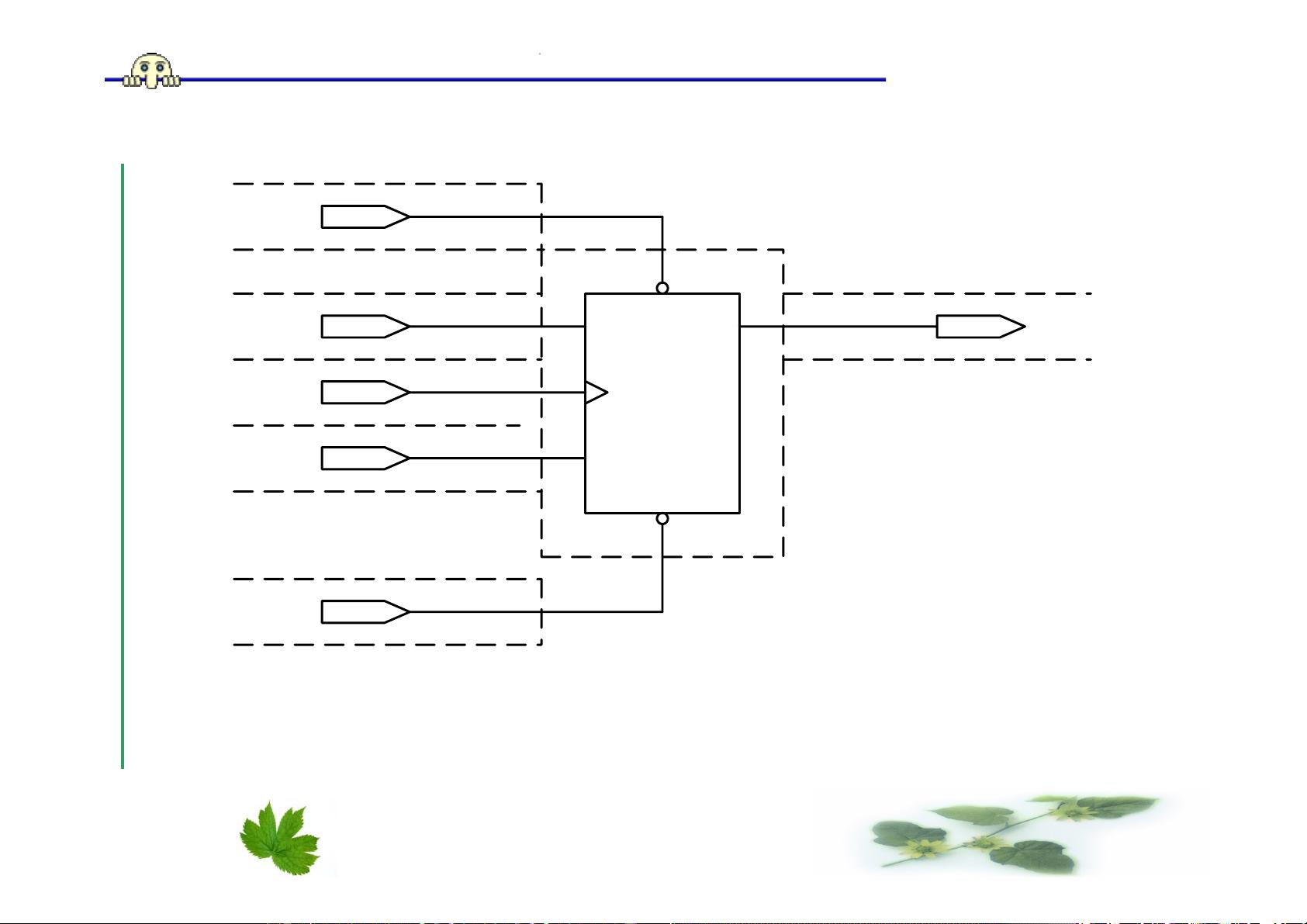

移位寄存器则是一种能够存储数据并按顺序移动数据位的电路。基本移位寄存器可以进行左移或右移操作,而预置数串行输出移位寄存器允许在指定位置加载数据,循环移位寄存器则可以实现数据的循环移位。移位寄存器在数据处理和通信系统中起到重要作用,例如在串行到并行转换和移位操作中。

此外,时序逻辑电路设计还涉及有限状态机(FSM),它是一种状态转换系统,可以根据输入序列和当前状态来确定下一个状态。FSM在许多数字系统中都有应用,如微控制器、处理器指令解码和自动贩卖机等控制系统。

时序逻辑电路设计的关键在于时钟信号的处理。在VHDL编程中,时钟通常通过进程的敏感列表或WAIT语句来描述。时钟的上升沿或下降沿常常作为触发事件,决定何时更新电路状态。例如,当使用"clk='1' AND clk'event"这样的条件时,表明只有在时钟信号的上升沿时,进程才会执行。

时序逻辑电路设计涵盖了多种核心组件和设计原则,对于理解和设计数字系统至关重要,特别是在嵌入式系统、微电子和计算机硬件领域。理解并掌握这些知识点对于任何IT专业人员来说都是必要的,因为它们构成了现代数字设备的基础。

293 浏览量

330 浏览量

202 浏览量

190 浏览量

197 浏览量

172 浏览量

2024-08-15 上传

coollee2009

- 粉丝: 0

- 资源: 2

最新资源

- Task1_2sem

- hivestu.zip

- Mall4j商城系统mall4j-master

- 开发区管委办2013年工作总结及2014年工作思路

- BBSNetworkSystemExample:BBSNetworkSystem的示例

- AirBnB_clone

- 智睿录取查询报名系统源码下载 v3.0.0

- dotfiles:我的点文件

- java编写的游戏服务器.zip

- 滚齿机速查挂轮软件2.1版本.zip

- DataMinig-in-Recruitment:#data #datascience #rapidminer #dataminig

- 测试2

- android演示手动切换语言的DEMO

- SimpleFormBuilder:这是一个简单的表单构建器

- copy-to-clipboard

- 关于机关软件正版化督导检查工作总结