Verilog实现8位寄存器设计与仿真

需积分: 0 144 浏览量

更新于2024-08-04

1

收藏 150KB DOCX 举报

"实验2-寄存器设计1"

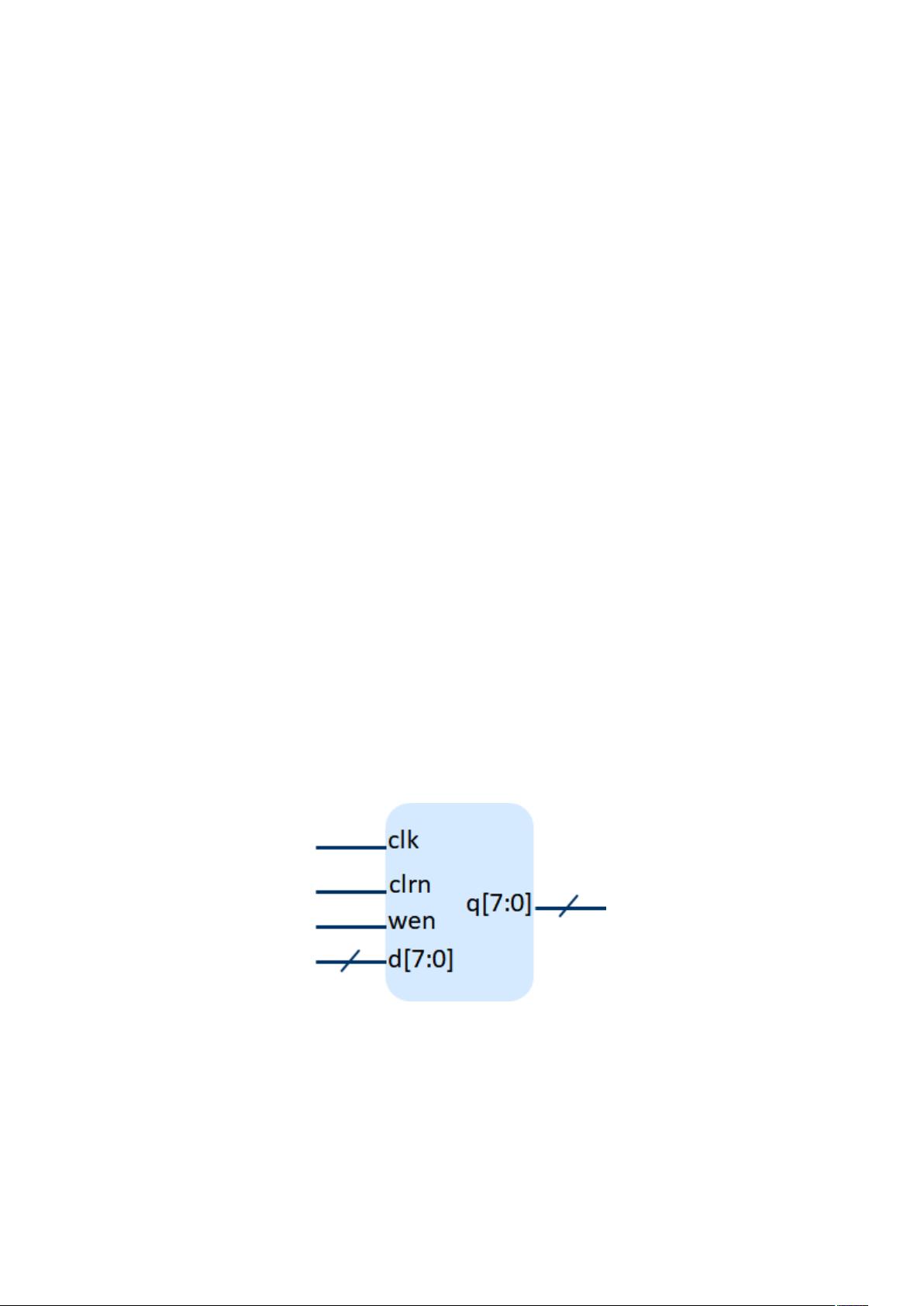

在本次实验中,主要目标是通过Verilog硬件描述语言设计和实现一个8位寄存器,该寄存器具有异步清零(clrn)和同步使能(wen)功能。实验旨在帮助学生熟悉Verilog语言在描述时序逻辑电路中的应用,掌握约束文件和仿真文件的编写,以及深入理解寄存器的工作原理。

实验的具体任务是设计一个8位寄存器reg8,它由8个D触发器组成,每个D触发器负责存储一位数据。D触发器是一种基本的时序逻辑单元,它在时钟边沿触发时,将数据输入(D)的值复制到输出(Q),除非存在清零或使能信号的影响。在本例中,D触发器具有异步清零功能,意味着当clrn信号为低电平时,无论时钟状态如何,寄存器都会被清零。同步使能wen则控制数据是否能够写入寄存器:wen为高电平时,数据不会改变;wen为低电平时,数据会在时钟上升沿更新。

设计流程包括首先编写单个D触发器(dffe.v)的Verilog代码,然后在主模块reg8.v中通过实例化8个dffe模块来构建8位寄存器。在reg8.v模块中,需要连接输入数据(d),输出数据(q),时钟(clk),清零(clrn)和写使能(wen)信号。在dffe.v中,根据图1-2的功能表,确保D触发器在clrn为低时清零,在wen为低且时钟上升沿时更新Q值。

为了验证设计的正确性,需要编写仿真文件reg8_sim.v。这个文件包含了一个测试平台,模拟了各种操作条件,如复位、跟随和保持。在给定的框架代码中,时钟(clk)、清零(clrn)和写使能(wen)被初始化,并设置了不同的测试序列。例如,`#10 clk=~clk`用来模拟时钟的翻转,而`#25 begin clrn=1'b0;wen=1'b0;end`则模拟了复位操作。仿真结果会展示在波形图上,如图1-4所示,通过观察波形可以判断设计是否符合预期。

此外,实验还需要一个约束文件reg8.xdc,用于指定硬件实现时的管脚分配。表1-1列出了reg8的管脚分配,学生需要根据实际开发板的资源和接口来完成约束文件的编写。

通过这个实验,学生不仅能够掌握Verilog语言的基本用法,还能学习到如何将基础逻辑单元组合成更复杂的数字系统,并通过硬件仿真验证其正确性,这对于理解和设计数字集成电路至关重要。

点击了解资源详情

704 浏览量

点击了解资源详情

177 浏览量

4967 浏览量

149 浏览量

202 浏览量

124 浏览量

吹狗螺的简柏承

- 粉丝: 21

最新资源

- HTC G22刷机教程:掌握底包刷入及第三方ROM安装

- JAVA天天动听1.4版:证书加持的移动音乐播放器

- 掌握Swift开发:实现Keynote魔术移动动画效果

- VB+ACCESS音像管理系统源代码及系统操作教程

- Android Nanodegree项目6:Sunshine-Wear应用开发

- Gson解析json与网络图片加载实践教程

- 虚拟机清理神器vmclean软件:解决安装失败难题

- React打造MyHome-Web:公寓管理Web应用

- LVD 2006/95/EC指令及其应用指南解析

- PHP+MYSQL技术构建的完整门户网站源码

- 轻松编程:12864液晶取模工具使用指南

- 南邮离散数学实验源码分享与学习心得

- qq空间触屏版网站模板:跨平台技术项目源码大全

- Twitter-Contest-Bot:自动化参加推文竞赛的Java机器人

- 快速上手SpringBoot后端开发环境搭建指南

- C#项目中生成Font Awesome Unicode的代码仓库