In order to ensure normal teaching order, protecting students ' healthy growth, ensuring that national (property) is not lost, to prevent or minimize the occurrence of safety accidents, follow the "prevent, rescue each other, ensure safety and reduce losses" principle, according to the local conditions, make the management system. 1, the principal is the responsibility of school safety, school security under the leadership of President security work leading group. The head teacher to the leadership team is responsible for, implementation of the accountability system. 2, school monthly student knowledge about safety education, education should be diversified in the form every safety education for students of classes per week should be targeted. To carry on emergency issues dealing with education in General, self-help and mutual rescue knowledge. Emergency calls (such as 110, 119, 122, 120, and so on) use common sense in education. 3, the establishment of major accident reporting system.

School students report major accident within an hour of education; student run and disappearances to report; report of the accident to a written report in triplicate, a correctional centre, a police station, a township people's Government shall not conceal the accident. 4 week, teachers are on duty system, establish and improve the leadership values; strengthen the education, management of teaching activities in schools to ensure normal teaching order; responsible for school safety leadership always maintained close contact and district police stations, canvassing support from the police station on school safety and help. 5, strengthening teachers ' moral education, establish a dedicated love, improving education quality, observe the students ' psychological changes at any time and take preventive measures, no corporal punishment and covert corporal punishment on students, student out of the classroom, schools may not be. 6, units or departments use student Street propaganda or

participate in the celebrations, as well as participating in other social work, without approval of the Correctional Centre, school principals consent, without organization. Without the approval of relevant departments, may organize students to participate in fire fighting, disaster relief and so on. 7, schools should educate students to obey the school rules and regulations, on time, on time home to prevent accidents. 8, school to school inspections on a regular basis, found hidden in time, and in severe cases, it is hard to eliminate immediately closed, and reported to the local people's Government, education, and rule of law section. 9, the school should always check the internal walls, retaining walls, ponds, railings, handrails, doors, Windows, staircases and a variety of sports, extracurricular activities, facilities such as fire safety, infrastructure security, unsafe facility to immediately repair and demolition to ensure that teachers and students work, learn, live venues and facilities are safe and

reliable. Song Lin Xiang Liu Jia ping elementary school March 2016 song Lin Xiang Liu Jia ping primary school fire safety systems to enhance fire safety, protection of public property and the life and property safety of teachers and students, school fire safety into day-to-day management, is developing the following fire safety system. 1, strengthen fire safety education of the whole school. According to the requirements of the Fire Services Act, so that everyone has of keeping fire control safety, protecting fire control facilities, fire prevention, reports of fire

为进一步加强和改进干部作风,严肃工作纪律,提高工作效能,更好地服务群众、服务企业、服务发展,树立“为民、务实、清廉”的良好形象提振干部队伍精气神,按照县委要求,利用一个月时间

Electricity lines, equipment inspections, found hidden in time for rectification, maintenance, and security. 9, do not use an open flame in the classroom, prohibit burning stove, lit candles, mosquito repellent, no smoking, and banning messy wiring. Without using any household appliances is not allowed. 10, live on campus faculty members, must lead by example, and educate families and children ready to fire. 11, household use of gas in schools, to master proper usage, pay attention to the leak-proof, explosion-proof, fireproof, closing valve after use to ensure security. 12, dining room must be qualified, and annual testing of pressure vessels, to regularly check, the canteen workers must be certified, strictly by operation operation, gas tank and stove safety distance of 1.5 meters, to prevent accidents. 13, the adverse consequences caused by ignoring fire safety regulations, will be punished, until investigated for legal responsibility. Song Lin Xiang Liu Jia ping elementary school March 2016 Xiang

Liu Jia ping elementary school, pine slopes surrounding safety management system 1 teachers and students, the surrounding area of the school governance covers personal and food hygiene, cultural events and other aspects, integrated governance shall obtain wide support and full cooperation of the community. On the surrounding environment in schools should be closely monitored. 2, school work at the same time, should pay attention to the safety management of school environment, should take the initiative to contact the district police station, the village Committee, Correctional Centre, Township government, business management and other departments to do a good job management. 3, teacher on duty with the exception of inspections in schools, should also pay attention to environmental inspections near the campus, found that the jobless migrants from rural areas, for example, harassment of students and a variety of accidents, according to different situations reported school

officials or the police station in a timely manner, to protect the safety of students. 4, every day before school, teachers remind students, pay attention to traffic safety. 5, should educate students to respect social ethics, and various regulations, maintaining public order, and fight the bad guys, and grasp the correct ways and means of maintaining and improving students ' self-care ability. 6, the establishment of emergency rescue teams of teachers in schools, on high alert and deployed. Song Lin Xiang Liu Jia ping elementary school March 2016 song Lin Xiang Liu Jia ping primary school teachers and students organizations out of safety management system organization activities between teachers and students, to draw up a precise plan and security measures must be signed by the school officials to review the programme of activities agreed upon Correctional Center agreed to implement. Organization to the field relatively far or activities require approval by the Deputy Director of the

Education Bureau in charge of security. 2, each activity should have a specific responsibility, pay attention to the persons age, physical match. Route 3, activities, location, field surveys should be carried out in advance. 4, activities for the means of transport should explain the situation to the school to comply with vehicle, safety requirements, before the line for repairs. 5, each activity must have security, emergency response plan for accidents. 6, picnics, hiking, picnic to pay attention to fire prevention, food poisoning, prevention of fall accidents 7, the activities near the rivers, reservoirs, no measures or do not meet the security requirements of the Organization and not let students into the water

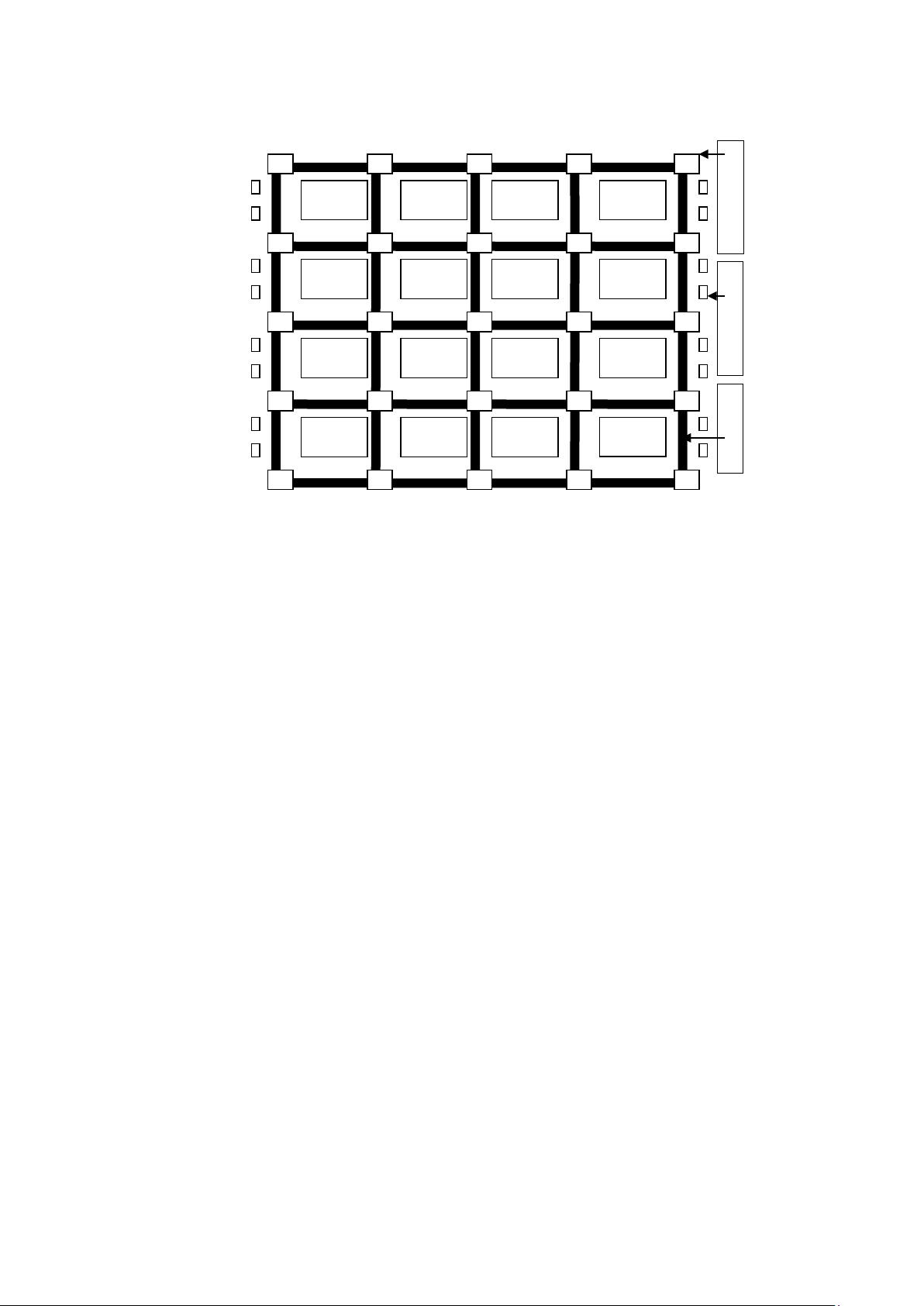

图2.1 CLB基本结构

2.3 FPGA 系统设计流程

一般说来,一个比较大的完整的项目应该采用层次化的描述方法:分为几个

较大的模块,定义好各功能模块之间的接口,然后各个模块再细分去具体实现,

这就是自顶向下的设计方法。目前这种高层次的设计方法已被广泛采用。高层次

设计只是定义系统的行为特征,可以不涉及实现工艺,因此还可以在厂家综合库

的支持下,利用综合优化工具将高层次描述转换为针对某种工艺优化的网络表,

使工艺转化变得轻而易举。

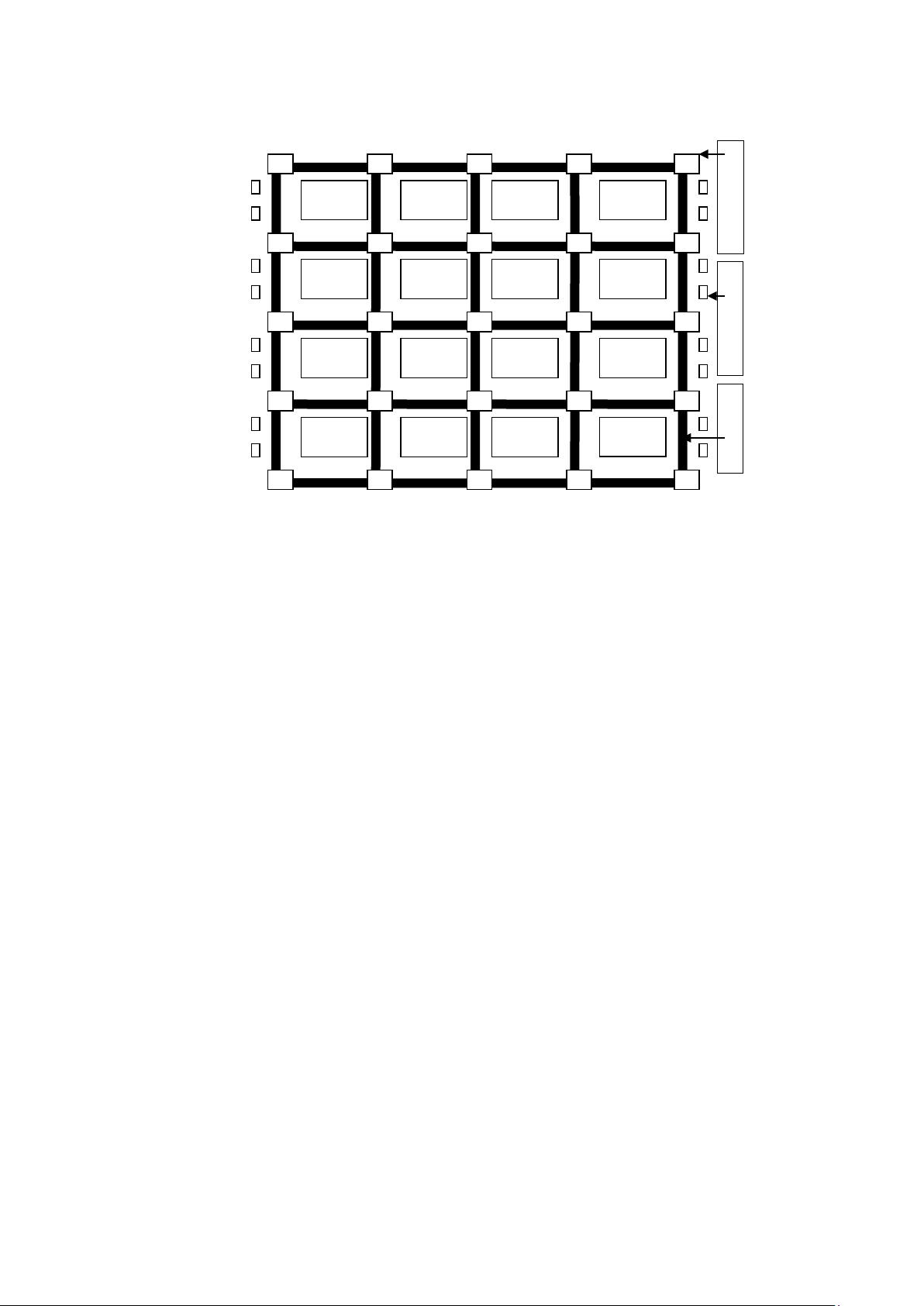

CPLD/FPGA系统设计的工作流程如图2.2所示。

流程说明:

1.工程师按照“自顶向下”的设计方法进行系统划分。

2.输入VHDL代码,这是设计中最为普遍的输入方式。此外,还可以采用图

形输入方式,这种输入方式具有直观、容易理解的优点。

3.将以上的设计输入编译成标准的VHDL文件。

4.进行代码级的功能仿真,主要是检验系统功能设计的正确性。这一步骤适

用于大型设计,因为对于大型设计来说,在综合前对源代码仿真,就可以大大减

少设计重复的次数和时间。一般情况下,这一仿真步骤可略去。

5.利用综合器对VHDL源代码进行综合优化处理,生成门级描述的网络表文

件,这是将高层次描述转化为硬件电路的关键步骤。综合优化是针对ASIC芯片

供应商的某一产品系列进行的,所以综合的过程要在相应的厂家综合库的支持下