NCOI Pcore在CPLD/FPGA中的Chirp函数实现及其IP核应用

43 浏览量

更新于2024-09-01

收藏 262KB PDF 举报

随着电子设计自动化(EDA)技术的迅速发展,复杂的可编程逻辑器件(CPLD)和现场可编程门阵列(FPGA)在各种电子产品设计中扮演着关键角色。IP核,即知识产权核或知识产权模块,是为满足特定应用而预先设计并封装的逻辑或数据单元,它们可以是FIR滤波器、SDRAM控制器、PCI接口等复杂功能模块。IP的核心价值在于提供标准化的、可配置的解决方案,减少了工程师的工作量,避免了重复设计。

IP核主要分为三种类型:软IP、固IP和硬IP。软IP是一种高级别的设计,由行为级描述语言(如Verilog或 VHDL)编写的代码组成,已经过行为级优化和功能验证,但不含具体物理实现。用户可以根据需求将其综合到自己的设计中,具有高度灵活性,适合大规模定制,但可能需要用户的后续结构设计和工艺适配。商业化的软IP通常拥有超过5000个门的电路结构,但设计不当可能导致集成失败。

硬IP则提供了更底层的实现,它基于特定的半导体工艺,具有固定的物理布局和工艺验证,确保了性能的一致性和可靠性。用户可以直接使用硬IP提供的电路模板和工艺文件,无需进行深入的物理设计,但它可能缺乏足够的灵活性以适应所有应用场景。

固IP设计介于软IP和硬IP之间,既包含了硬IP的物理实现,又保留了某种程度的行为级灵活性。它通常包括硬IP的所有设计,并可能进行了额外的优化,以适应更广泛的用户需求,同时提供了一定程度的自定义选项。

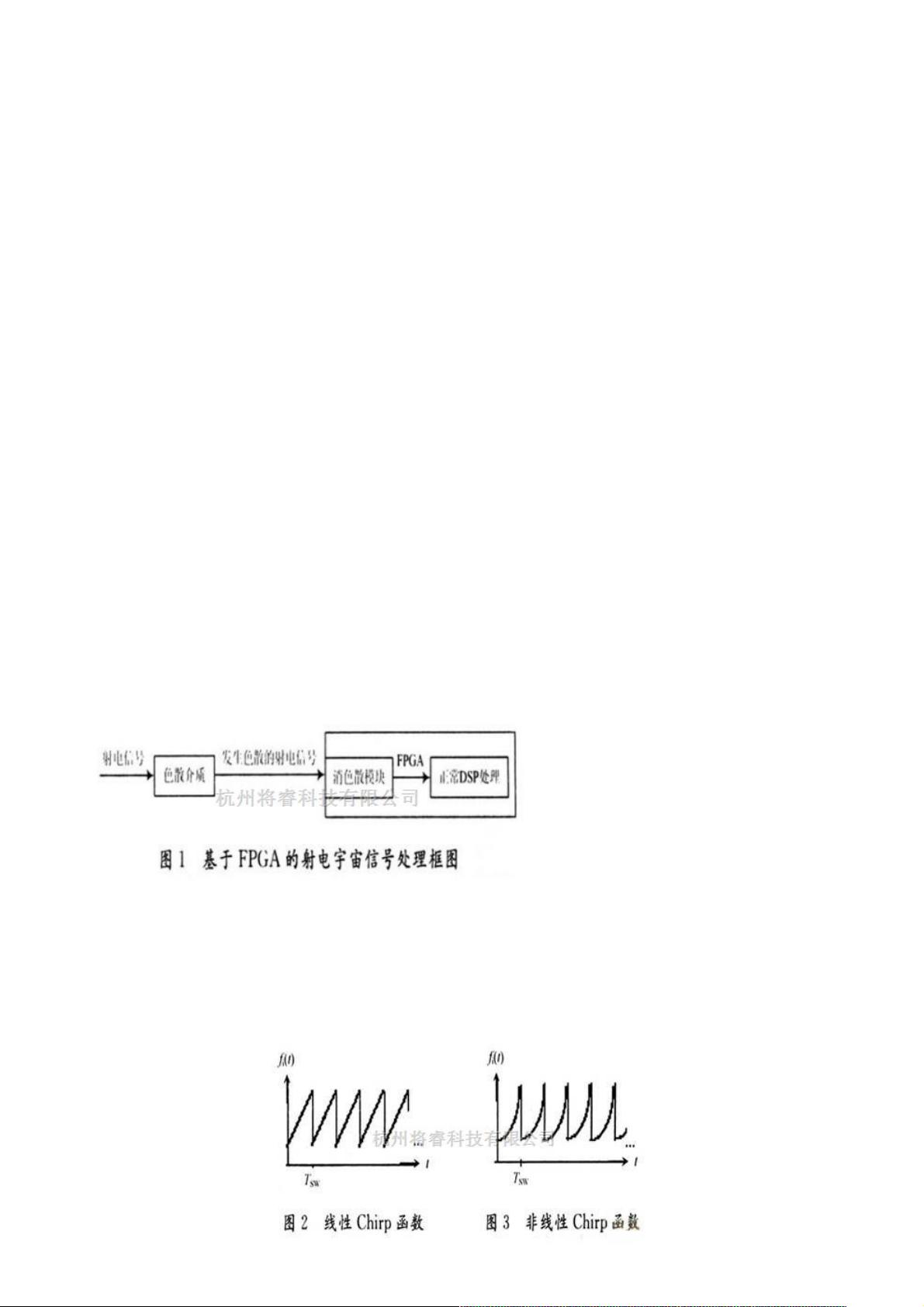

在利用NCOI Pcore实现Chirp函数的具体场景中,NCOI(数字频率合成器)Pcore可能是一个预设计的IP模块,用于生成Chirp信号,这是一种线性频率变化的信号,常见于雷达和通信系统中。通过集成NCOI Pcore,设计师可以在FPGA或CPLD上快速构建能够生成所需Chirp波形的系统,而无需从头开始设计复杂的数字信号处理逻辑。这种方法提高了设计效率,降低了风险,并且使IP核成为现代电子设计不可或缺的一部分。

点击了解资源详情

点击了解资源详情

点击了解资源详情

487 浏览量

2025-01-07 上传

2025-01-07 上传

2025-01-07 上传

weixin_38514805

- 粉丝: 9

- 资源: 932

最新资源

- rsa-src.zip

- 煤矿采煤机自动化与智能化技术研究.rar

- Highlight to Google Calendar-crx插件

- 博通网卡管理软件(Management Applications) v17.0.5.1 官方版

- peep-object:检查对象的所有组件

- NetThief81_8582.7z

- 大亨游戏

- Enegy-Generation-Company-SunSolar-ForntEnd-

- Rapid BSR-crx插件

- autocert:Python Web应用程序的自动TLS证书发行和续签

- 网上书店模板(有demo设计文档和界面源码,界面很帅哟,)

- TinyLinqJs:Linq-to-Objects 的 JavaScript 实现,以便将其与标准 JavaScript 数组一起使用

- arya.adslab

- Zet-crx插件

- 人脸检测编程实验工具.rar

- 腾达W522U无线USB网卡驱动