ModelSim代码覆盖率分析教程:从入门到序列检测器案例

需积分: 5 17 浏览量

更新于2024-08-03

1

收藏 173KB DOCX 举报

"ModelSim是一款常用的硬件描述语言(HDL)仿真工具,广泛应用于FPGA和ASIC设计的验证。代码覆盖率是衡量设计验证完整性的重要指标,ModelSim提供了强大的代码覆盖率分析功能,包括语句覆盖率、分支覆盖率、条件覆盖率、表达式覆盖率、信号反转覆盖率和有限状态机覆盖率等。本文将简要介绍如何在ModelSim中实现代码覆盖率分析,并通过序列检测器的仿真案例进行详细步骤说明。"

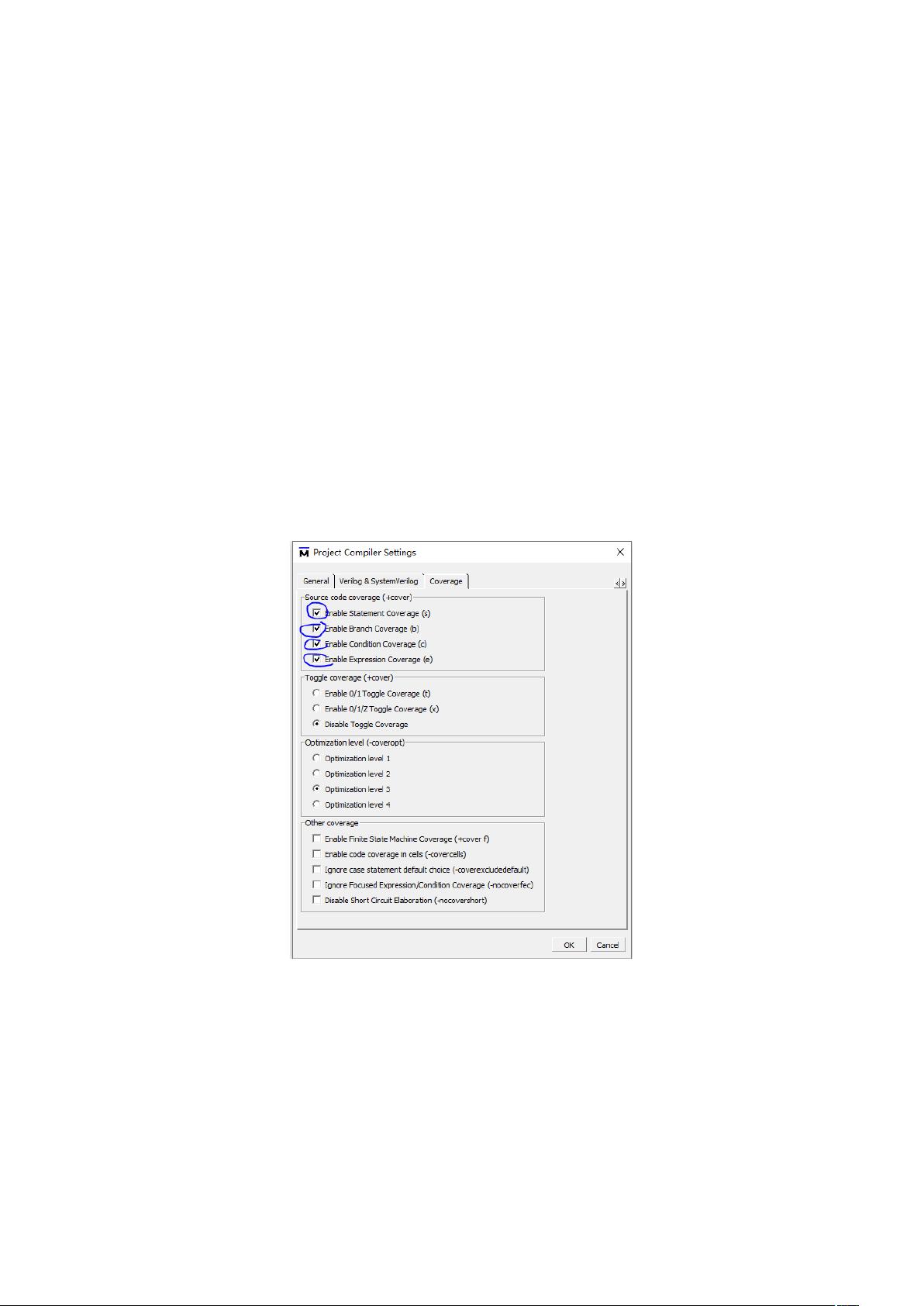

在ModelSim中进行代码覆盖率分析,首先需要在编译选项中开启覆盖率支持。在ModelSim的工作区(Workspace)中,选择需要进行覆盖率分析的源代码文件,使用Ctrl键多选,然后右键点击并选择“compile” → “compile properties” → “coverage”,在此界面勾选statement、branches、condition和expression等覆盖率类型。

接下来是编译阶段。对选中的文件进行编译,这可以通过在命令行窗口输入“compile-all”完成,也可以通过菜单栏的“compile all”选项进行。确保在编译时启用覆盖率功能。

在编译完成后,进入仿真阶段。为了启用代码覆盖率,需要在命令行窗口输入“vsim -voptargs=+acc -coveragework.test”,然后运行“run-all”。另一种方式是在“simulate”菜单中选择“start simulate”,在“Others UI”界面勾选“enable code coverage”选项,然后运行“run-all”。

仿真结束后,可以在“Instance coverage”和“File”窗口查看覆盖率结果。这些数据显示了每个模块或文件的覆盖率情况,例如在示例中,testbench的覆盖率是100%,而sequ_dtcr模块的覆盖率是97.74%。如果发现有未覆盖的部分,例如状态机的default分支,这可能是为了防止状态机进入异常状态的设计。

为了验证default分支是否按照预期工作,可以通过强制状态机进入非法状态来达到100%覆盖率。在Wave窗口中,选择“current_state”信号,右键点击“Force”,输入非法状态值(如8’h03)。此外,也可以使用脚本命令“force-freezesim:/test/sequ_dtcr_t0/curr”来实现同样的效果。

通过这种方式,ModelSim不仅提供了代码覆盖率的统计,还帮助开发者识别和测试设计中的未被触达部分,确保设计的全面验证。在实际项目中,代码覆盖率分析是保证设计质量、减少设计错误的关键步骤。

2009-07-29 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2008-10-29 上传

2020-08-15 上传

2012-06-24 上传

2020-10-23 上传

windyqiao

- 粉丝: 14

- 资源: 15

最新资源

- 开源数据结构:全球开源项目中使用的数据结构

- quiron:Modulo QtQuick para cargar en Unik Qml Engine-Modulo deaplicaciónpara Ayuda Memoria de DatosAstrológicos

- accyrding-policy-aloha.zip_TreeView控件_Visual_Basic_

- LogKyrcach

- 算法和数据结构:使用JavaScript实现的常见排序算法,数据结构和其他算法挑战的交互式概述

- led发光管(PE).rar_嵌入式/单片机/硬件编程_C/C++_

- 用于读取和写入图像数据的Python库-Python开发

- 第十三届中国大学生服务外包创新创业大赛-A08基于 FPGA 的铝片表面工业缺陷检测系统

- gdxextras:Libgdx的一些额外工具

- clean-undefined:删除未定义的对象字段

- Women-in-Big-Data-South-Africa:本笔记本介绍了Zindi竞赛(南非大数据中的女性-南非女性为户主的家庭)。 我们将快速浏览数据,展示如何创建模型,估算您在Zindi上获得的得分,准备提交并进入排行榜。 我还提供了一些有关如何获得更高分数的提示-一旦您第一次提交,这些都可能给您一些下一步尝试的想法

- 正方教务通用安卓

- libradio-开源

- 数据结构算法:此存储库包括我在本科期间所做的数据结构程序和算法。 这些是我自己用C ++从头开始编写的功能齐全的算法。 -要求:Microsoft Visual Studio 2019-打开sln文件以打开整个项目

- lilt:Lilt终端模拟器-用于Linux,macOS和其他类似Unix的系统的简单便携式终端模拟器

- siptapi-开源