Verilog语言详解:数字集成电路设计基础

版权申诉

PDF格式 | 1.47MB |

更新于2024-07-03

| 9 浏览量 | 举报

"该文档是关于数字集成电路原理与设计中Verilog语言的介绍,涵盖了Verilog的历史、HDL的基本概念、为什么使用HDL、Verilog程序的结构、建模方式以及测试验证等内容。"

在数字集成电路设计领域,Verilog是一种重要的硬件描述语言(HDL),用于描述和模拟电子系统的硬件行为。此文档详细介绍了Verilog的历史,从1977年的ISP研究项目到1995年成为IEEE标准的过程。Verilog最初由CMU的一个研究项目开发,旨在进行模拟,但不具备综合功能。1983年,GDA公司发布了Verilog HDL,这是Verilog的早期版本,随后在1985年得到了加强改进,仿真器升级为Verilog-XL。

随着技术的发展,Verilog逐渐被广泛采用。1989年,Cadence公司收购了GDA,进一步推动了Verilog的普及。1990年,为了管理Verilog的所有权,成立了OpenVerilog International(OVI)。到1993年,大多数ASIC设计都使用Verilog,其地位得到了进一步巩固。1995年,Verilog正式成为IEEE 1364-1995标准,与VHDL一起成为了国际上最广泛应用的硬件描述语言。

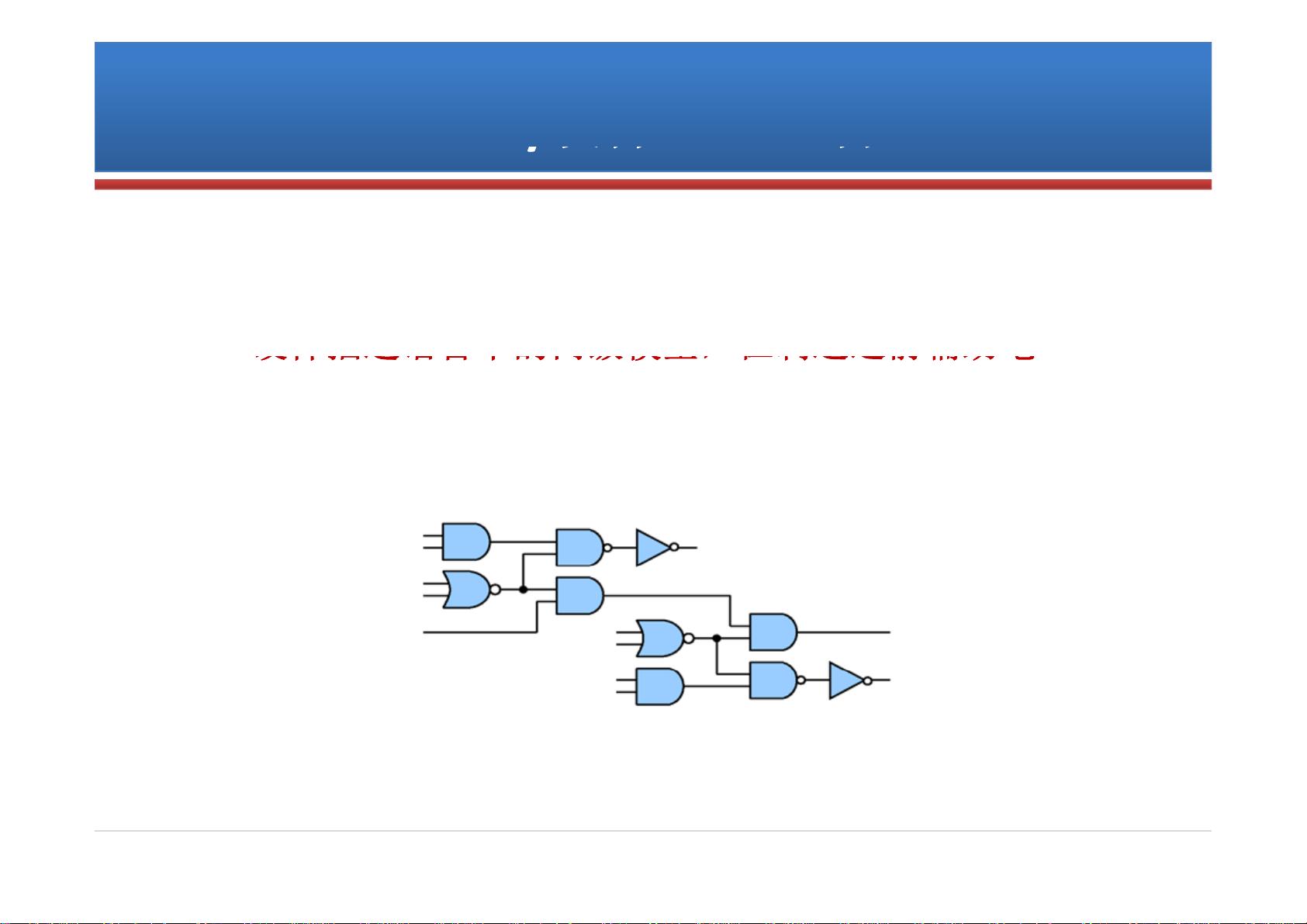

文档中还提到了Verilog程序的基本结构和建模方式,包括三种主要的建模技术:结构化建模、行为建模和混合建模。结构化建模主要用于描述电路的物理结构,如门级电路;行为建模则关注系统功能,不涉及实现细节;混合建模结合了两者,既能描述硬件结构也能表示高级行为。

测试验证是设计流程中的关键环节,Verilog提供了模块化和参数化的特性,使得创建测试平台和验证设计变得更加便捷。通过编写测试激励和观察预期输出,设计师可以确保设计的正确性。

总而言之,这份文档为读者提供了深入理解Verilog语言及其在数字集成电路设计中应用的基础知识,无论是对于初学者还是经验丰富的工程师,都是一个宝贵的参考资料。

相关推荐

智慧安全方案

- 粉丝: 3853

最新资源

- 探索Azure静态Web应用与TypeScript的结合

- Jellyfin-NMT: 实现网络媒体播放器与Jellyfin的无缝对接

- MySQL全套资料下载:安装包、文档与Java连接示例

- 基于SpringMVC与数据库的公司主页开发教程

- 全面入门汇编语言教程:从基础到高级应用

- 瑞萨rh850单片机ADC功能代码实现

- 炒股专用平板电脑软键盘软件V3.2发布

- 物质维度的探索:matter-dimensions开发版本发布

- 单人模式下如何加载Cayo Perico岛的CayoPericoRPH教程

- 青花瓷模板资源库:图片与模板大全下载

- 天香锦电话机系列开发接口支持OCX/DLL

- 自动组卷评分的单项选择题考试系统设计

- Fraps游戏录屏软件:高清无损视频录制利器

- 《钓球》主角真田由希蓝色头发可爱鼠标指针免费下载

- Flutter入门:customer_list2顾客管理应用开发指南

- OMSCS课程CS-7641: 掌握机器学习项目实践