指令流水线相关性分析实验报告:WinDLX模拟器探索

需积分: 15 52 浏览量

更新于2024-07-24

收藏 312KB DOCX 举报

"实验二 指令流水线相关性分析"

指令流水线是现代计算机处理器提高性能的重要手段,它将指令的执行过程分解为多个阶段,如取指、解码、执行、访存和写回,使得多条指令可以在同一时间的不同阶段并行处理。然而,这种并行处理可能会引发相关性问题,降低流水线的效率。

实验的目的在于通过使用WINDLX模拟器来观察和分析指令流水线中的三种主要相关性:结构相关、数据相关和控制相关,以及它们如何影响处理器性能。实验者需要对一个名为Fact.s的求阶乘程序进行分析,以深入理解RISC处理器的流水线特点。

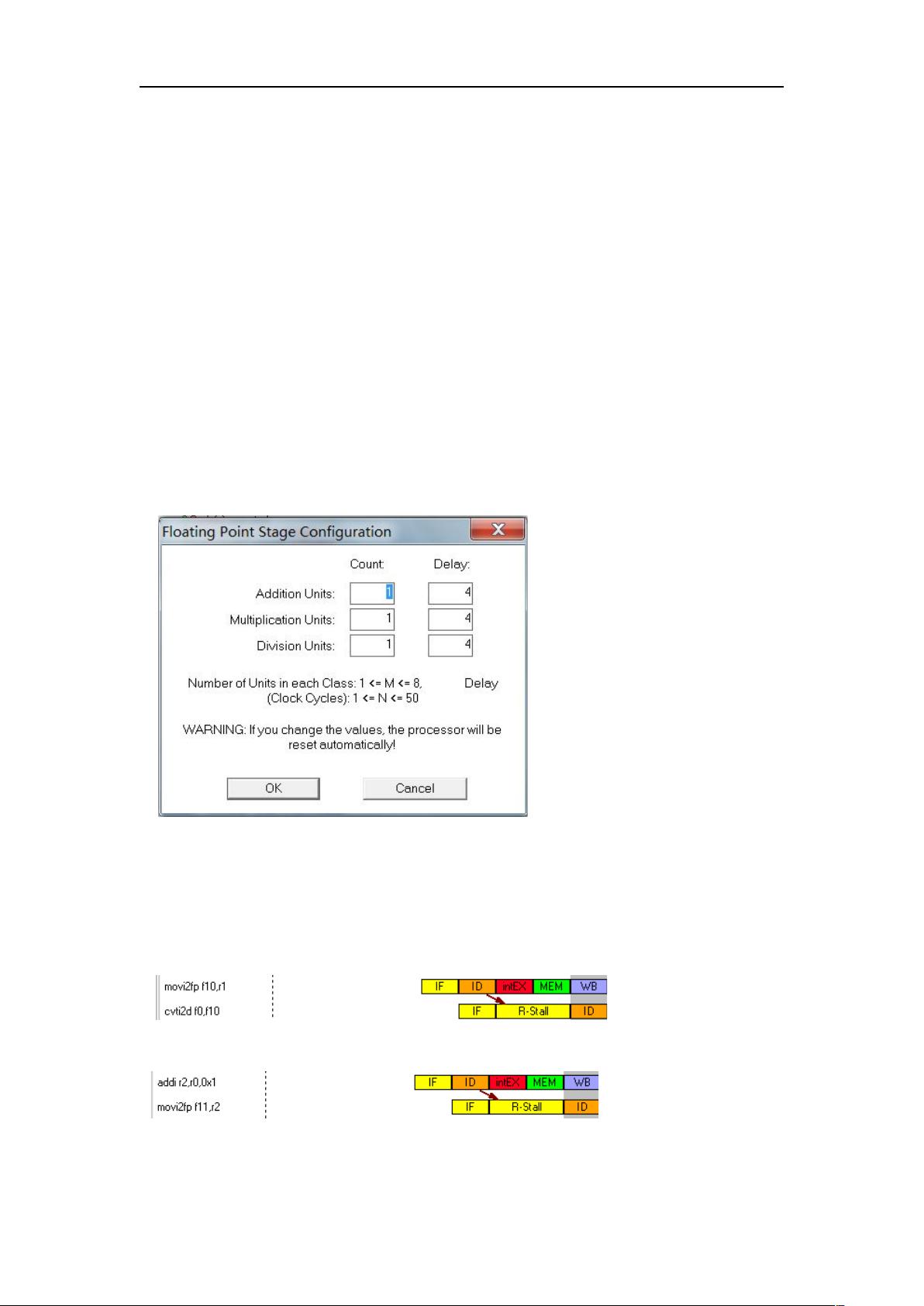

数据相关发生在当一条指令的结果被另一条指令所需,而这两条指令在流水线的不同阶段时。例如,W/R相关指的是写后读冲突,当一个寄存器或浮点寄存器在写入之后立即被读取,可能会影响到结果的正确性。在实验中,观察到了r2、f10、f11、f2、f4、r3、r5、r1和f0的W/R相关。

控制相关则涉及到分支和跳转指令。这些指令可能改变指令流的方向,从而中断流水线的正常流程。实验中,展示了不同类型的跳转和分支情况,包括无条件转移、条件分支(转移和不转移),以及循环跳转,所有这些都可能引起流水线的停顿,以更新指令预测和状态。

结构相关是指硬件资源的使用冲突,例如,当两个指令需要同时使用同一运算部件时。在最初的实验中,Fact.s程序没有结构相关,因此增加浮点运算部件并未提高性能。然而,通过在循环中添加额外的减法指令,人为制造了结构相关,导致了流水线的阻塞。

实验的最后部分考察了增加浮点运算部件对性能的影响。虽然这理论上可以增加并行计算的能力,但在Fact.s程序中,由于不存在结构相关,增加部件并未带来性能提升。这表明优化流水线设计需要根据具体程序的特性来定制,不能一概而论。

总结起来,这个实验通过实际操作和分析,让学生们深入理解了指令流水线的相关性问题及其对处理器性能的影响,同时也强调了优化处理器设计时需要考虑实际运行的程序和流水线的特性。

2010-06-16 上传

2023-06-07 上传

2023-06-07 上传

2023-06-12 上传

2023-06-01 上传

2023-06-12 上传

2023-06-13 上传

w8211279

- 粉丝: 0

- 资源: 6

最新资源

- 新型智能电加热器:触摸感应与自动温控技术

- 社区物流信息管理系统的毕业设计实现

- VB门诊管理系统设计与实现(附论文与源代码)

- 剪叉式高空作业平台稳定性研究与创新设计

- DAMA CDGA考试必备:真题模拟及章节重点解析

- TaskExplorer:全新升级的系统监控与任务管理工具

- 新型碎纸机进纸间隙调整技术解析

- 有腿移动机器人动作教学与技术存储介质的研究

- 基于遗传算法优化的RBF神经网络分析工具

- Visual Basic入门教程完整版PDF下载

- 海洋岸滩保洁与垃圾清运服务招标文件公示

- 触摸屏测量仪器与粘度测定方法

- PSO多目标优化问题求解代码详解

- 有机硅组合物及差异剥离纸或膜技术分析

- Win10快速关机技巧:去除关机阻止功能

- 创新打印机设计:速释打印头与压纸辊安装拆卸便捷性