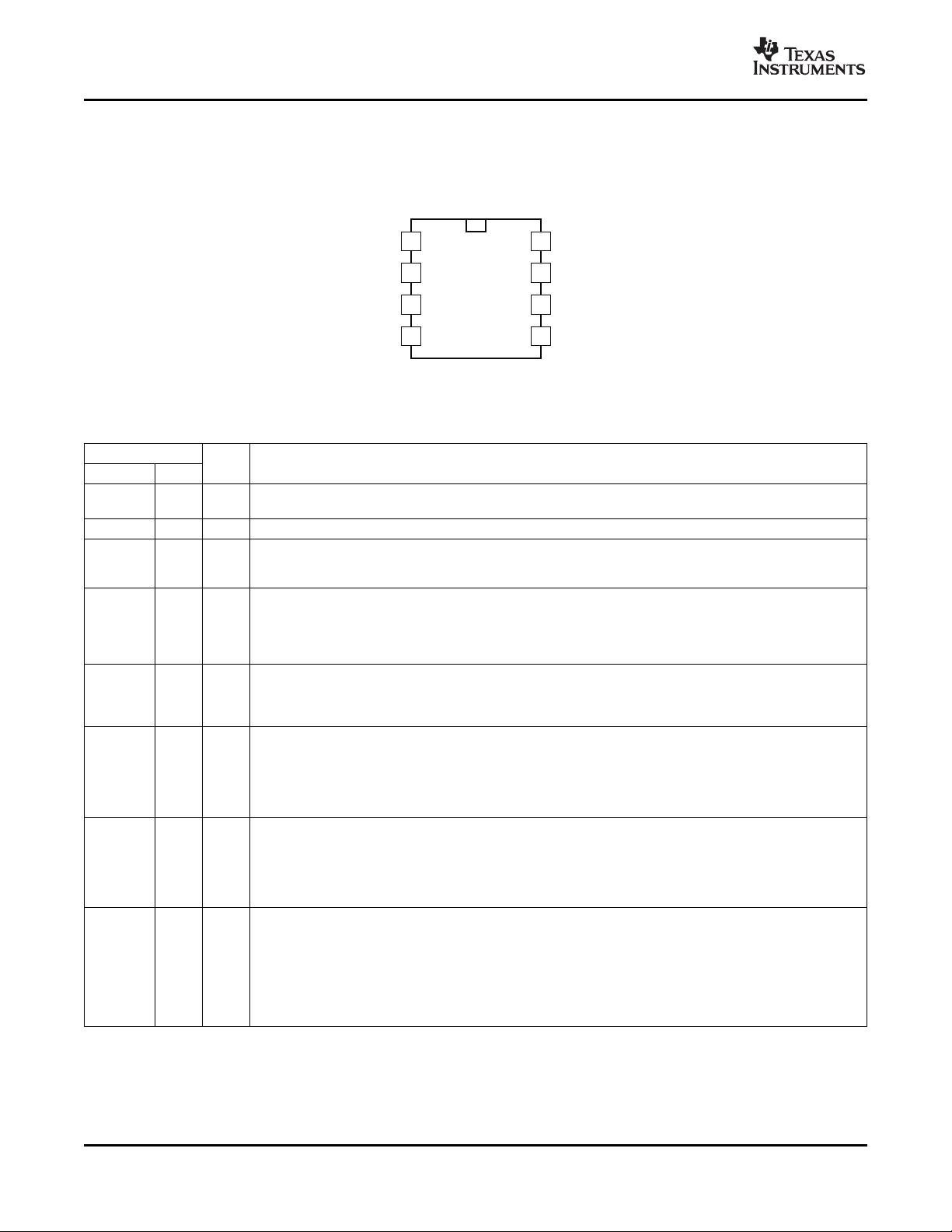

DEVICE INFORMATION

Connection Diagram

GND

ICOMP

ISENSE

GATE

VCC

VSENSE

VCOMP

VINS

1

2

3

4

8

7

6

5

Pin Descriptions

UCC28019

SLUS755B – APRIL 2007 – REVISED DECEMBER 2007

UCC28019 Top View (SOIC-8, PDIP-8)

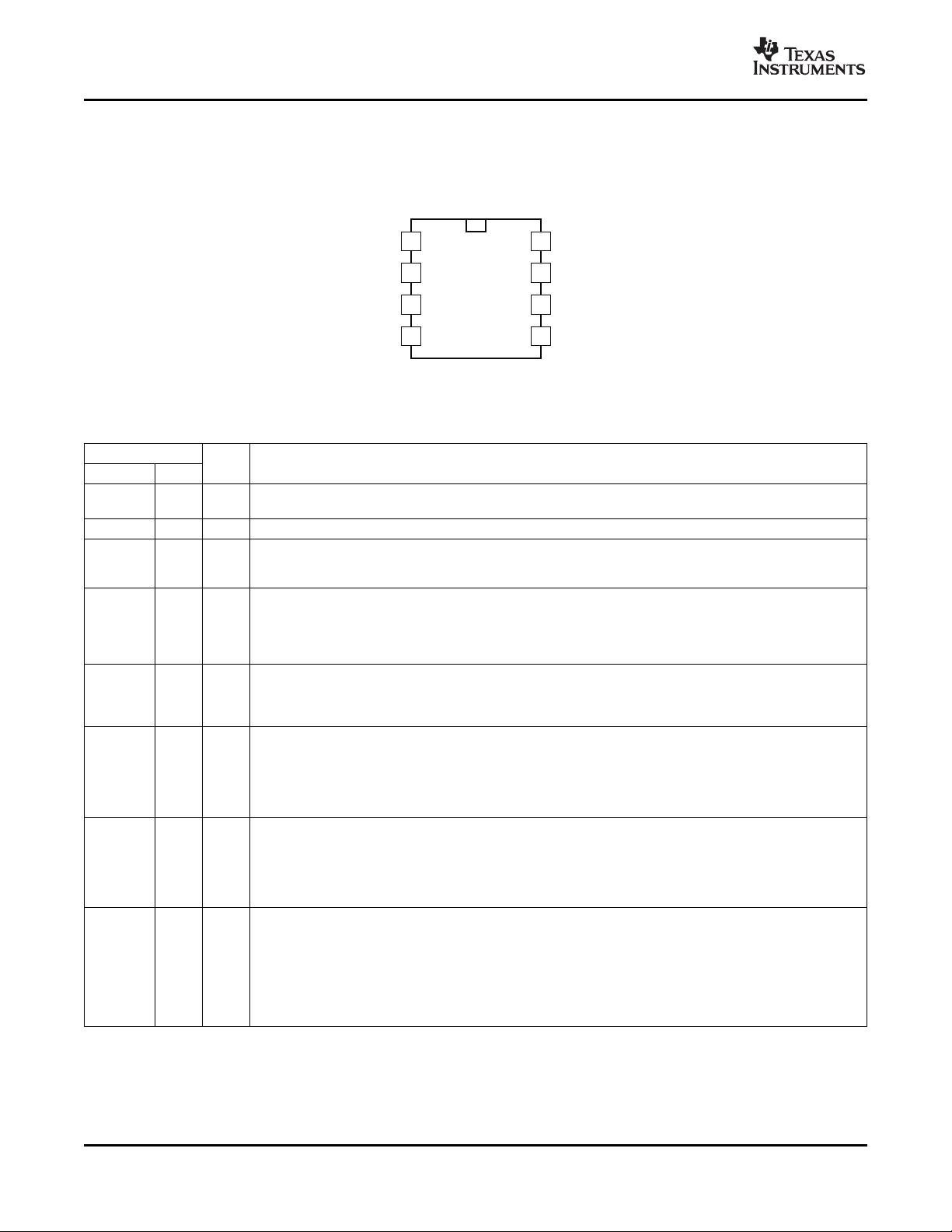

Terminal Functions

TERMINAL

I/O FUNCTION

NAME #

Gate drive: Integrated push-pull gate driver for one or more external power MOSFETs. 2.0-A sink and 1.5-A

GATE 8 O

source capability. Output voltage is clamped at 12.5 V.

GND 1 Ground: Device ground reference.

Current loop compensation: Transconductance current amplifier output. A capacitor connected to GND

ICOMP 2 O provides compensation and averaging of the current sense signal in the current control loop. The controller is

disabled if the voltage on ICOMP is less than 0.6 V.

Inductor current sense: An input for the voltage across the external current sense resistor, which represents

the instantaneous current through the PFC boost inductor. This voltage is averaged to eliminate the effects of

ISENSE 3 I noise and ripple. Soft Over Current (SOC) limits the average inductor current. Cycle-by-cycle peak current

limit (PCL) immediately shuts off the GATE drive if the peak-limit voltage is exceeded. Use a 220- Ω resistor

between this pin and the current sense resistor to limit inrush-surge currents into this pin.

Device supply: External bias supply input. Under Voltage Lock Out (UVLO) disables the controller until VCC

exceeds a turn-on threshold of 10.5 V. Operation continues until VCC falls below the turn-off (UVLO)

VCC 7

threshold of 9.5 V. A ceramic by-pass capacitor of 0.1 µ F minimum value should be connected from VCC to

GND as close to the device as possible for high frequency filtering of the VCC voltage.

Voltage loop compensation: Transconductance voltage error amplifier output. A resistor-capacitor network

connected from this pin to GND provides compensation. VCOMP is held at GND until VCC, VINS, and

VSENSE all exceed their threshold voltages. Once these conditions are satisfied, VCOMP is charged until the

VCOMP 5 O

VSENSE voltage reaches 95% of its nominal regulation level. When the Enhanced Dynamic Response (EDR)

is engaged, additional current is applied to VCOMP to reduce the charge time. EDR additional current is

inhibited during soft-start. Soft-start is programmed by the capacitance on this pin.

Input ac voltage sense: Input Brown Out Protection (IBOP) detects when the system ac-input voltage is

above a user-defined normal operating level, or below a user-defined “ brown-out ” level. A filtered

resistor-divider network connects from this pin to the rectified-mains node. At startup the controller is disabled

VINS 4 I

until the VINS voltage exceeds a threshold of 1.5 V, initiating a soft-start. The controller is also disabled if

VINS drops below the brown-out threshold of 0.8 V. Operation will not resume until both VINS and VSENSE

voltages exceed their enable thresholds, initiating another soft-start.

Output voltage sense: An external resistor-divider network connected from this pin to the PFC output

voltage provides feedback sensing for output voltage regulation. A small capacitor from this pin to GND filters

high-frequency noise. Standby disables the controller and discharges VCOMP when the voltage at VSENSE

drops below the enable threshold of 0.8V. An internal 100nA current source pulls VSENSE to GND for

VSENSE 6 I

Open-Loop Protection (OLP), including pin disconnection. Output over-voltage protection (OVP) disables the

GATE output when VSENSE exceeds 105% of the reference voltage. Enhanced Dynamic Response (EDR)

rapidly returns the output voltage to its normal regulation level when a system line or load step causes

VSENSE to fall below 95% of the reference voltage.

10 Submit Documentation Feedback Copyright © 2007, Texas Instruments Incorporated

Product Folder Link(s): UCC28019