FPGA平台上的DDS信号发生器实现

"基于FPGA的DDS信号发生器设计"

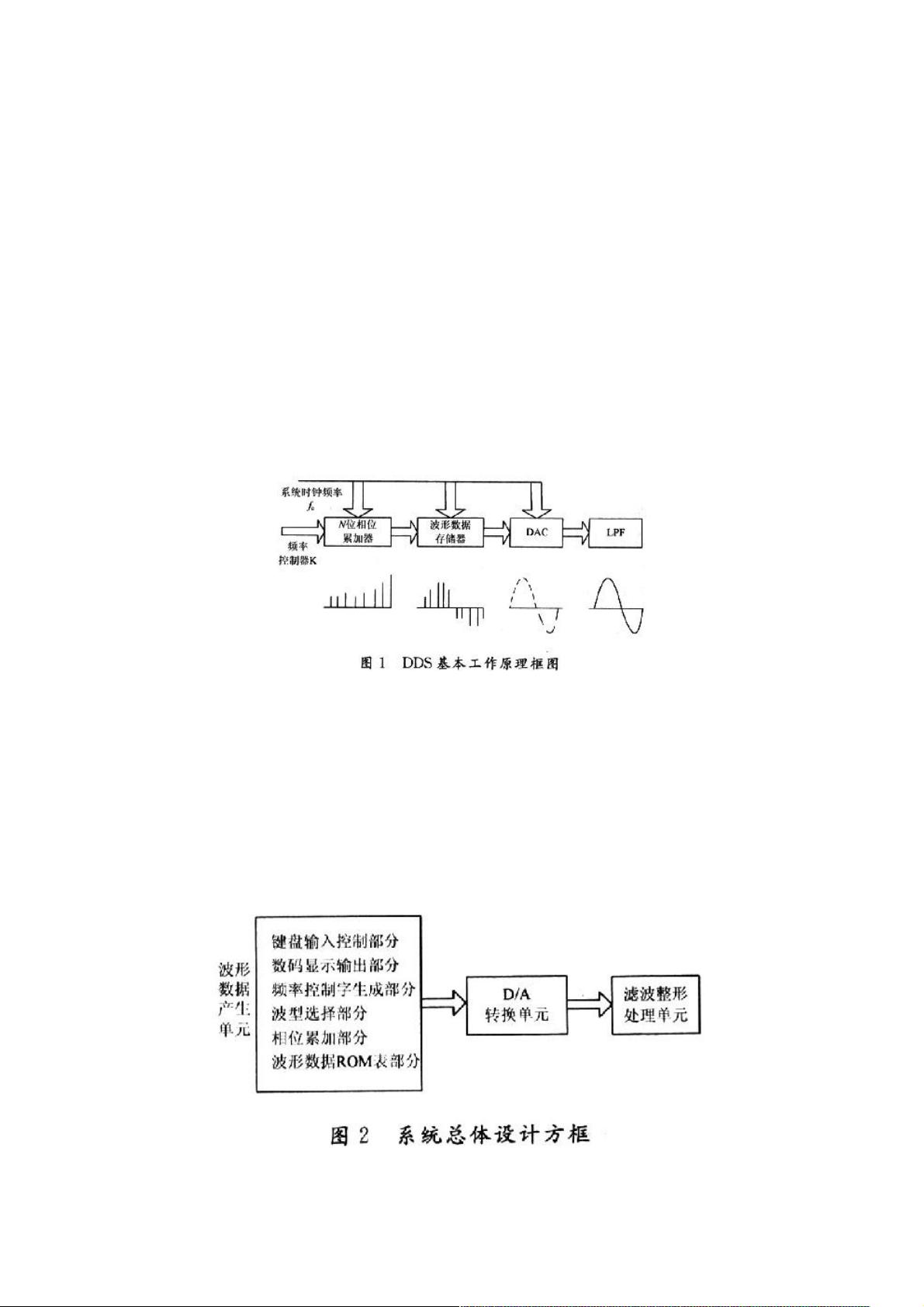

DDS(直接频率合成)技术是一种现代电子信号发生器的核心技术,它允许快速、精确且灵活地生成各种波形,包括正弦波、三角波、矩形波等。DDS的基本思想是通过数字化的方式来控制信号的频率、幅度和相位,从而实现频率合成。在传统的信号发生器中,通常采用分立元件或专用集成芯片来实现,但这些方法存在频率范围有限、稳定性差和调试困难等问题。

FPGA(Field-Programmable Gate Array)是可编程逻辑器件,它的灵活性和高速处理能力使得在FPGA上实现DDS成为可能。相比使用专用DDS芯片,基于FPGA的DDS信号发生器有以下优势:

1. **成本效益**:FPGA的可编程性意味着可以复用硬件资源,减少了对专门芯片的需求,降低了硬件成本。

2. **灵活性**:用户可以根据需要定制信号发生器的功能,例如改变输出波形、频率和幅度,无需更换硬件。

3. **实时更新**:FPGA允许通过软件更新配置,可以在运行时动态调整参数,适应不同的应用需求。

4. **高性能**:FPGA的并行处理能力可以实现高速信号生成,满足高频率和低抖动的要求。

5. **系统集成**:DDS系统中的大部分组件,如相位累加器、查找表和D/A转换器,都可以在FPGA内部实现,便于系统的小型化和集成。

DDS信号发生器的核心部分包括以下几个模块:

- **相位累加器**:接收频率控制字(FSW),每次参考时钟脉冲到来时,相位累加器的输出增加一个步长的相位增量。相位累加器的位宽决定了频率分辨率,即最小可调频率。

- **查找表(LUT)**:存储预计算的波形样本,相位累加器的输出作为地址,读取对应的幅度值。

- **D/A转换器**:将查找表输出的数字值转换为模拟信号,形成最终的输出波形。

- **低通滤波器(LPF)**:滤除高频噪声,平滑数字输出,得到连续的模拟波形。

在FPGA中实现DDS,需要考虑的关键设计因素包括:

- **频率精度和分辨率**:取决于相位累加器的位数和参考时钟的频率,更高的位数和频率能提供更好的频率分辨率。

- **带宽和失真**:低通滤波器的设计决定信号的带宽,同时需要优化以减少谐波失真。

- **实时性**:FPGA的处理速度应足够快,以保证在每个时钟周期内完成相位累加和查表操作。

- **功耗和散热**:在保持高性能的同时,需要关注FPGA的功耗和散热设计,以确保设备的长期稳定运行。

本文研究的基于FPGA的DDS信号发生器设计,旨在利用FPGA的优势,实现一个成本低、操作灵活、可定制化的多功能信号发生器。通过精心设计和优化,该发生器能够产生多种满足预定指标的波形,适应不同应用场景的需求。在实际应用中,这种DDS信号发生器可以广泛应用于通信系统测试、电子设备调试、科研实验等多个领域。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2012-10-10 上传

2009-07-18 上传

123 浏览量

2011-08-23 上传

2021-07-13 上传

2023-06-20 上传

weixin_38692100

- 粉丝: 3

- 资源: 871

最新资源

- README_Generator

- designpatterns:设计模式

- reviews:回顾我参加的一些在线CS课程

- mmpose和openpose的onnx导出

- AMI_CRT-0.1-py3-none-any.whl.zip

- ASP Jscript Calendar-开源

- 梦境前端

- nodesql:带有SQL Server的节点

- wiki.central.ntua.gr

- TU-Chemnitz-thesis-pandoc:使用 pandoc 的 TU-Chemnitz 模板

- learn_flutter_with_git

- Scrumdidilyumptio.us-开源

- My Template-开源

- AMQPStorm-2.6.2-py2.py3-none-any.whl.zip

- oslfrobot.github.io:有关一个传感器行跟随器机器人的网站,该机器人还可以避开物体并进行自动校准

- 仓库SWWReact节点MySQL