Section 1.8 Application-Specific ICs 17

DO NOT COPY

DO NOT COPY

DO NOT COPY

DO NOT COPY

DO NOT COPY

DO NOT COPY

DO NOT COPY

DO NOT COPY

DO NOT COPY

Copyright © 1999 by John F. Wakerly Copying Prohibited

internal structure of the chip, creating tooling such as the metal masks for manu-

facturing the chips, developing tests for the manufactured chips, and actually

making the first few sample chips.

The NRE cost for a typical, medium-complexity ASIC with about 100,000

gates is $30–$50,000. An ASIC design normally makes sense only when the

NRE cost can be offset by the per-unit savings over the expected sales volume of

the product.

The NRE cost to design a

custom LSI

chip—a chip whose functions, inter-

nal architecture, and detailed transistor-level design is tailored for a specific

customer—is very high, $250,000 or more. Thus, full custom LSI design is done

only for chips that have general commercial application or that will enjoy very

high sales volume in a specific application (e.g., a digital watch chip, a network

interface, or a bus-interface circuit for a PC).

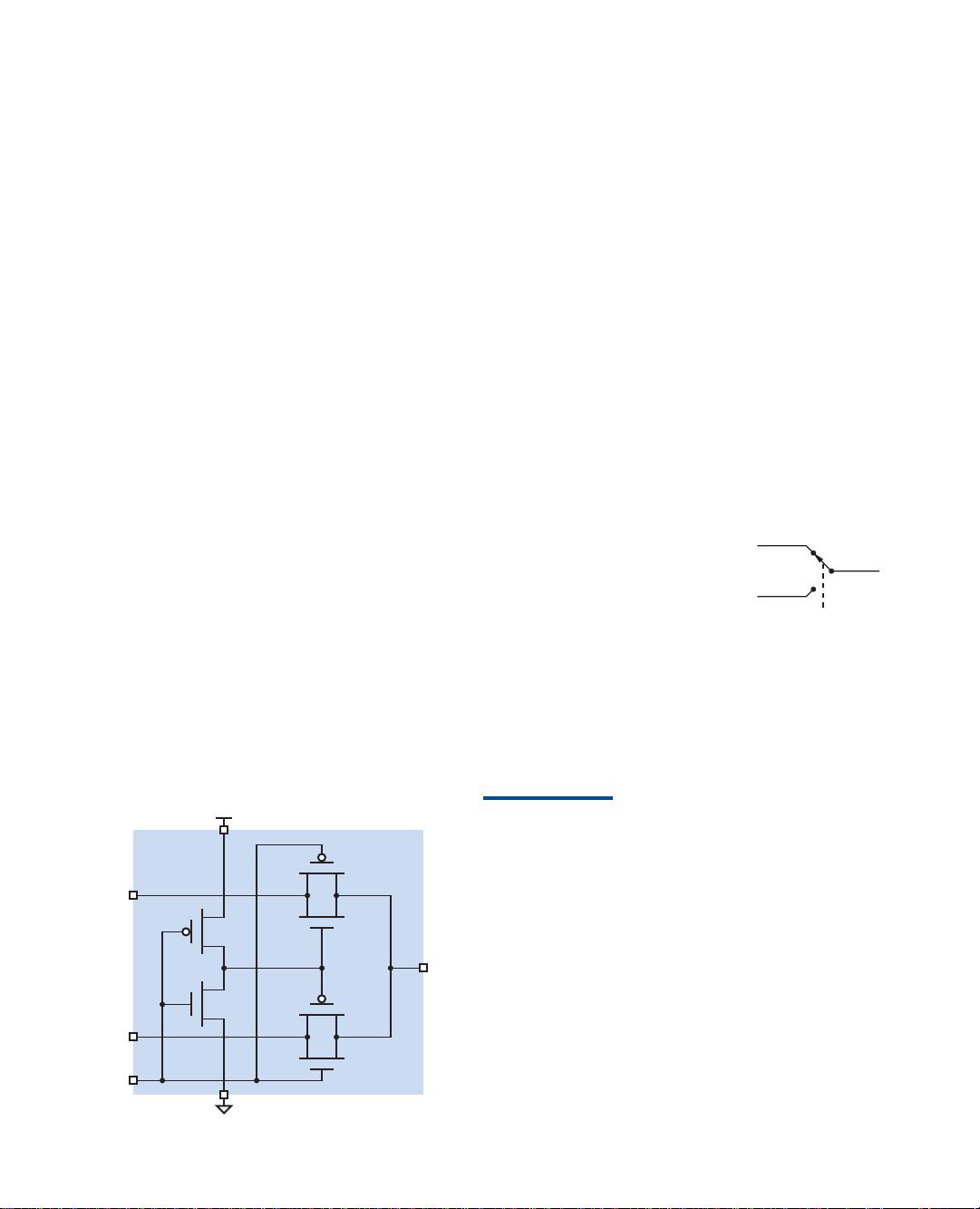

To reduce NRE charges, IC manufacturers have developed libraries of

standard cells

including commonly used MSI functions such as decoders,

registers, and counters, and commonly used LSI functions such as memories,

programmable logic arrays, and microprocessors. In a

standard-cell design

, the

logic designer interconnects functions in much the same way as in a multichip

MSI/LSI design. Custom cells are created (at added cost, of course) only if abso-

lutely necessary. All of the cells are then laid out on the chip, optimizing the

layout to reduce propagation delays and minimize the size of the chip. Minimiz-

ing the chip size reduces the per-unit cost of the chip, since it increases the

number of chips that can be fabricated on a single wafer. The NRE cost for a

standard-cell design is typically on the order of $150,000.

Well, $150,000 is still a lot of money for most folks, so IC manufacturers

have gone one step further to bring ASIC design capability to the masses. A

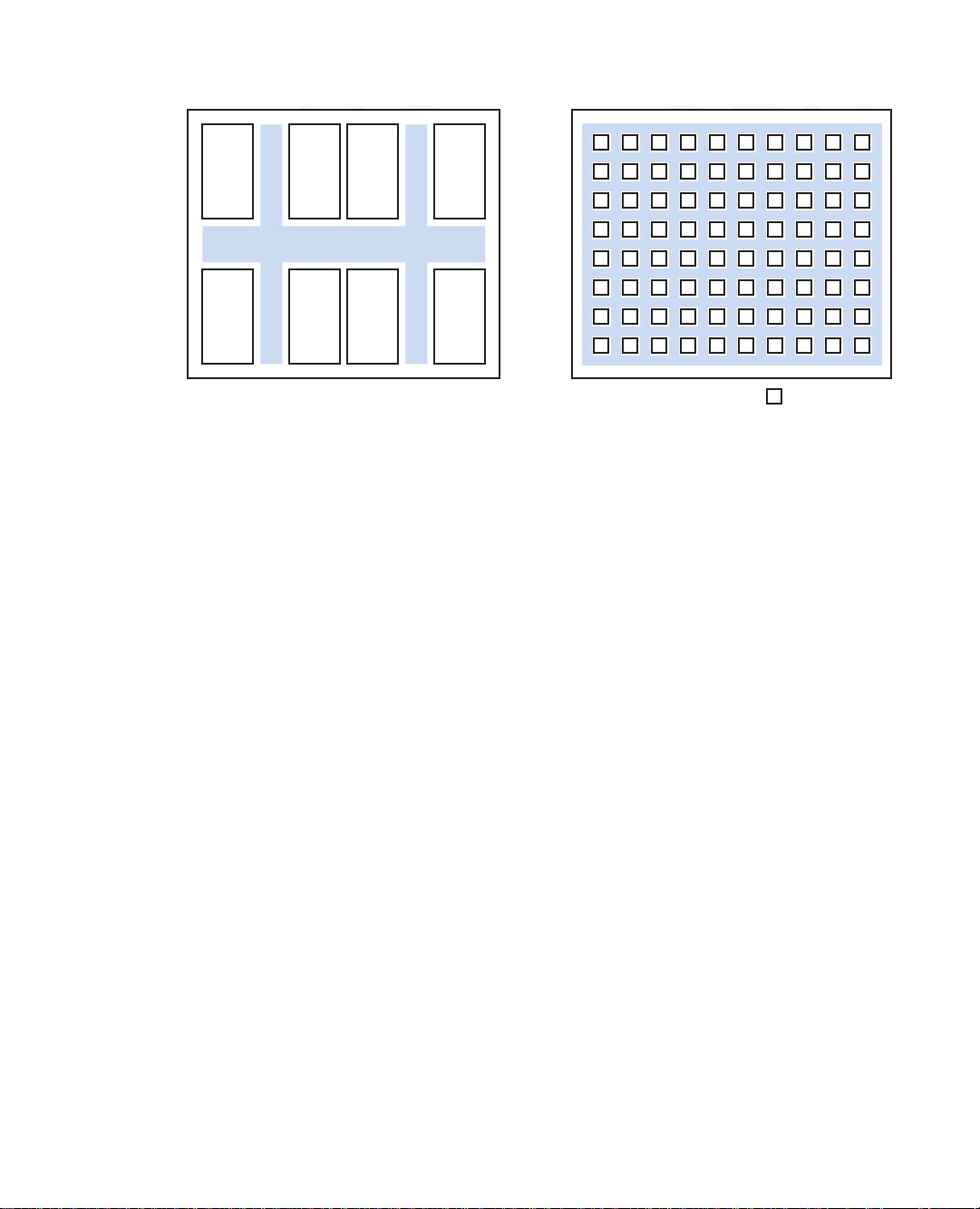

gate

array

is an IC whose internal structure is an array of gates whose interconnec-

tions are initially unspecified. The logic designer specifies the gate types and

interconnections. Even though the chip design is ultimately specified at this very

low level, the designer typically works with “macrocells,” the same high-level

functions used in multichip MSI/LSI and standard-cell designs; software

expands the high-level design into a low-level one.

The main difference between standard-cell and gate-array design is that the

macrocells and the chip layout of a gate array are not as highly optimized as

those in a standard-cell design, so the chip may be 25% or more larger, and

therefore may cost more. Also, there is no opportunity to create custom cells in

the gate-array approach. On the other hand, a gate-array design can be complet-

ed faster and at lower NRE cost, ranging from about $5000 (what you’re told

initially) to $75,000 (what you find you’ve spent when you’re all done).

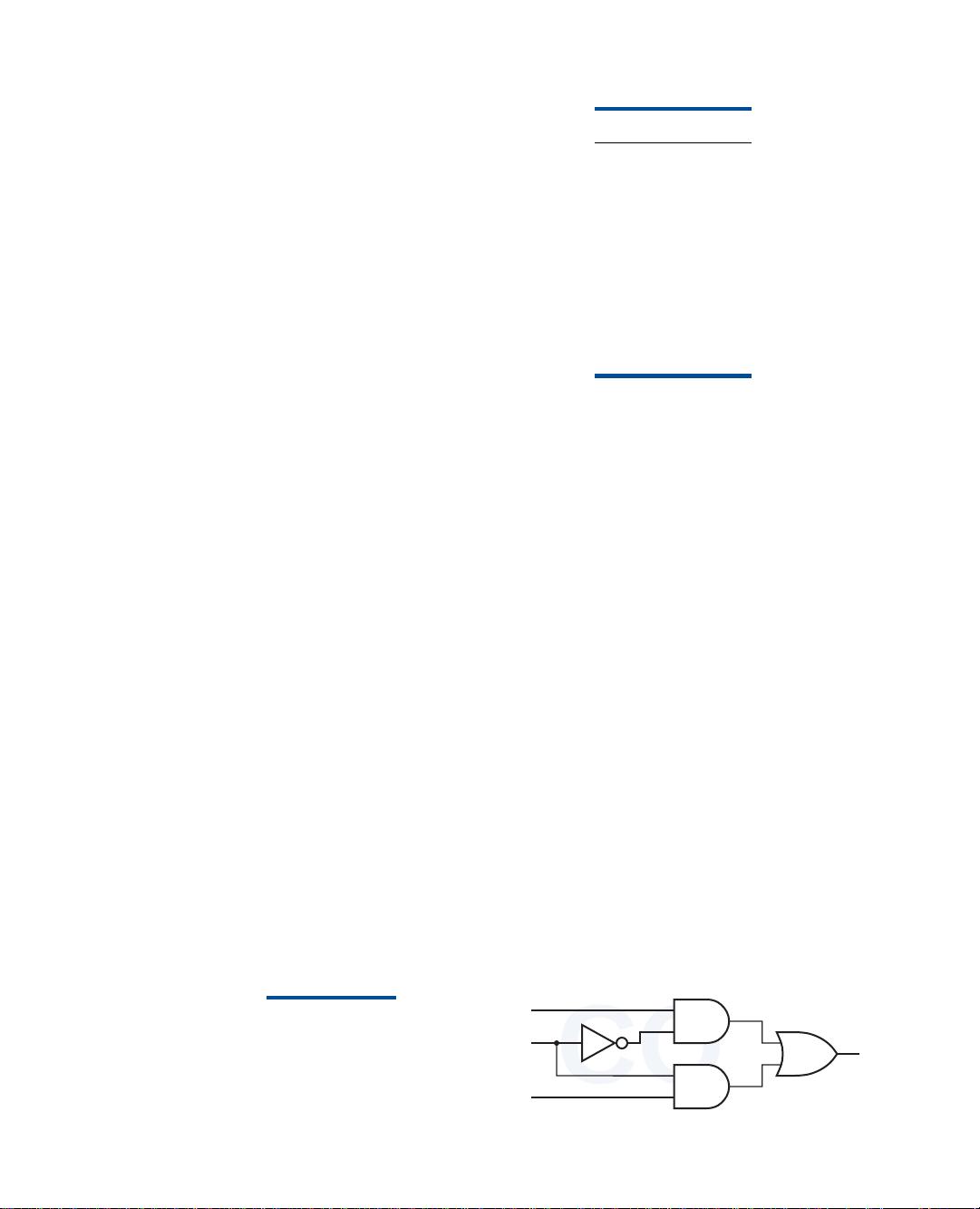

The basic digital design methods that you’ll study throughout this book

apply very well to the functional design of ASICs. However, there are additional

opportunities, constraints, and steps in ASIC design, which usually depend on

the particular ASIC vendor and design environment.

custom LSI

standard cells

standard-cell design

gate array