华为FPGA高级设计策略:优化与资源利用

本篇文章是关于华为FPGA设计的高级技巧指南,由深圳市华为技术有限公司的研究管理部文档中心内部公开,针对Xilinx平台进行深入讲解。这份文档共有62页,涵盖了丰富的设计策略和知识点,旨在帮助FPGA学习者提升设计效率和优化资源利用。

1. **逻辑优化**:

- **关键路径优化**:介绍了如何通过减少关键路径的逻辑级数(章节4.3)来提高设计的速度性能,减少延迟。

- **IF语句和Case语句**:在设计中,理解并恰当使用这些控制结构(章节4.2)有助于组织复杂逻辑,降低逻辑资源的消耗。

2. **资源利用**:

- **LUT配置**:章节3.8详细解释了如何通过配置LUT作为组合逻辑电路,虽然门数增加,但逻辑级数保持不变,从而节省资源,提高速度(3.8.1)。

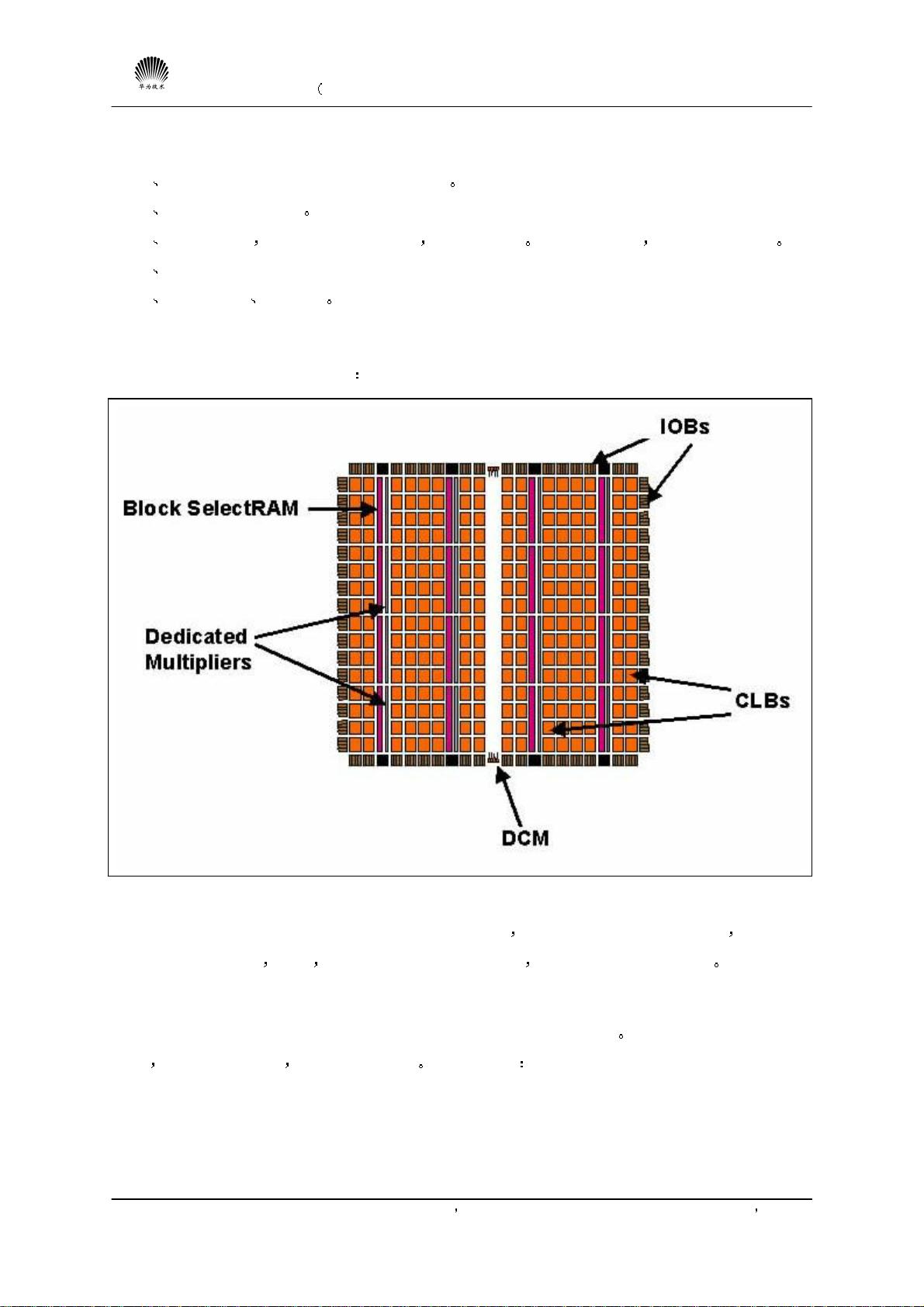

- **BlockSelectRAM**:分析了BlockSelectRAM的内部结构,以及如何利用它(3.4.2),这对于内存操作优化至关重要。

3. **时钟管理**:

- **DCM、CLKMUX和GlobalClock**:3.7章介绍了数字时钟管理单元(DCM)、时钟多路复用器(CLKMUX)以及全局时钟管理,这些都是优化时钟性能的关键部分。

- **DCI**:3.6.3节讨论了数据通信接口,对于I/O时序控制有重要作用。

4. **输入/输出接口**:

- **IOB结构**:了解IOB(输入/输出块)的设计和使用方法(3.6.1),确保信号传输的高效性和准确性。

- **SelectI/O**:3.6.2部分讲解了如何有效地选择和配置I/O引脚。

5. **算术运算**:

- **加法器**:详细分析了串行进位与超前进位的处理方式(4.1.1),以及合理选择加法电路的重要性(4.1)。

- **乘法器资源**:讨论了乘法器资源的分配和优化(3.5)。

6. **存储器**:

- **BlockRAM和DistributedRAM**:章节3.4介绍了分布式RAM和BlockRAM的不同类型及其在设计中的应用。

7. **基本逻辑单元**:

- **LUT、Slice和CLB**:3.3节介绍了基本逻辑单元(LUT)、逻辑综合块(Slice)和基本逻辑细胞(CLB)的概念,以及它们如何影响设计风格。

8. **编码风格和器件结构**:

- **ASIC与FPGA结构对比**:3.1.1和3.1.2章节探讨了ASIC和FPGA这两种器件架构对编程风格的不同影响。

- **器件结构对编码的影响**:解释了器件结构如何决定代码编写的方式和性能需求。

总结来说,本文档提供了华为FPGA设计中的一系列高级技巧,包括逻辑优化、资源管理和具体组件的使用,是FPGA设计者深入学习和提高技能的重要参考资料。通过掌握这些高级技巧,设计者能够更有效地利用Xilinx FPGA,提高设计质量和效率。

2008-12-16 上传

2013-08-28 上传

2023-08-10 上传

2023-07-29 上传

2023-08-02 上传

2024-01-27 上传

2023-07-16 上传

2023-11-25 上传

2023-09-07 上传

sunyzz

- 粉丝: 3

- 资源: 12

最新资源

- 新型智能电加热器:触摸感应与自动温控技术

- 社区物流信息管理系统的毕业设计实现

- VB门诊管理系统设计与实现(附论文与源代码)

- 剪叉式高空作业平台稳定性研究与创新设计

- DAMA CDGA考试必备:真题模拟及章节重点解析

- TaskExplorer:全新升级的系统监控与任务管理工具

- 新型碎纸机进纸间隙调整技术解析

- 有腿移动机器人动作教学与技术存储介质的研究

- 基于遗传算法优化的RBF神经网络分析工具

- Visual Basic入门教程完整版PDF下载

- 海洋岸滩保洁与垃圾清运服务招标文件公示

- 触摸屏测量仪器与粘度测定方法

- PSO多目标优化问题求解代码详解

- 有机硅组合物及差异剥离纸或膜技术分析

- Win10快速关机技巧:去除关机阻止功能

- 创新打印机设计:速释打印头与压纸辊安装拆卸便捷性