"单片机课程设计:iic总线式eeprom存储器应用设计"

DOC格式 | 550KB |

更新于2024-01-30

| 111 浏览量 | 举报

本篇文档是关于单片机课程设计中应用IIC总线式EEPROM存储器的设计。下面将根据文档的内容进行总结,最终达到2000字的要求。

本文档的目录明确了设计要求和设计目的。设计要求部分列举了对该设计的具体要求,包括使用IIC总线和EEPROM存储器、实现数据的读写操作、要求设计出完整的电路原理图和PCB布局图等。设计目的部分说明了本设计的目的在于通过实践来加深对单片机课程所学知识的理解和应用,并且提升综合能力。

在第三部分中,介绍了关于EEPROM的基本概念和特点。EEPROM是一种可擦除可编程的电子存储器,通过电信号来控制其中的晶体管开关状态,实现数据的存储和读取。与传统的ROM相比,EEPROM可以在不移出芯片的情况下进行数据的修改。

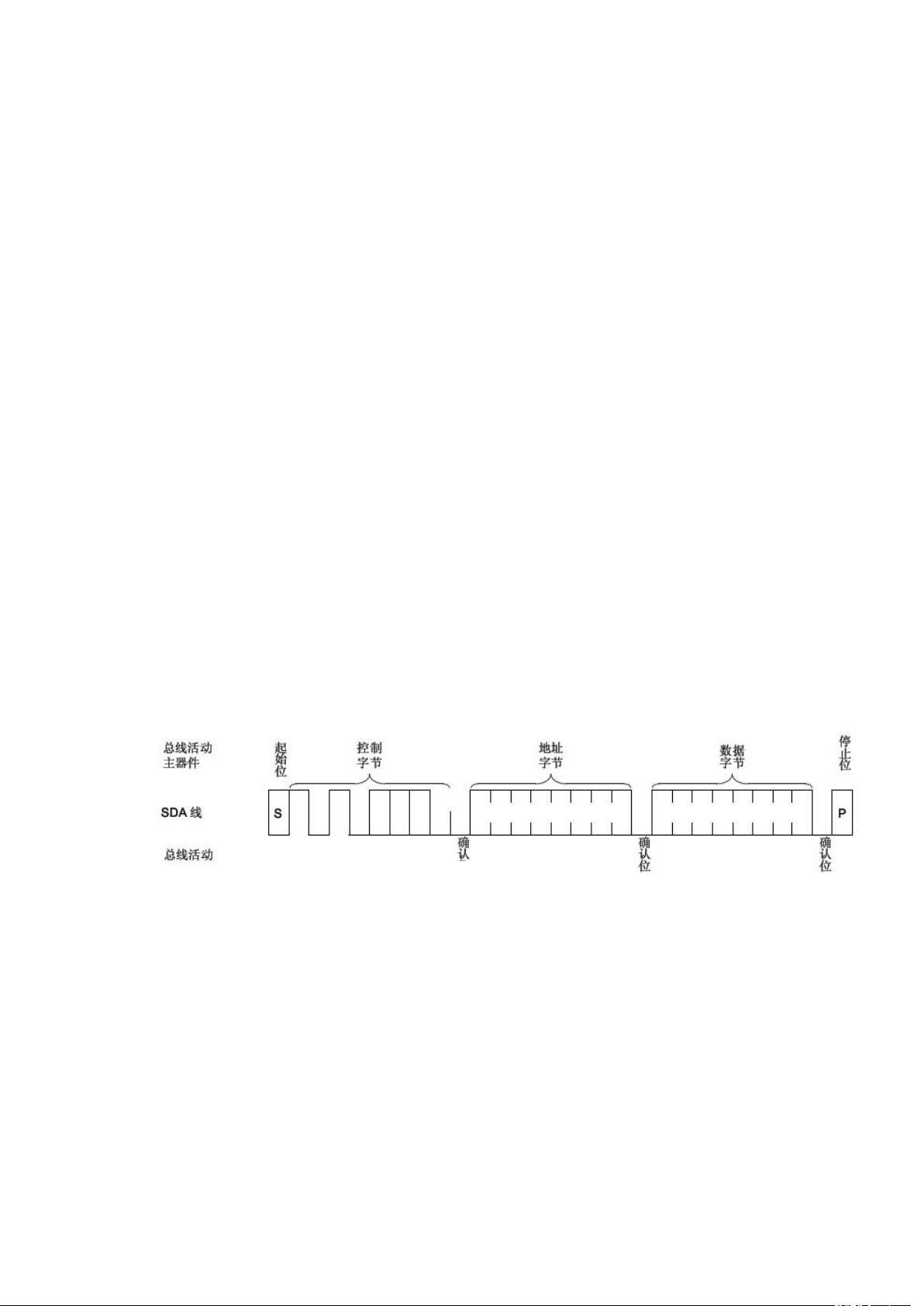

接着,本文档对设计的整体框架进行了详细的描述和分析。首先,在硬件设计部分,列举了设计所需的各种器件和元件,并给出了电路图和PCB布局图。其中,涉及到了单片机、EEPROM、电源等器件。通过IIC总线的搭建,实现了EEPROM与单片机之间的通信和数据交互。在软件设计部分,给出了设计所需的基本操作代码,并进行了详细的注解和解释。通过编写具体的读写函数,实现了对EEPROM中数据的读写操作,并在LCD显示屏上进行了实时显示。

在第五部分,对设计的测试结果进行了详细的记录和分析。通过实际测试,验证了设计的正常运行和各项功能的实现。测试结果表明,设计具备了良好的稳定性和可靠性,能够满足设计要求和设计目的。

最后,在结论部分,总结了本次设计的成果和经验,并提出了改进的建议。本设计通过将单片机与EEPROM相结合,实现了数据的读写操作,提升了综合能力和动手实践能力。同时,在设计过程中也发现了一些问题和不足之处,对这些问题提出了改进的建议,以便在后续的设计中能够得到更好的应用和发展。

总而言之,本文档详细介绍了单片机课程设计中应用IIC总线式EEPROM存储器的设计。通过对设计要求和设计目的的分析,在硬件设计和软件设计方面进行了详细的阐述,并通过实际测试验证了设计的正确性和可行性。在结论部分,对本次设计进行了总结,并提出了改进的建议。通过本篇文档的阅读,读者可以对单片机课程设计中应用IIC总线式EEPROM存储器有一个全面的了解,并且可以借鉴其中的设计思想和方法。

相关推荐

381 浏览量

智慧安全方案

- 粉丝: 3847

- 资源: 59万+

最新资源

- pid控制器代码matlab-bobb:光束在光束平衡器上控制项目。有关更多详细信息,请参见dvernooy.github.io/projec

- java接口自动化案例

- css3 checkbox美化单选按钮和复选按钮美化样式

- 行业文档-设计装置-一种具有可移动风扇的笔记本散热器.zip

- cerbo:我的脑子里有什么

- awesome-farming:精心制作的一切的精选链接列表

- 德阁html.zip

- pid控制器代码matlab-Modeling-and-controlling-of-Electrical-DC-motor::在MATLAB

- 中国风创意书画展古风海报背景水墨书法

- CQL-Formatting-and-Usage-Wiki:一个协作工作区,用于开发用于工件开发的CQL格式约定和使用模式。 带有CQL示例的烹饪之家,请访问Wiki了解更多

- generation03

- jolloniego.github.io

- 像素:方格像素

- pid控制器代码matlab-Motor-PID-Controller-using-Arduino-Matlab:使用Arduino和Matl

- 牧场系统可视化系统 娱乐系统

- androidone:图形界面草图库,用于设计Android one应用程序