掌握TimeQuest:FPGA设计中的静态时序分析利器

需积分: 10 199 浏览量

更新于2024-07-22

收藏 2.6MB DOC 举报

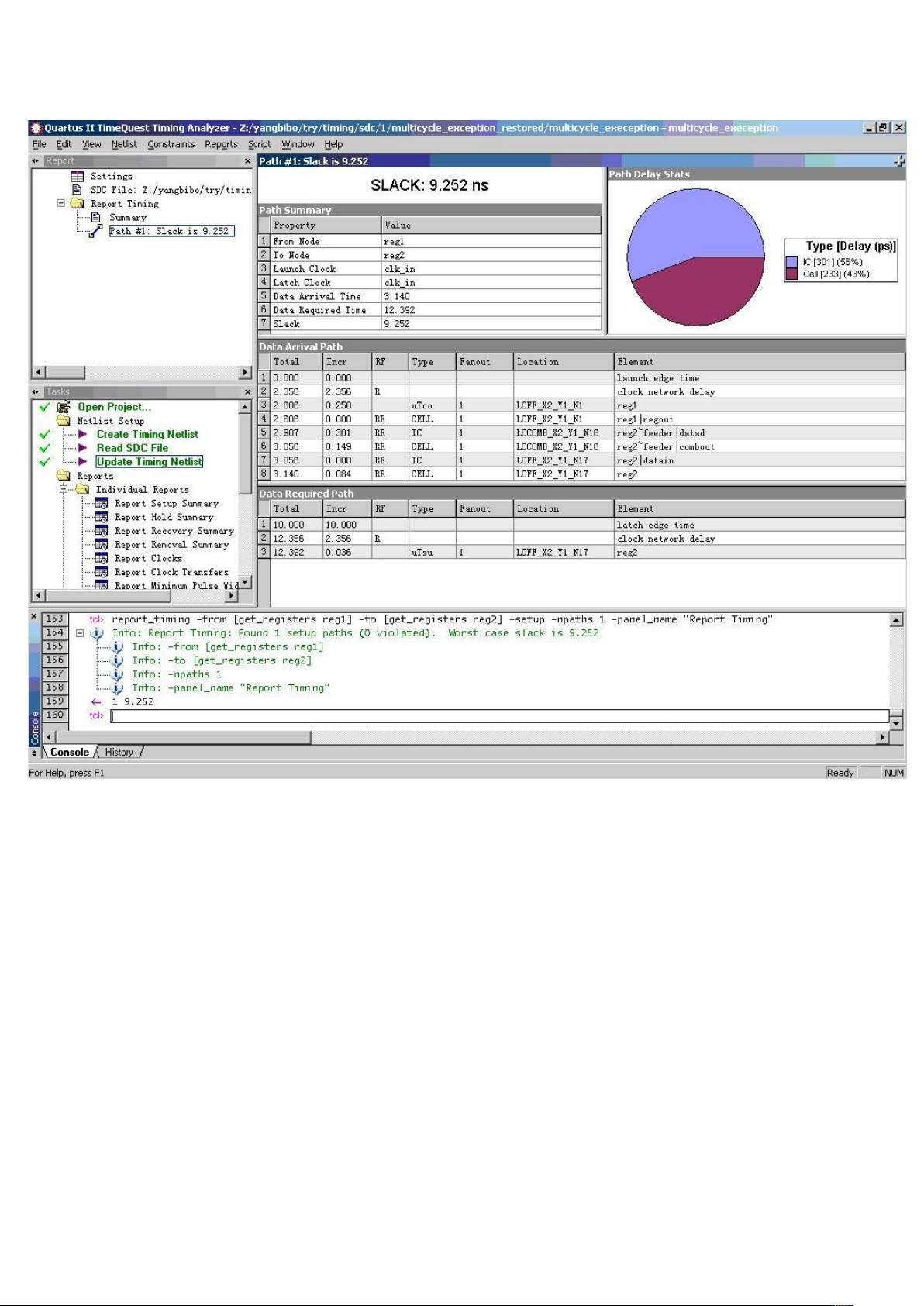

"TimeQuest是Altera公司推出的一款强大的静态时序分析工具,适用于FPGA设计,具有ASIC设计风格,并支持Synopsys Design Constraints (SDC)文件格式,相较于Timing Analyzer,它提供了更友好的界面和更精细的时序约束功能。时序分析在确保设计质量和性能优化中起到关键作用,尤其是在FPGA设计中,良好的时序约束能够指导布局布线,提升设计性能。TimeQuest的通用约束语言使得设计约束在FPGA和ASIC之间迁移更加方便。"

在FPGA设计中,TimeQuest的掌握至关重要,因为它可以帮助设计者进行详尽的时序分析,不仅确保设计的质量,还能让设计者深入理解其代码在硬件层面的表现。TimeQuest引入了ASIC设计中的静态时序分析概念,通过读取布局布线后的网表,分析其中的基本单元——细胞(Cells)、引脚(Pins)和网络(Nets),来评估设计的时序性能。

时序分析的基本概念包括:

1. 细胞(Cells):这是构成Altera器件的基础,如查找表、寄存器、IO单元、PLL和存储器块等。每个LE(Logic Element)可以视为一个Cell。

2. 引脚(Pins):细胞的输入输出接口。在TimeQuest中,引脚不直接代表器件的外部输入输出,而是内部LE的输入输出。

3. 网络(Nets):在细胞内,从输入引脚到输出引脚的连接路径。

TimeQuest使用SDC文件格式,这是一种行业标准,允许设计者创建更复杂的时序约束,这比Quartus II的QSF文件提供了更大的灵活性。这种通用性使得设计约束更容易在不同的设计流程之间转换,无论是从FPGA到ASIC,还是在不同FPGA项目之间。

通过使用TimeQuest,设计者可以更有效地控制时钟路径、数据路径和其他关键路径,确保设计满足时序收敛的要求。此外,TimeQuest的用户界面和报告功能便于理解时序违规,进行调试和优化。这对于FPGA设计初学者尤其有益,因为他们可以通过TimeQuest深入理解硬件描述语言的实现,以及综合工具如何处理这些语言,从而提升设计技能。

TimeQuest是FPGA开发中不可或缺的工具,它提供了一种强大的方法来理解和优化设计的时序特性,这对于确保设计的高效性和可靠性至关重要。通过熟练掌握TimeQuest,设计者可以更有效地利用Altera FPGA的性能潜力,同时也能为将来可能的ASIC设计打下坚实基础。

2021-08-10 上传

106 浏览量

318 浏览量

648 浏览量

182 浏览量

365 浏览量

king_tianya2

- 粉丝: 4

最新资源

- 普天身份证阅读器新版二次开发包发布

- C# 实现文件的数据库保存与导出操作

- CkEditor增强功能:轻松实现图片上传

- 掌握DLL注入技术:测试工具使用与探索

- 实现带节假日农历功能的jQuery日历选择器

- Spring循环依赖示例:深入理解与Git代码仓库实践

- ABB PLC液压阀门控制程序开发指南

- 揭秘4核旋风密版626象棋引擎的超牛实力

- HTML5实现的经典游戏:小霸王坦克大战源码分享

- 让Visual Studio兼容APM硬件信息的方法

- Kotlin入门:创建我的第一个应用

- Android语音识别技术研究报告与应用分析

- 掌握JavaScript基础:第8版教程源代码解析

- jQuery制作动态侧面浮动图片广告特效教程

- Android PinView仿支付宝密码输入框源码分析

- HTML5 Canvas制作的围住神经猫游戏源码分享