STM32F10x存储器与总线架构解析

需积分: 10 47 浏览量

更新于2024-09-05

收藏 188KB PDF 举报

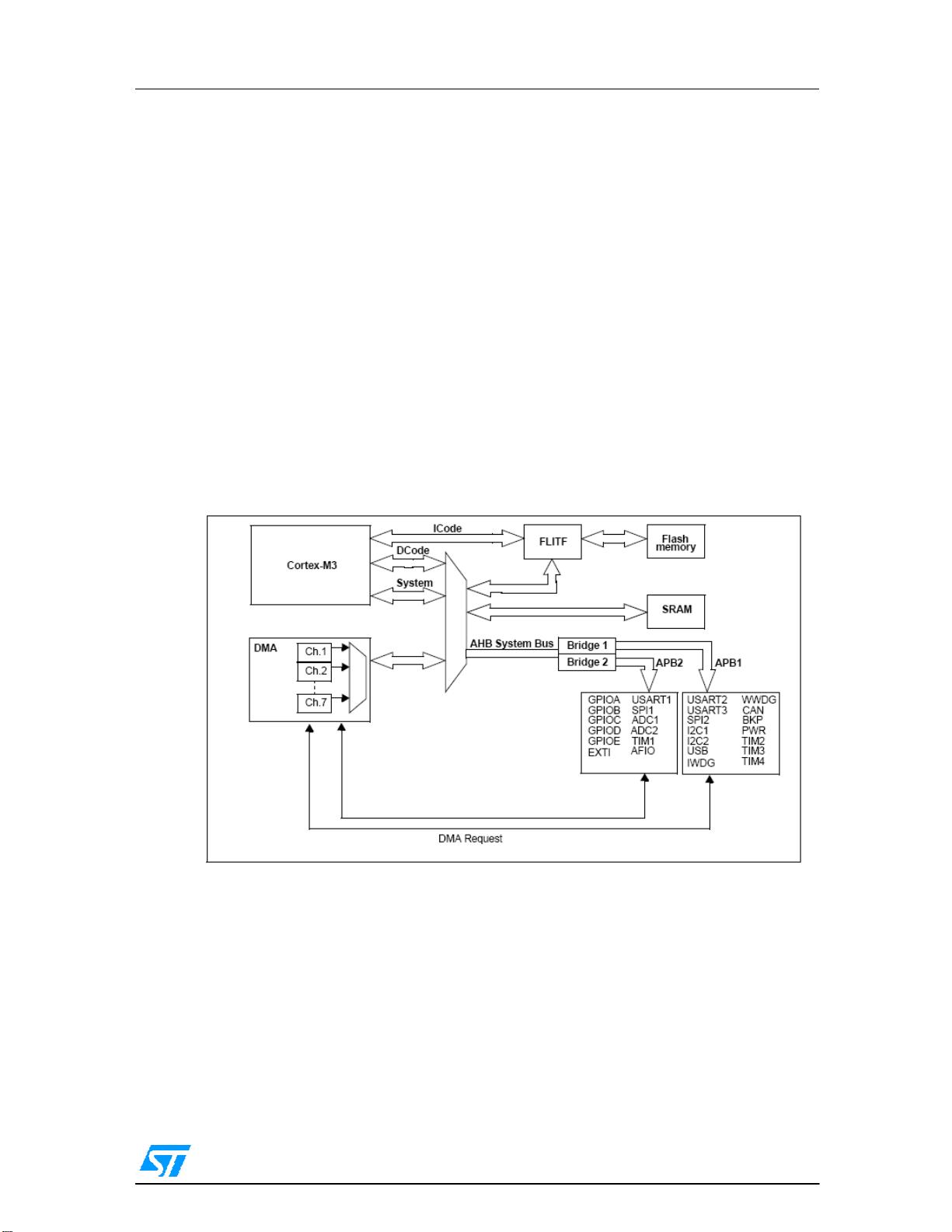

"STM32F10x参考手册详细介绍了微控制器的存储器和总线架构,包括I-bus, D-bus, S-bus, GP-DMA, 内部SRAM, 内部闪存存储器, AHB到APB的桥以及总线矩阵等关键组件的相互连接和功能。"

STM32F10x系列是意法半导体(ST)推出的一款基于Cortex-M3内核的微控制器,其存储器和总线架构是其核心设计之一,确保高效的数据传输和处理。

1. **系统架构**

- 系统架构由四个驱动单元和三个被动单元组成。驱动单元包括Cortex-M3的I-bus(用于指令)、D-bus(用于数据)、S-bus(系统总线)以及GP-DMA(通用直接内存访问)。被动单元包含内部SRAM、内部闪存存储器以及AHB到APB桥,这些组件通过多级AHB总线架构相连。

2. **总线系统**

- **I-bus**:连接Cortex-M3内核的指令总线和Flash指令接口,用于预取指令。

- **D-bus**:连接Cortex-M3的DCode总线和闪存存储器,处理常量加载和调试访问的数据传输。

- **S-bus**:连接Cortex-M3的系统总线到总线矩阵,使得内核可以访问外设。

- **DMA总线**:连接DMA控制器到总线矩阵,协调CPU和DMA对SRAM、闪存和外设的访问。

- **总线矩阵**:管理I-bus、S-bus和DMA总线之间的访问仲裁,采用轮换算法,包含三个驱动部件和三个被动部件。

3. **AHB到APB桥**

- AHB到APB桥(AHB/APB Bridge)有两个,它们在高速AHB总线和两个APB总线之间建立同步连接。APB1的工作频率限制为36MHz,而APB2则工作在最高72MHz的全速。

4. **AHB和APB外设**

- AHB总线上的外设通过总线矩阵与系统总线相连,允许DMA访问。APB总线则服务于低速或中速的外设,如定时器、串行接口等。

5. **地址映射**

- 不同的外设根据其功能和性能需求被分配到不同的总线,具体的地址映射可以在第1章找到,这对于理解和编程这些外设至关重要。

STM32F10x的这种存储器和总线架构设计使得它可以高效地处理复杂的实时任务,同时通过AHB和APB总线支持多种外设,满足各种嵌入式应用的需求。了解这一架构对于开发者来说,是充分利用STM32F10x功能并优化系统性能的关键。

2021-05-06 上传

2012-01-02 上传

2021-05-14 上传

2022-12-02 上传

2020-10-19 上传

2021-10-01 上传

2019-09-13 上传

2011-04-17 上传

weixin_38744153

- 粉丝: 347

- 资源: 2万+

最新资源

- 基于Python和Opencv的车牌识别系统实现

- 我的代码小部件库:统计、MySQL操作与树结构功能

- React初学者入门指南:快速构建并部署你的第一个应用

- Oddish:夜潜CSGO皮肤,智能爬虫技术解析

- 利用REST HaProxy实现haproxy.cfg配置的HTTP接口化

- LeetCode用例构造实践:CMake和GoogleTest的应用

- 快速搭建vulhub靶场:简化docker-compose与vulhub-master下载

- 天秤座术语表:glossariolibras项目安装与使用指南

- 从Vercel到Firebase的全栈Amazon克隆项目指南

- ANU PK大楼Studio 1的3D声效和Ambisonic技术体验

- C#实现的鼠标事件功能演示

- 掌握DP-10:LeetCode超级掉蛋与爆破气球

- C与SDL开发的游戏如何编译至WebAssembly平台

- CastorDOC开源应用程序:文档管理功能与Alfresco集成

- LeetCode用例构造与计算机科学基础:数据结构与设计模式

- 通过travis-nightly-builder实现自动化API与Rake任务构建