Vivado入门:流水灯实战与自制IP设计

需积分: 42 5 浏览量

更新于2024-07-18

4

收藏 6.62MB PDF 举报

本资源是一份关于使用Vivado进行基础实验的教程,主要目标是帮助学习者通过实践设计一个简单的流水灯电路。Vivado是一个由Xilinx公司推出的高级设计套件,它集成了高度集成的设计环境,支持从系统级到集成电路级别的设计,采用AMBA AXI4互连规范、IP-XACT封装元数据等开放标准,旨在简化设计流程并满足定制化需求。

在本次实验中,核心内容包括以下几个部分:

1. **Vivado基础**:

- 学习者将使用Vivado 2015.4版本,这是一款功能强大的FPGA设计工具,能够处理大规模的等效ASIC门设计。

- 实验涉及到的主要工具和技术有Verilog HDL语言,这是硬件描述语言,用于编写FPGA的逻辑设计。

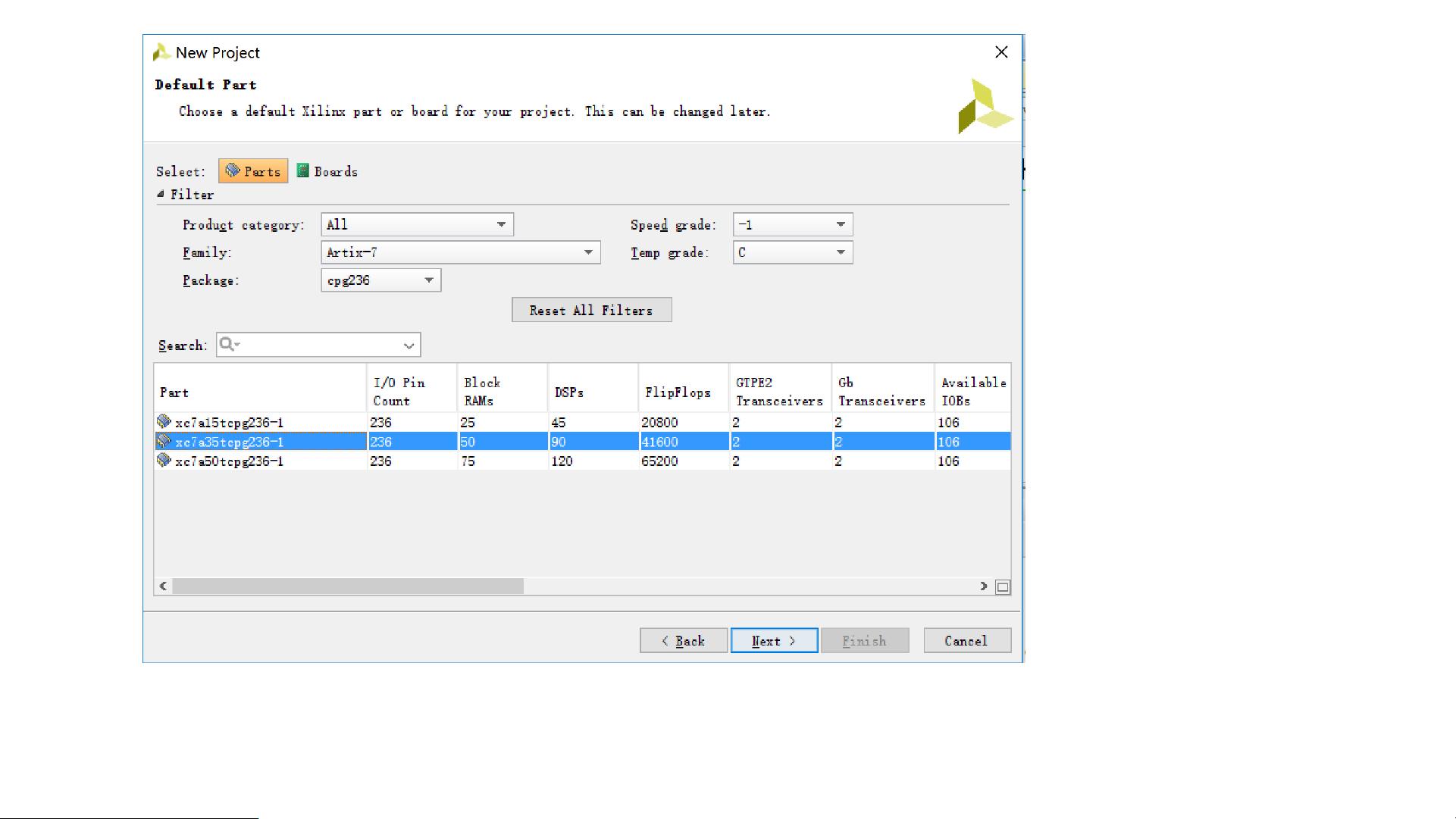

2. **BASYS3平台**:

- 基于Digilent的BASYS3 FPGA开发板作为实验平台,它搭载了Xilinx Artix-7 FPGA,拥有丰富的I/O资源,如5200个逻辑切片、1800KB快速块RAM、5个PLL时钟管理模块等,适合初学者入门。

3. **实验内容**:

- 学习者将亲手制作一个8进制减计数器IP核,这是流水灯电路的关键组成部分,用于控制灯的亮灭顺序。

- 实验设计流程涉及分频器设计,用于精确控制灯的切换频率;译码器设计,将计数器的结果转化为特定灯的点亮信号。

- 顶层模块设计则是将各个子模块整合成完整的电路,实现灯的逐个点亮和熄灭。

- 除了硬件设计,还包括软件仿真,确保设计的正确性。

- 最后,学习者将进行电路的综合、实现与下载,将设计部署到实际硬件上。

4. **电路原理图**:

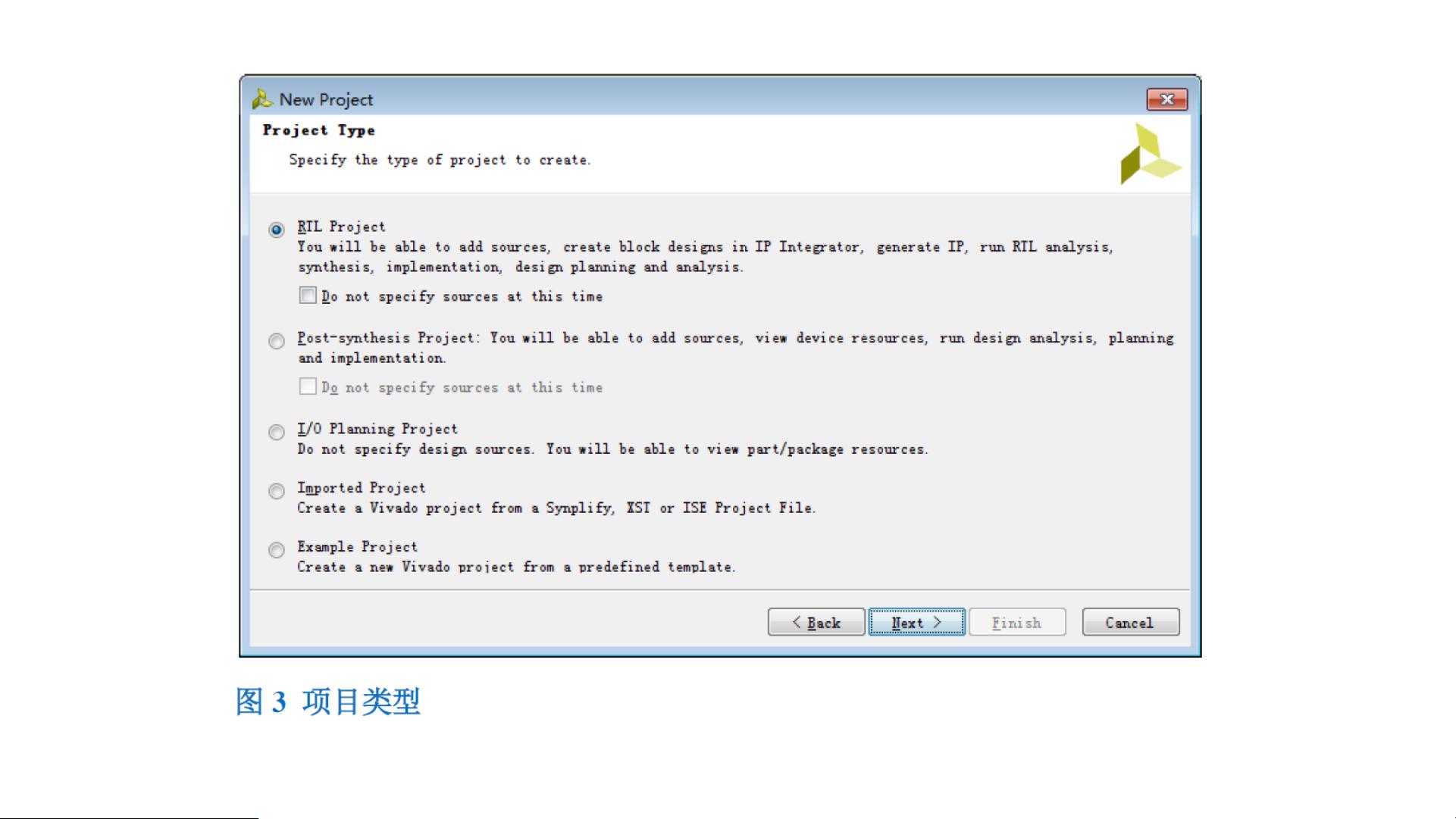

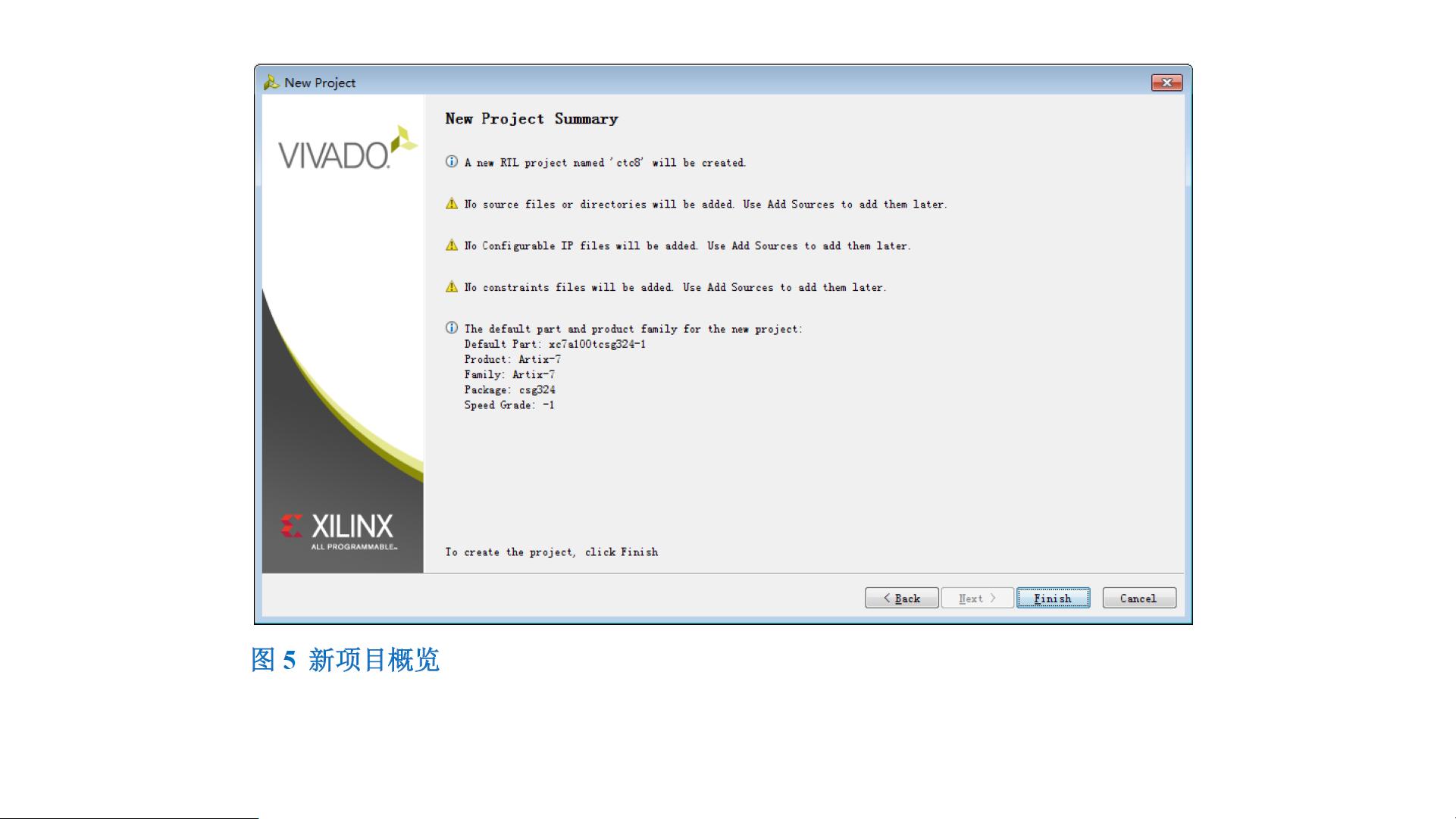

- 在制作IP核的过程中,会引导学习者如何在Vivado中创建新项目,并配置所需的FPGA型号,例如BASYS3。

整个实验不仅涵盖了基础的硬件设计和软件仿真,还锻炼了学习者自定义IP核的能力,有助于理解和掌握Vivado工具的使用,提升FPGA设计的实际操作技能。通过这个项目,学习者可以深入理解数字逻辑设计的基本原理,并建立起从概念到实物的连接。

2020-06-25 上传

2022-09-24 上传

2023-06-15 上传

2017-11-13 上传

2019-05-11 上传

2022-09-14 上传

2018-12-16 上传

liyf67

- 粉丝: 3

- 资源: 4

最新资源

- 单片机和图形液晶显示器接口应用技术

- 医院计算机管理信息系统需求分析和实施细则

- DS1302 涓流充电时钟保持芯片的原理与应用

- C++C代码审查表 文件结构

- 330Javatips

- Linux环境下配置同步更新的SVN服务器(word文档)

- C# 编码规范和编程好习惯

- DELPHI串口通讯实现

- 《Linux 内核完全注解》 赵炯

- Que-Linux-Socket-Programming.pdf

- VMware Workstation使用手册

- jsp texiao test

- Struts in action 中文版

- 基于uml的工作流管理系统分析

- Oracle9i数据库管理实务讲座

- arm指令集arm指令集