Different signals generated by the resistor bridge vary in

amplitude due to different times of operations, which

worsens differential nonlinearity of the Ph-ADC. (2) A

large amount of transconductance cells are required to

drive the resistor bridge, leading to much current con-

sumption. The total current consumption reported in [10]is

290 lA. (3) Critical matching is needed in the resistor

bridge. Larger resistors are neces sary for better matching,

which leads to higher chip area.

In [12], a current mirror based combiner for Ph-ADC is

proposed, as shown in Fig. 2(b). The phase quantization is

fulfilled by different sizes of current mirrors. This structure

avoids the amplitude variation problem in resistor bridge

combiners. However, there is a trade-off between power

and matching, which still comes as a design challenge.

Larger current mirror sizes face fewer matching problems,

yet may increase chip area and introduce more parasitic

effects, limiting circuit speed in a power-constrained

design.

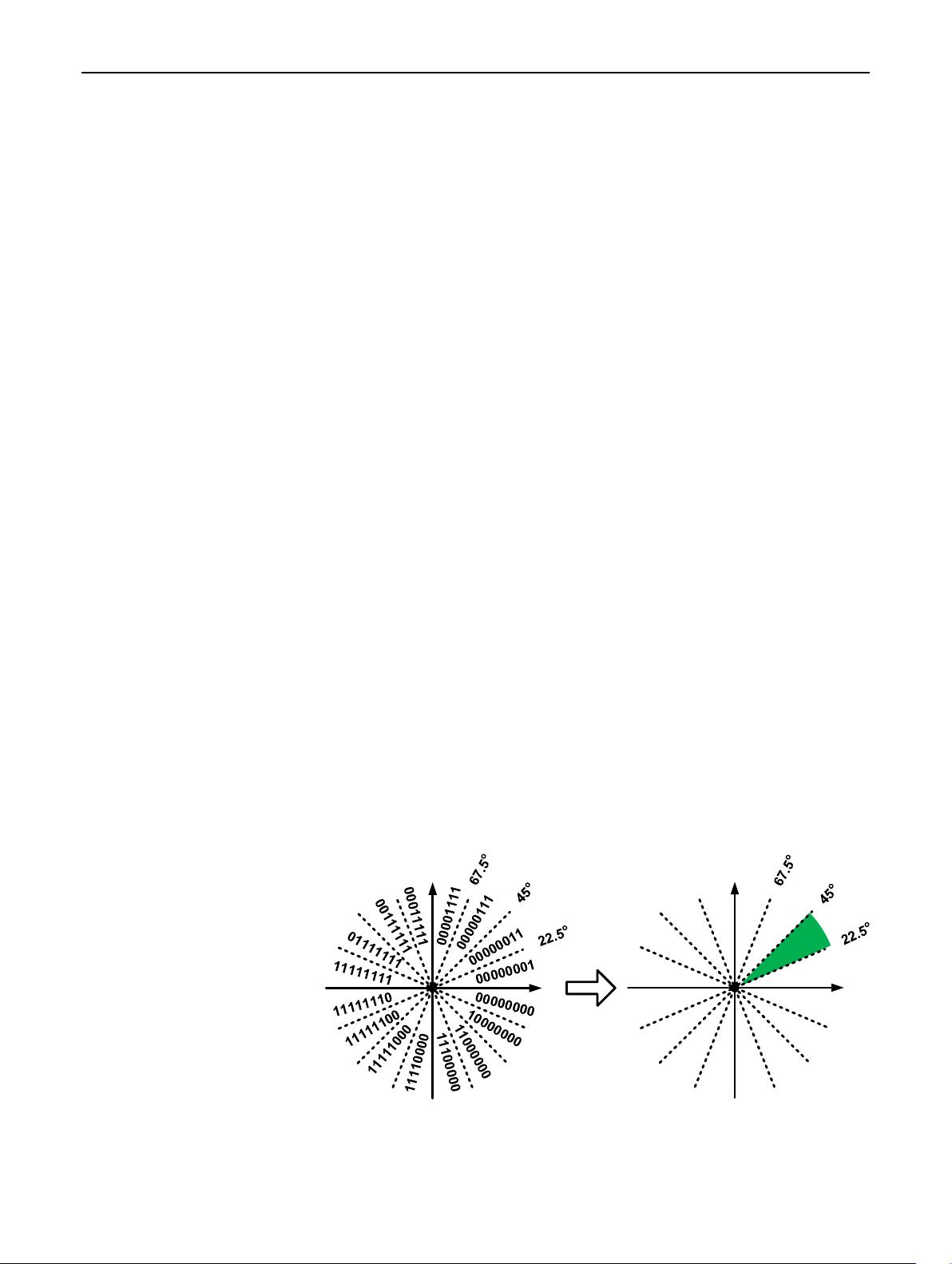

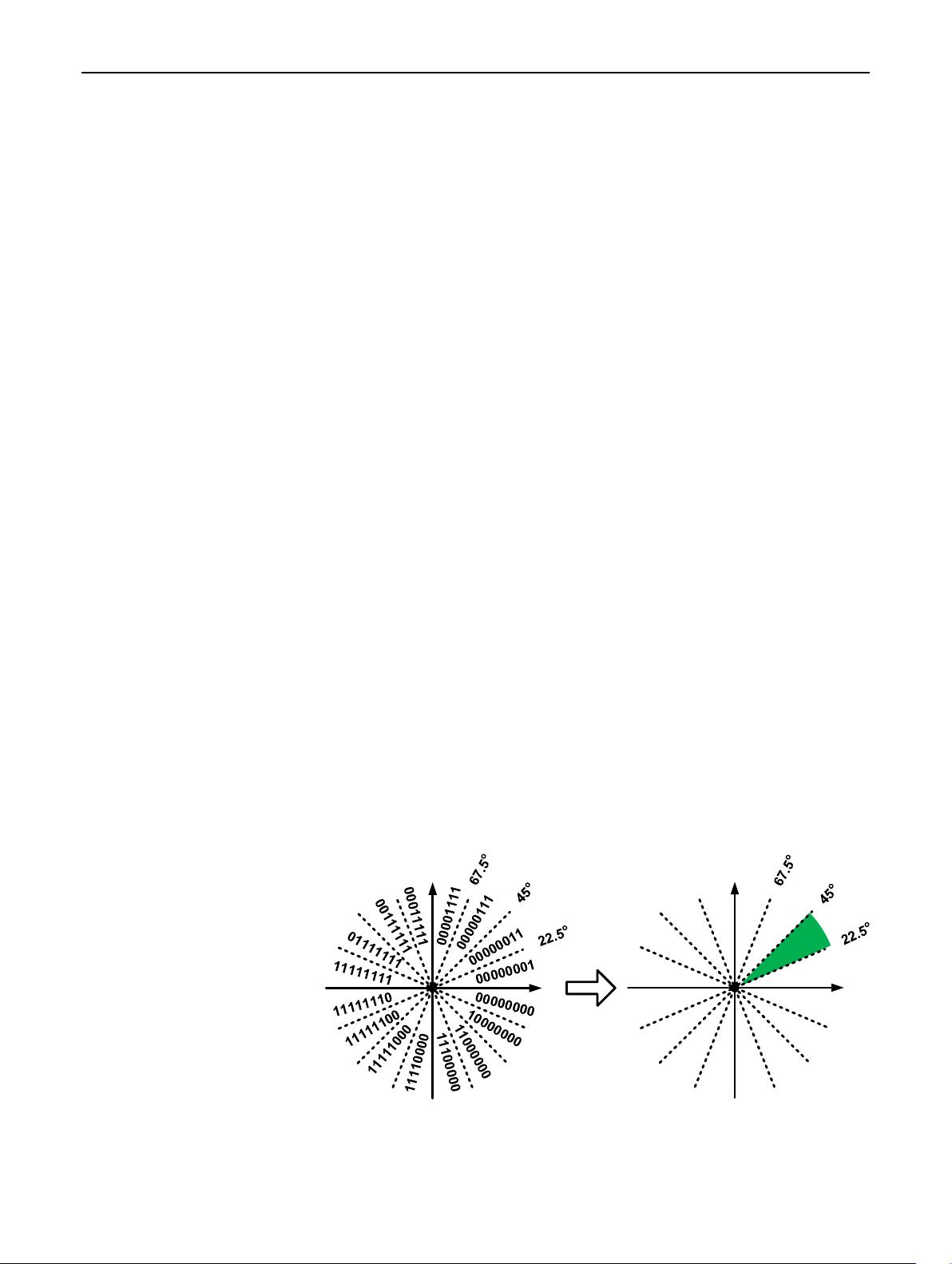

In both resistor bridge based Ph-ADCs and current

mirror based Ph-ADCs, 8 thermometer coded output bits

[Fig. 3(a)] are gener ated simultaneously for each input

sample, which is similar to the amplitude flash ADCs. A

large number of resistor/current elements and comparators

are required inevitably. For example, the current mirror

based Ph-ADC in [12] employs 260 current elements and 8

comparators, which results in excessive power consump-

tion. A charge redistribution Ph-ADC based on an IQ-as-

sisted conversion algorithm is proposed in [13, 14], which

avoids the use of combiner. Power is reduced compared to

[10] and [12]. However, 4 comparators are utilized in

[13, 14], which still leaves room for optimization.

To achieve a good trade-off between quantization speed/

accuracy and circuit complexity, a multi-step Ph-ADC is

proposed in this work. The multi-step conversion is similar

to the idea in successive-approximation (SAR) ADC with

good power/speed efficiency [16]. With multi-step

conversion, the proposed Ph-ADC requires only 52 current

elements and 1 comparator.

2.2 Operation principle of proposed Ph-ADC

architecture

In the proposed Ph-ADC, the complex plane is equally

divided into 16 sections. The phase resolution is 22.5 and

the trip points on the ADC transfer curve are given by

u

n

= n 22.5 (0 B n B 15), as shown in Fig. 3(b). The

22.5 resolution is enough to detect 90 phase rotation

according to the BLE protocol.

In conventional Ph-ADCs, 8 b its thermometer codes are

adopted for quantization, as shown in Fig. 3(a). 8 bits

thermometer codes require 8 parallel comparators or one

comparator which operates 8 times serially. To reduce the

number of comparing operation, 4 bits binary-weighted

codes are proposed in this paper, which is shown in

Fig. 3(b). The bit definition is given in Table 1, where

m and k are integers.

By definition, tan U

IF

= Q/I = (V

QP

- V

QN

)/(V

IP

-

V

IN

), where U

IF

is the phase of the IF sign al.

1. The trip points where B

3

alters between 0 and 1 are

U

IF

= 90 or 270. At these trip points, V

IP

-

V

IN

= 0, and bit B

3

can be determined by comparing

V

IP

with V

IN,

as shown in Fig. 4(a).

2. The trip points where B

2

alters between 0 and 1 are

U

IF

= 0 or 180. At these trip points, V

QP

- V

QN

= 0,

and bit B

2

can be determined by comparing V

QP

with

V

QN

, as shown in Fig. 4 (b).

3. The trip points where B

1

alters between 0 and 1 are

U

IF

= (2 m ? 1) 45. At these trip points, (V

QP

-

V

QN

)/(V

IP

- V

IN

) = tan (2m ? 1) 45 = 1or-1,

depending on the values of B

3

and B

2

. Thus, bit B

1

can

be determined by comparing the absolute value of

1111

1110

1101

1100

0100

0101

0110

0111

0011

0010

0001

0000 1000

1001

1010

1011

I

Q

Q

I

(a) (b)

Fig. 3 a Thermometer code in

conventional Ph-ADCs.

b Binary code in proposed SAR

Ph-ADC

Analog Integrated Circuits and Signal Processing (2018) 94:49–63 51

123