数字逻辑设计:电子密码锁倒计时系统

需积分: 0 54 浏览量

更新于2024-06-30

1

收藏 1.09MB DOCX 举报

"本次大作业是关于数字逻辑与数字系统设计的一个实验项目,设计一个具有显示倒计时和自定义密码功能的电子密码锁。学生需要利用所学的数字逻辑知识,如计数器、触发器和译码电路,通过EGO1开发板和Vivado集成开发环境来实现。设计要求包括密码输入、时间限制、自动复位和报警功能,以及可能的附加功能。系统由输入控制、时钟分频、比较修改和译码显示四个主要模块组成。"

在本次数字逻辑大作业中,学生需要设计的电子密码锁涉及到多个关键知识点:

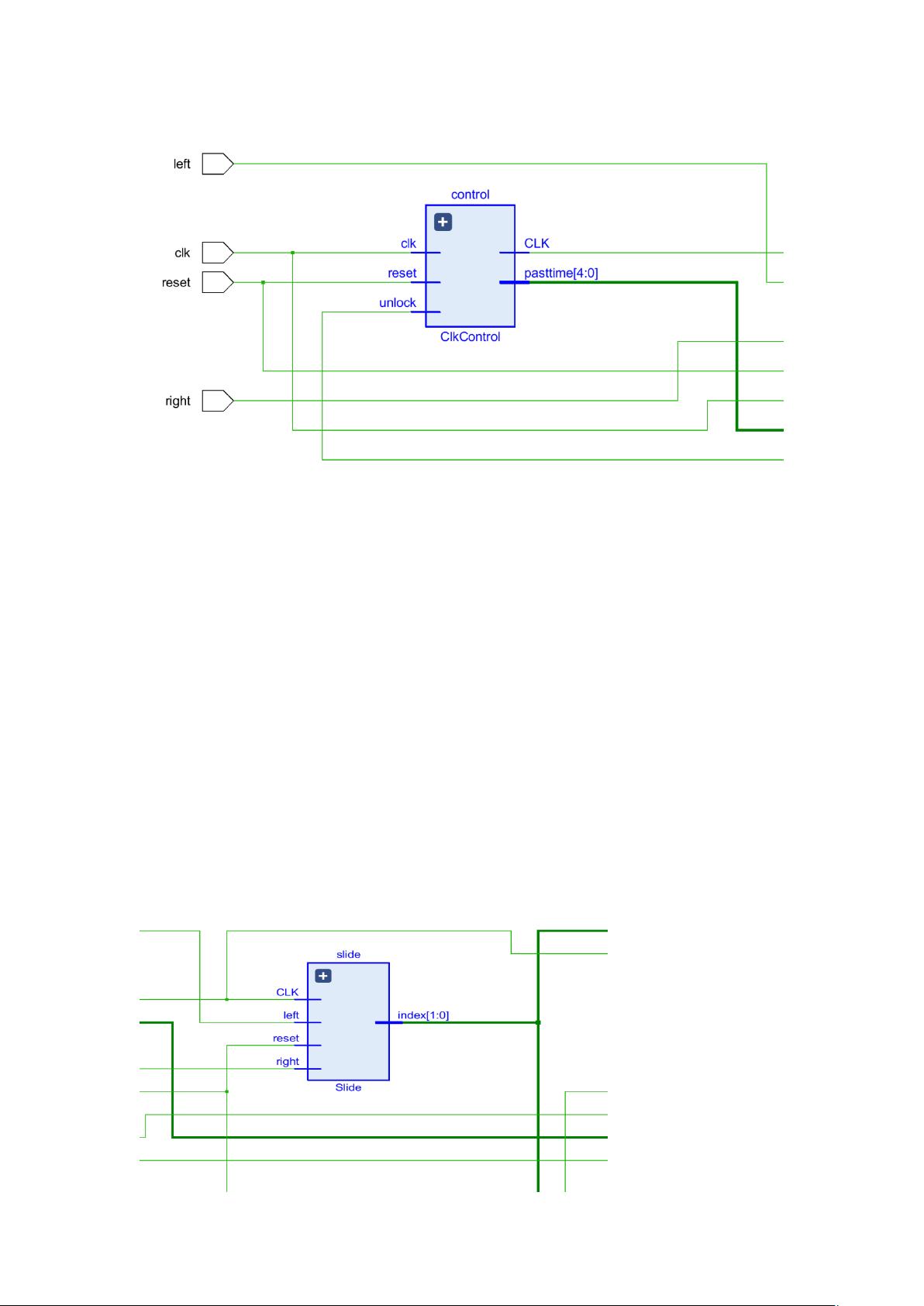

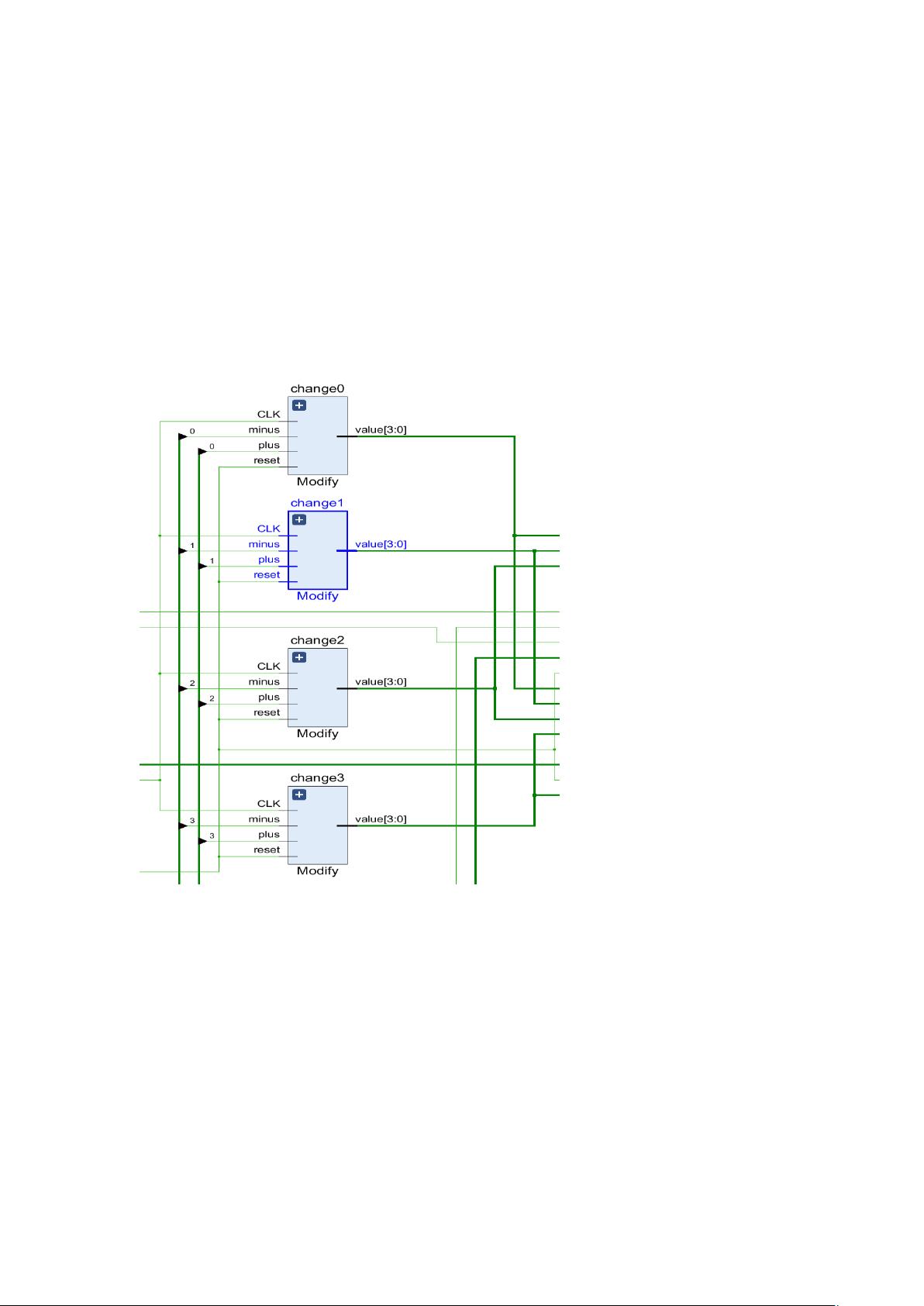

1. **输入控制模块**:这个模块处理用户的输入,包括按键S0-S4的操作,支持加、减、左移位、右移位和确认。这里的移位操作是通过模4计数器实现,而加减操作则需要模10计数器。R1和N4开关分别用于选择操作模式和重置密码锁。

2. **时钟分频模块**:该模块负责从100MHz的主时钟生成20Hz和1Hz的子时钟。20Hz时钟用于用户交互,1Hz时钟则用于30秒倒计时的计数。

3. **比较修改模块**:在30秒内,如果模式开关(mode)设定为0,系统会对比输入与密码,未匹配则允许继续输入;当mode为1时,系统允许修改密码。超过30秒或者成功解锁后,此模块停止接收新的输入。

4. **译码显示模块**:此模块将密码和倒计时转换为七段数码管的段码,通过分时显示技术将它们可视化。它需要能够处理十进制数值,并根据位码调整显示内容。

5. **模块化设计**:整个系统被划分为8个子模块,如Operate、ClkControl、Slide、Modify、Valuetodiode和Lightdi等,每个模块都有明确的功能,这体现了模块化设计思想,便于代码的组织和维护。

6. **Vivado集成开发环境**:这是一个用于硬件描述语言(HDL)编程的工具,支持Verilog或VHDL,用于设计、仿真和实现FPGA(Field-Programmable Gate Array)项目。

7. **EGO1开发板**:这是一个实验平台,提供了硬件接口和资源,如按键、数码管显示和时钟信号,用于实现数字逻辑设计。

通过这个项目,学生不仅能巩固数字逻辑的基础知识,还能提升实际工程设计和问题解决能力,包括硬件描述语言编程、逻辑设计、时序分析和硬件调试等。

2023-05-12 上传

2023-11-27 上传

2023-11-17 上传

2023-07-31 上传

2023-10-21 上传

2023-05-14 上传

柔粟

- 粉丝: 33

- 资源: 304

最新资源

- 彩虹rain bow point鼠标指针压缩包使用指南

- C#开发的C++作业自动批改系统

- Java实战项目:城市公交查询系统及部署教程

- 深入掌握Spring Boot基础技巧与实践

- 基于SSM+Mysql的校园通讯录信息管理系统毕业设计源码

- 精选简历模板分享:简约大气,适用于应届生与在校生

- 个性化Windows桌面:自制图标大全指南

- 51单片机超声波测距项目源码解析

- 掌握SpringBoot实战:深度学习笔记解析

- 掌握Java基础语法的关键知识点

- SSM+mysql邮件管理系统毕业设计源码免费下载

- wkhtmltox下载困难?找到正确的安装包攻略

- Python全栈开发项目资源包 - 功能复刻与开发支持

- 即时消息分发系统架构设计:以tio为基础

- 基于SSM框架和MySQL的在线书城项目源码

- 认知OFDM技术在802.11标准中的项目实践