FPGA SDRAM操作详解:初始化与读写步骤

"本文详细介绍了FPGA如何操作SDRAM,包括初始化步骤、读写操作以及相关的时序控制。"

在FPGA设计中,SDRAM(Synchronous Dynamic Random Access Memory)是一种常用的高速存储器,它的所有操作都严格同步于时钟。SDRAM的使用涉及到一系列复杂的初始化、预充电、刷新和模式寄存器设置等步骤,以及严格的时序控制。

首先,SDRAM的初始化至关重要。在电源稳定后,需要等待约200微秒的延时,这个期间可以通过计数器来实现,并发送NOP(No Operation)命令。接着,执行全银行预充电,即对所有L-BANK发送预充电命令,保持一个时钟周期,然后返回NOP状态。随后,进行8次刷新周期,每个刷新周期通常需要6个时钟周期,但具体数值可能因芯片型号而异。模式寄存器设置(MRS)用于设定SDRAM的工作模式,其设置码根据不同的SDRAM芯片有所不同,设置完成后需等待一定时钟周期,具体时钟数量依据芯片规格书。

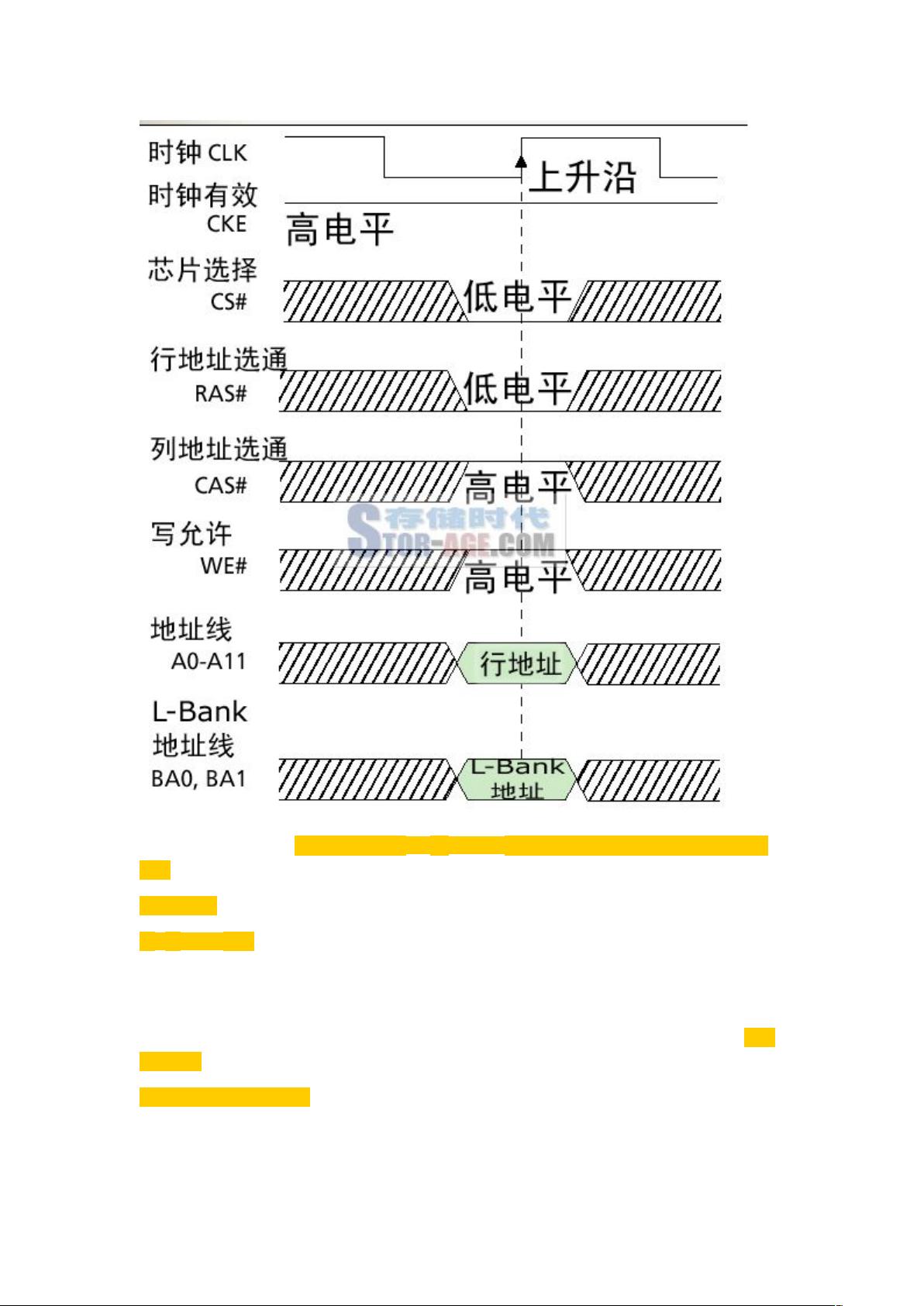

进入读写操作前,SDRAM需要先激活一行,这通过写入行有效命令完成。此命令与CS(Chip Select)和L-Bank的地址线信号同时发出,且写信号需为高电平。之后,遵循tRCD(Row Address Strobe to Column Address Strobe Delay)延时,即从行有效到列有效之间的间隔,这个时间段内应发送NOP命令。tRCD是根据SDRAM内部存储阵列的响应时间设定的。

读写操作的核心在于列地址的有效化。在tRCD延时结束后,读写命令和地址信号同时发出,只是#WE(Write Enable)信号区分读写操作:#WE为低表示写操作,反之为读操作。值得注意的是,读操作在CAS(Column Address Strobe)命令发出后,还需要等待CL(CAS Latency)个时钟周期才能得到数据。CL分为两部分,一是数据在存储体中响应的时间,二是数据传输至S-AMP(Sense Amplifier)并准备好输出的时间,即tAC(Access Time from CAS)。

FPGA对SDRAM的控制涉及多步时序操作,需要精确地按照芯片的数据手册进行,确保时序正确,以保证数据的准确读写和SDRAM的稳定工作。理解并掌握这些知识点对于FPGA开发者来说是至关重要的,因为它们直接影响到系统的性能和可靠性。

2022-09-15 上传

2022-09-22 上传

2022-09-20 上传

2022-09-23 上传

2022-09-24 上传

2014-04-05 上传

2022-09-14 上传

2022-07-14 上传

2015-03-17 上传

WESTMULAN

- 粉丝: 1

- 资源: 6

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍