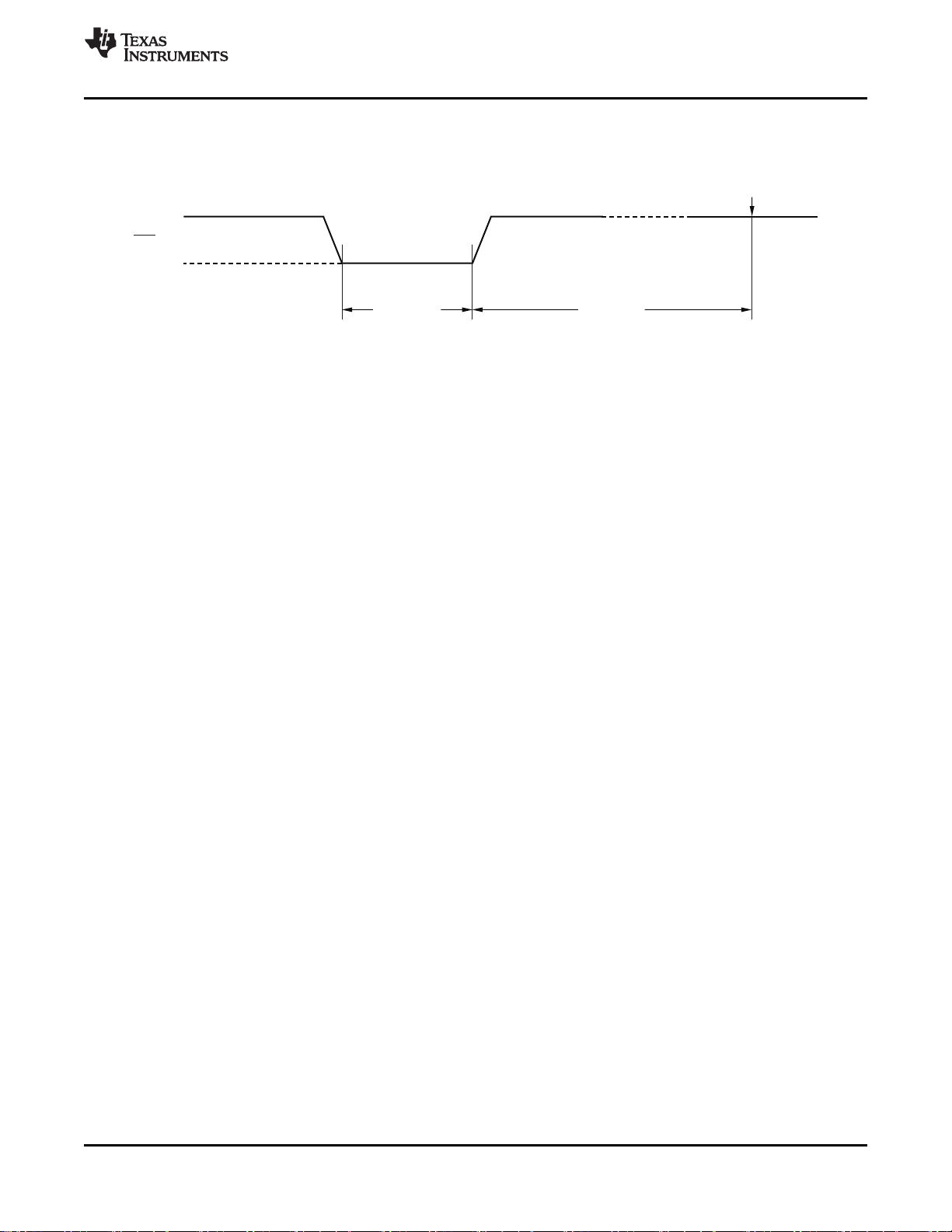

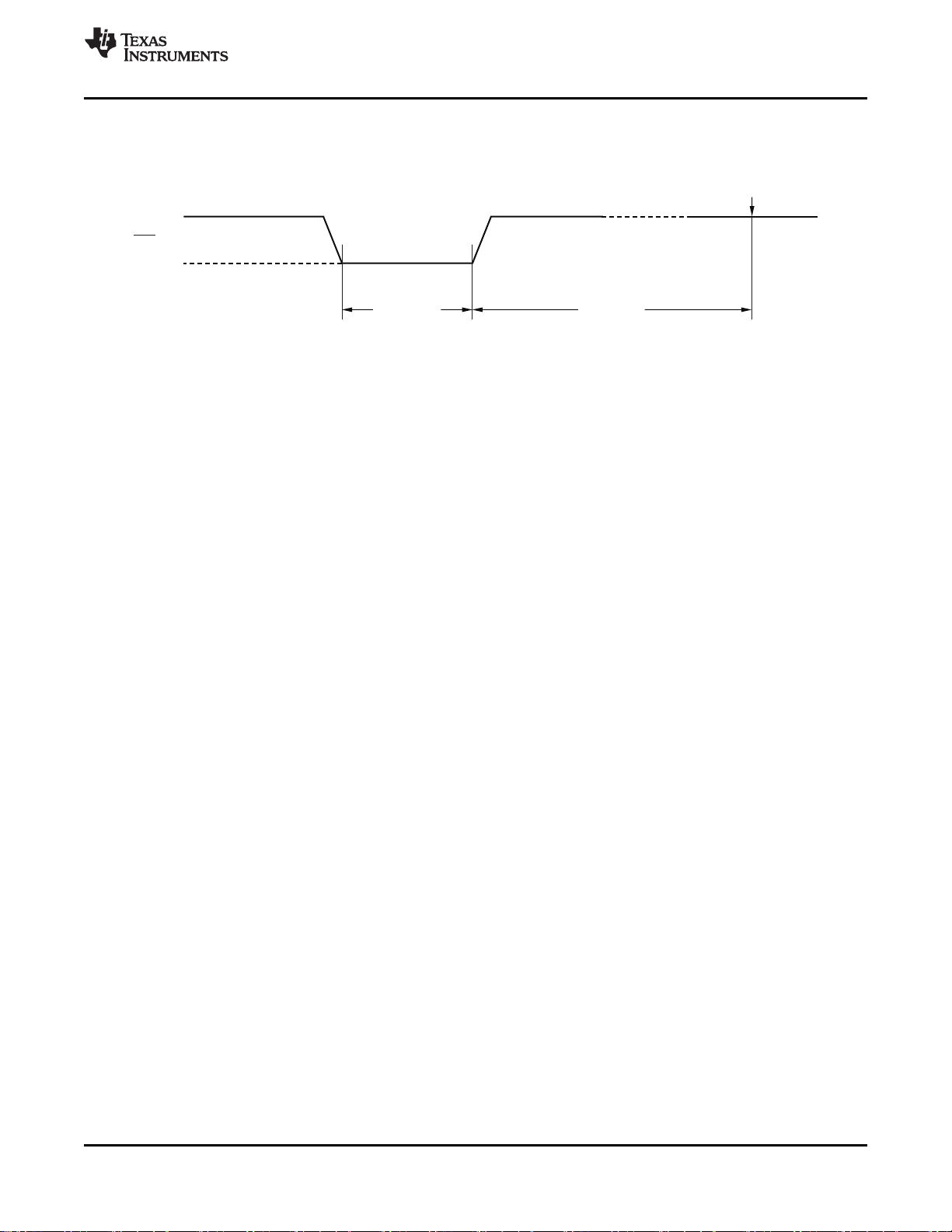

RST

0

1

500ns (min)

500 sm (min)

Write orRead

via

S IorP I C

2

13

DIX4192

www.ti.com.cn

ZHCSG80F –FEBRUARY 2006–REVISED SEPTEMBER 2016

Copyright © 2006–2016, Texas Instruments Incorporated

Feature Description (continued)

Figure 6. Reset Sequence Timing

9.3.2 Master and Reference Clocks

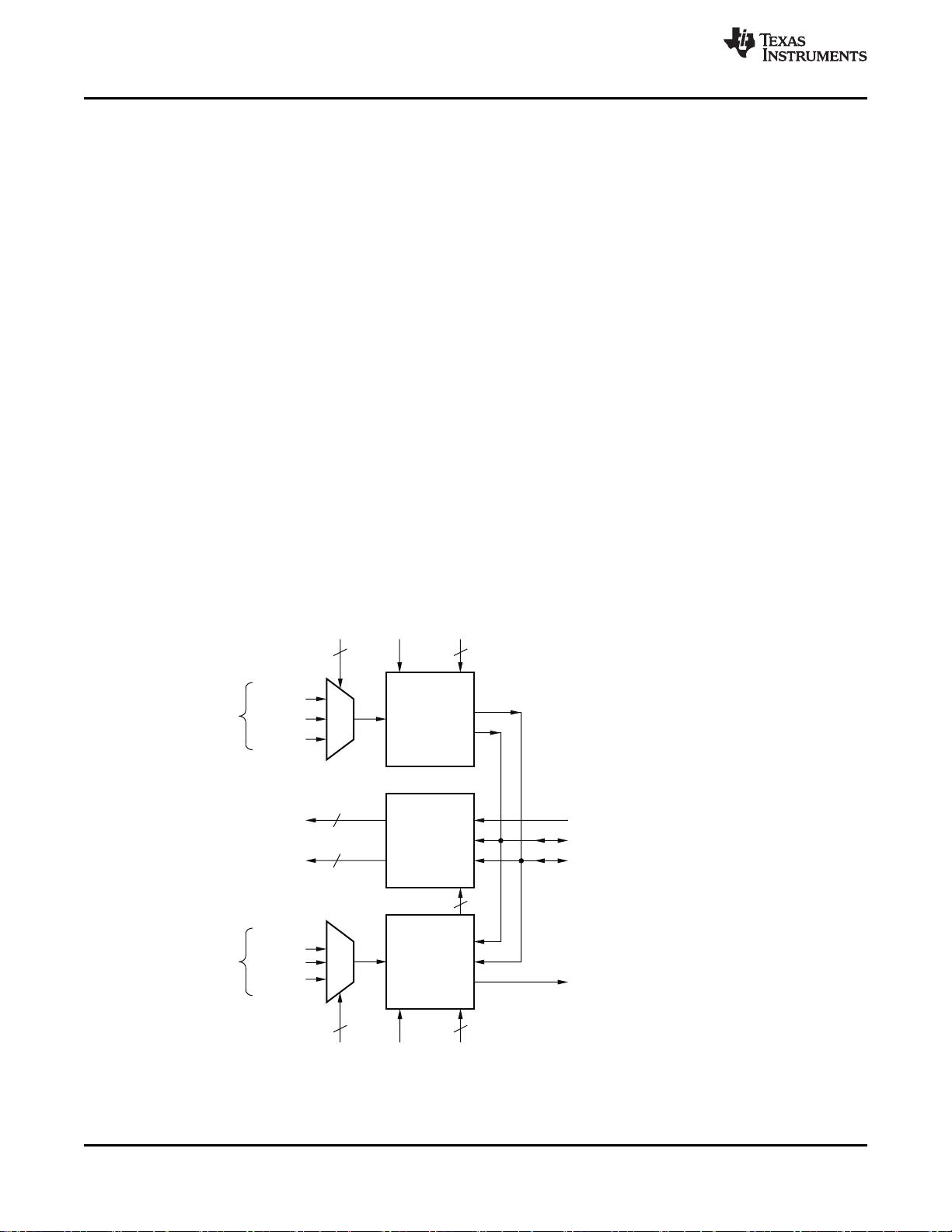

The DIX4192 includes two clock inputs, MCLK (pin 25) and RXCKI (pin 13). The MCLK clock input is typically

used as the master clock source for the audio serial ports and/or the DIT. The MCLK may also be used as the

reference clock for the DIR. The RXCKI clock input is typically used for the DIR reference clock source, although

it may also be used as the master or reference clock source for the audio serial ports.

In addition to the MCLK and RXCKI clock sources, the DIR core recovers a master clock from the AES3-

encoded input data stream. This clock is suitable for use as a master or system clock source in many

applications. The recovered master clock output, RXCKO (pin 12), may be used as the master or reference clock

source for the audio serial ports and the DIT, as well as external audio devices.

The master clock frequency for the audio serial ports (Port A and Port B) depends on the Slave or Master mode

configuration of the port. In Slave mode, the ports do not require a master clock because the left/right word and

bit clocks are inputs, sourced from an external audio device serving as the serial bus timing master. In Master

mode, the serial ports derive the left/right word and bit clock outputs from the selected master clock source,

MCLK, RXCKI, or RXCKO. The left/right word clock rate is derived from the selected master clock source using

one of four clock divider settings (divide by 128, 256, 384, or 512). Refer to Audio Serial Port Operation for

additional details.

The DIT always requires a master clock source, which may be either the MCLK input, or the DIR recovered clock

output, RXCKO. Like the audio serial ports, the DIT output frame rate is derived from the selected master clock

using one of four clock divider settings (divide-by-128, -256, -384, or -512). Refer to Digital Interface Transmitter

(DIT) Operation for additional details.

The DIR reference clock may be any frequency that meets the PLL1 set-up requirements, described in Control

Registers. Typically, a common audio system clock rate, such as 11.2896 MHz, 12.288 MHz, 22.5792 MHz, or

24.576 MHz, may be used for this clock.

TI recommends that the clock sources for MCLK and RXCKI input be generated by low-jitter crystal oscillators for

optimal performance. In general, phase-locked loop (PLL) clock synthesizers must be avoided, unless they are

designed or specified for low clock jitter.