半导体存储器设计与计算

需积分: 2 53 浏览量

更新于2024-09-07

3

收藏 433KB DOCX 举报

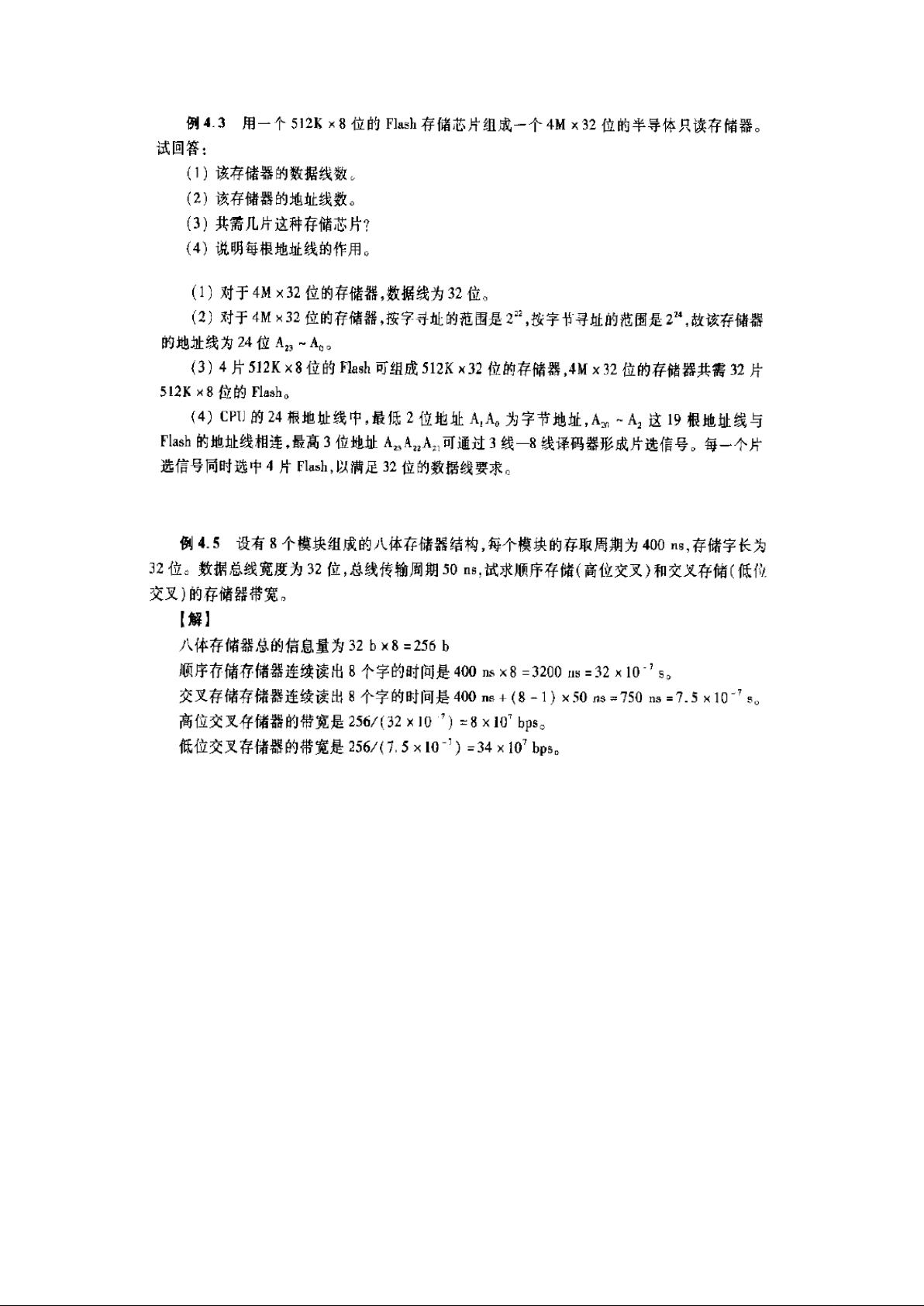

本文档主要讨论了存储器的相关知识,包括存储器的组成、地址线和数据线的数量、存储器的寻址方式以及不同类型的存储器的存取速度。通过两个具体的例子,例4.3和例4.5,解释了如何计算存储器的组成部分以及如何评估存储器带宽。

在例4.3中,讨论了一个用512K×8位的Flash存储芯片构建4M×32位半导体只读存储器的问题。首先,对于4M×32位的存储器,数据线为32位,意味着每次可以读写32位数据。其次,地址线总数为24位,其中最低两位A0和A1用于字节寻址,中间19位A2到A18用于直接连接到Flash芯片的地址线,最后三位As到A21通过3线-8线译码器生成片选信号,每片选信号选择4片Flash,共计需要32片来达到32位数据宽度的要求。

在例4.5中,涉及到了一个八体交叉存储器结构,每个模块的存取周期为400ns,存储字长为32位。数据总线宽度也是32位,总线传输周期为50ns。这里讨论了两种存储方式的带宽计算:顺序存储(高位交叉)和交叉存储(低位交叉)。顺序存储时,数据传输速率受到最慢模块的限制,即400ns;而交叉存储利用总线在不同模块间交替传输数据,可以显著提高带宽。

此外,文档还提到了一些基本的存储器知识,如9根地址线对应2^9=512个地址,8根数据线,1根片选线,1根读写线,总共19根线构成的基本存储单元。同时,区分了寻道速度和数据传输速度的区别,强调磁盘转速提高只影响数据传输速度,不改变寻道速度。在存储器速度比较中,给出了Cache、主存、寄存器和辅存的存取速度排名,其中寄存器的存取速度最快。存储周期是指连续读或写操作所允许的最短间隔时间,而非单次操作的时间。缓存作为CPU和主存之间的高速缓冲,其速度需要与CPU匹配,容量则直接影响缓存的命中率。

本文档详细阐述了存储器的组织结构、地址线和数据线的计算方法、多芯片存储器的组合、存储器带宽的计算以及不同层次存储器的速度特性,对于理解存储系统有重要的理论和实践价值。

595 浏览量

734 浏览量

630 浏览量

580 浏览量

534 浏览量

714 浏览量

DUTzjh

- 粉丝: 6

- 资源: 39

最新资源

- pev2:Postgres解释可视化工具2

- U26fog

- Flash+C#在线拍照源码_图片动画网站.rar

- kzzeksnd.zip_kzze

- GreedyNN

- 华为软件设计方案模板

- SSE-Github:该存储库包含博客的演示应用程序

- 丛林铁轨

- 高斯白噪声matlab代码-WMC-Project---MATLAB-simulation-of-RSS-based-channel-mode

- Tweed.

- EloFix

- vb屏幕取词 很简单的一个程序

- 百度离线地图实现绘制路径并打点示例

- pgbouncer:PostgreSQL轻量级连接池

- Trajax

- 滴滴快的智能出行平台数据2016年8月-西安-数据集