ADS1212, 1213

9

SBAS064A

THEORY OF OPERATION

The ADS1212 and ADS1213 are precision, high dynamic

range, self-calibrating, 24-bit, delta-sigma A/D converters

capable of achieving very high resolution digital results.

Each contains a programmable gain amplifier (PGA); a

second-order delta-sigma modulator; a programmable digi-

tal filter; a microcontroller including the Instruction, Com-

mand and Calibration registers; a serial interface; a clock

generator circuit; and an internal 2.5V reference. The

ADS1213 includes a 4-channel input multiplexer.

In order to provide low system noise, common-mode rejec-

tion of 100dB and excellent power supply rejection, the

design topology is based on a fully differential switched

capacitor architecture. Turbo Mode, a unique feature of the

ADS1212/13, can be used to boost the sampling rate of the

input capacitor, which is normally 7.8kHz with a 1MHz

clock. By programming the Command Register, the sam-

pling rate can be increased to 15.6kHz, 31.2kHz, 62.5kHz,

or 125kHz. Each increase in sample rate results in an

increase in performance when maintaining the same output

data rate.

The programmable gain amplifier (PGA) of the ADS1212/

13 can be set to a gain of 1, 2, 4, 8 or 16—substantially

increasing the dynamic range of the converter and simplify-

ing the interface to the more common transducers (see Table

I). This gain is implemented by increasing the number of

samples taken by the input capacitor from 7.8kHz for a gain

of 1 to 125kHz for a gain of 16. Since the Turbo Mode and

PGA functions are both implemented by varying the sam-

pling frequency of the input capacitor, the combination of

PGA gain and Turbo Mode Rate is limited to 16 (see Table

II). For example, when using a Turbo Mode Rate of 8

(62.5kHz at 1MHz), the maximum PGA gain setting is 2.

The output data rate of the ADS1212/13 can be varied from

less than 1Hz to as much as 6.25kHz, trading off lower

resolution results for higher data rates. In addition, the data

rate determines the first null of the digital filter and sets the

–3dB point of the input bandwidth (see the Digital Filter

section). Changing the data rate of the ADS1212/13 does not

result in a change in the sampling rate of the input capacitor.

The data rate effectively sets the number of samples which

are used by the digital filter to obtain each conversion result.

A lower data rate results in higher resolution, lower input

bandwidth, and different notch frequencies than a higher

data rate. It does not result in any change in input impedance

or modulator frequency, or any appreciable change in power

consumption.

The ADS1212/13 also includes complete on-board calibra-

tion that can correct for internal offset and gain errors or

limited external system errors. Internal calibration can be

run when needed, or automatically and continuously in the

background. System calibration can be run as needed and the

appropriate input voltages must be provided to the ADS1212/

13. For this reason, there is no continuous system calibration

mode. The calibration registers are fully readable and writ-

able. This feature allows for switching between various

configurations—different data rates, Turbo Mode Rates, and

gain settings—without re-calibrating.

The various settings, rates, modes, and registers of the

ADS1212/13 are read or written via a synchronous serial

interface. This interface can operate in either a self-clocked

mode (Master Mode) or an externally clocked mode (Slave

Mode). In the Master Mode, the serial clock (SCLK) fre-

quency is one-quarter of the ADS1212/13 X

IN

clock fre-

quency.

The high resolution and flexibility of the ADS1212/13 allow

these converters to fill a wide variety of A/D conversion

tasks. In order to ensure that a particular configuration will

meet the design goals, there are several important items

which must be considered. These include (but are certainly

not limited to) the needed resolution, required linearity,

desired input bandwidth, power consumption goal, and sen-

sor output voltage.

The remainder of this data sheet discusses the operation of

the ADS1212/13 in detail. In order to allow for easier

comparison of different configurations, “effective resolu-

tion” is used as the figure of merit for most tables and

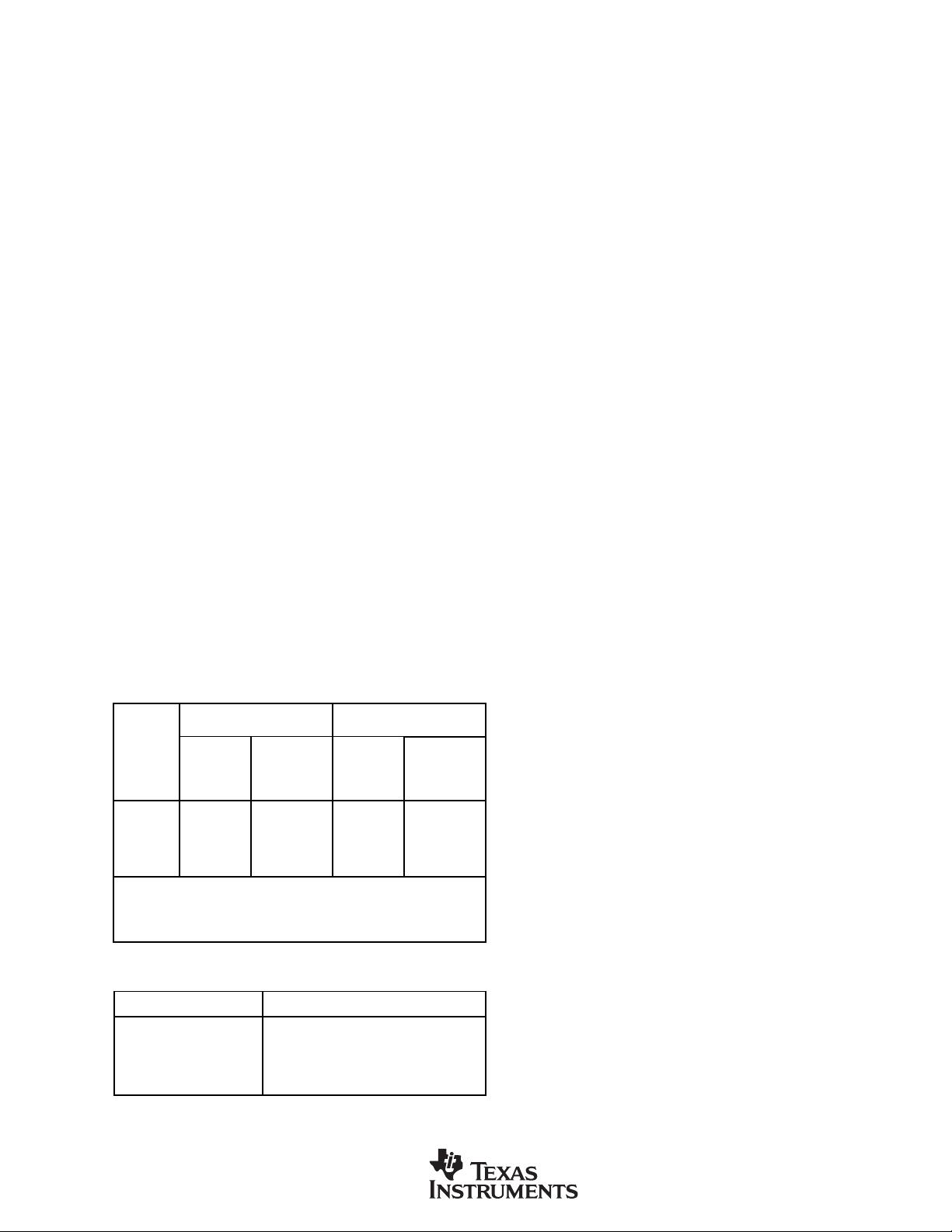

graphs. For example, Table III shows a comparison between

data rate (and –3dB input bandwidth) versus PGA setting at

a Turbo Mode Rate of 1 and a clock rate of 1MHz. See the

Definition of Terms section for a definition of effective

resolution.

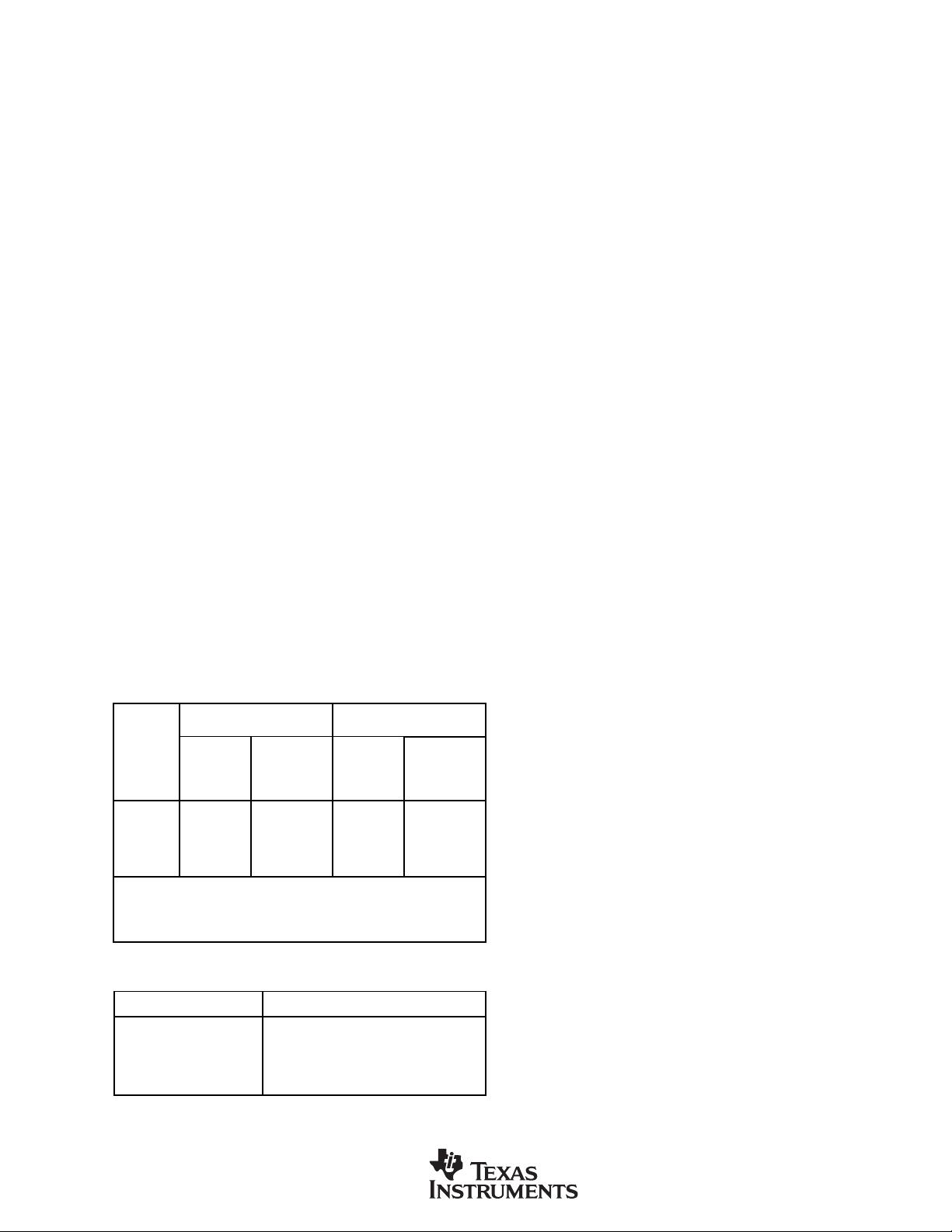

ANALOG ANALOG INPUT

INPUT

(1)

UTILIZING V

BIAS

(1,2)

FULL- EXAMPLE FULL- EXAMPLE

SCALE VOLTAGE SCALE VOLTAGE

GAIN RANGE RANGE

(3)

RANGE RANGE

(3)

SETTING (V) (V) (V) (V)

1 10 0 to 5 40 ±10

2 5 1.25 to 3.75 20 ±5

4 2.5 1.88 to 3.13 10 ±2.5

8 1.25 2.19 to 2.81 5 ±1.25

16 0.625 2.34 to 2.66 2.5 ±0.625

NOTE: (1) With a 2.5V reference, such as the internal reference. (2) This

example utilizes the circuit in Figure 12. Other input ranges are possible. (3)

The ADS1212/13 allows common-mode voltage as long as the absolute

input voltage on A

IN

P or A

IN

N does not go below AGND or above AV

DD

.

TABLE I. Full-Scale Range vs PGA Setting.

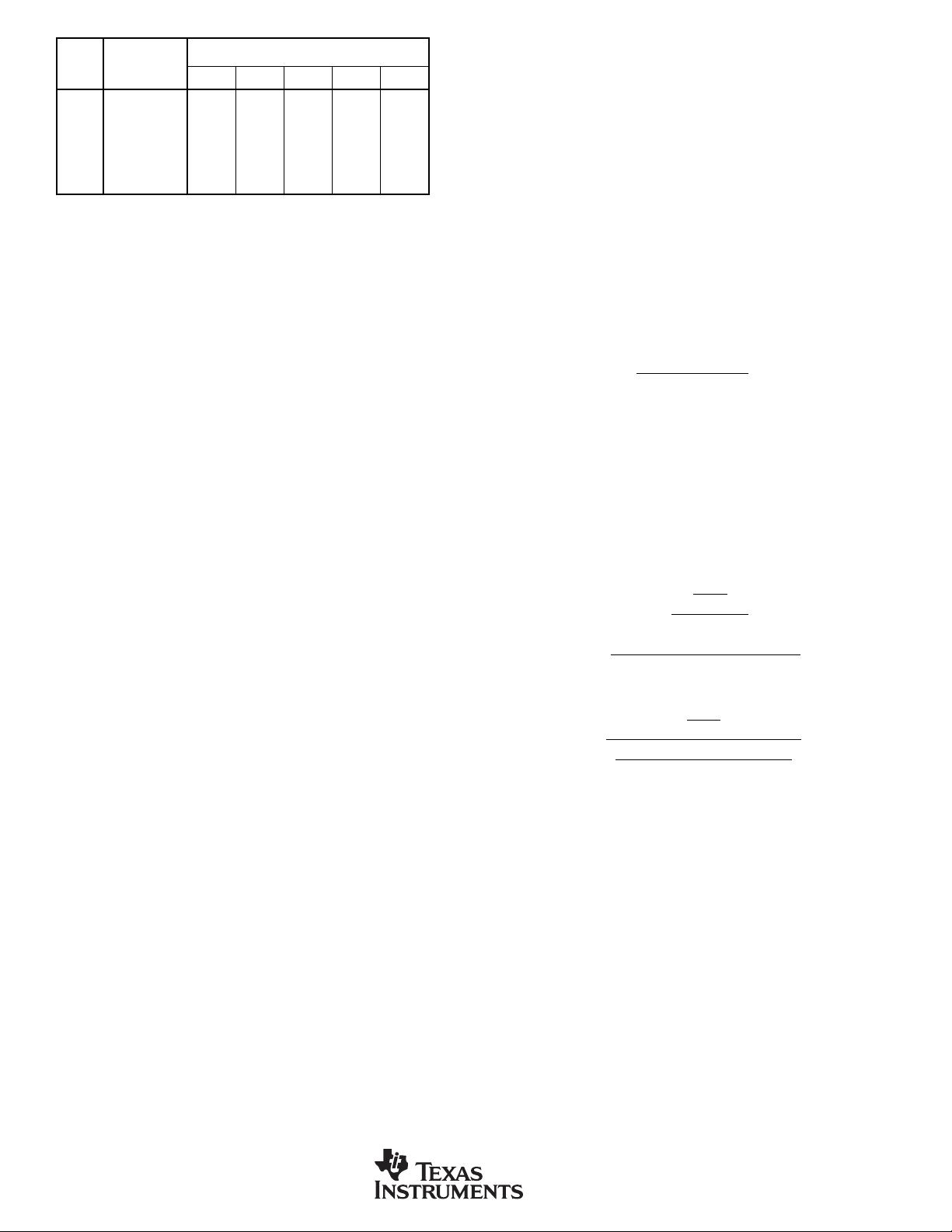

TURBO MODE RATE AVAILABLE PGA SETTINGS

1 1, 2, 4, 8, 16

2 1, 2, 4, 8

4 1, 2, 4

8 1, 2

16 1

TABLE II. Available PGA Settings vs Turbo Mode Rate.