优化ADC信号链:放大器噪声对动态性能的影响及AD8375应用

167 浏览量

更新于2024-09-01

收藏 319KB PDF 举报

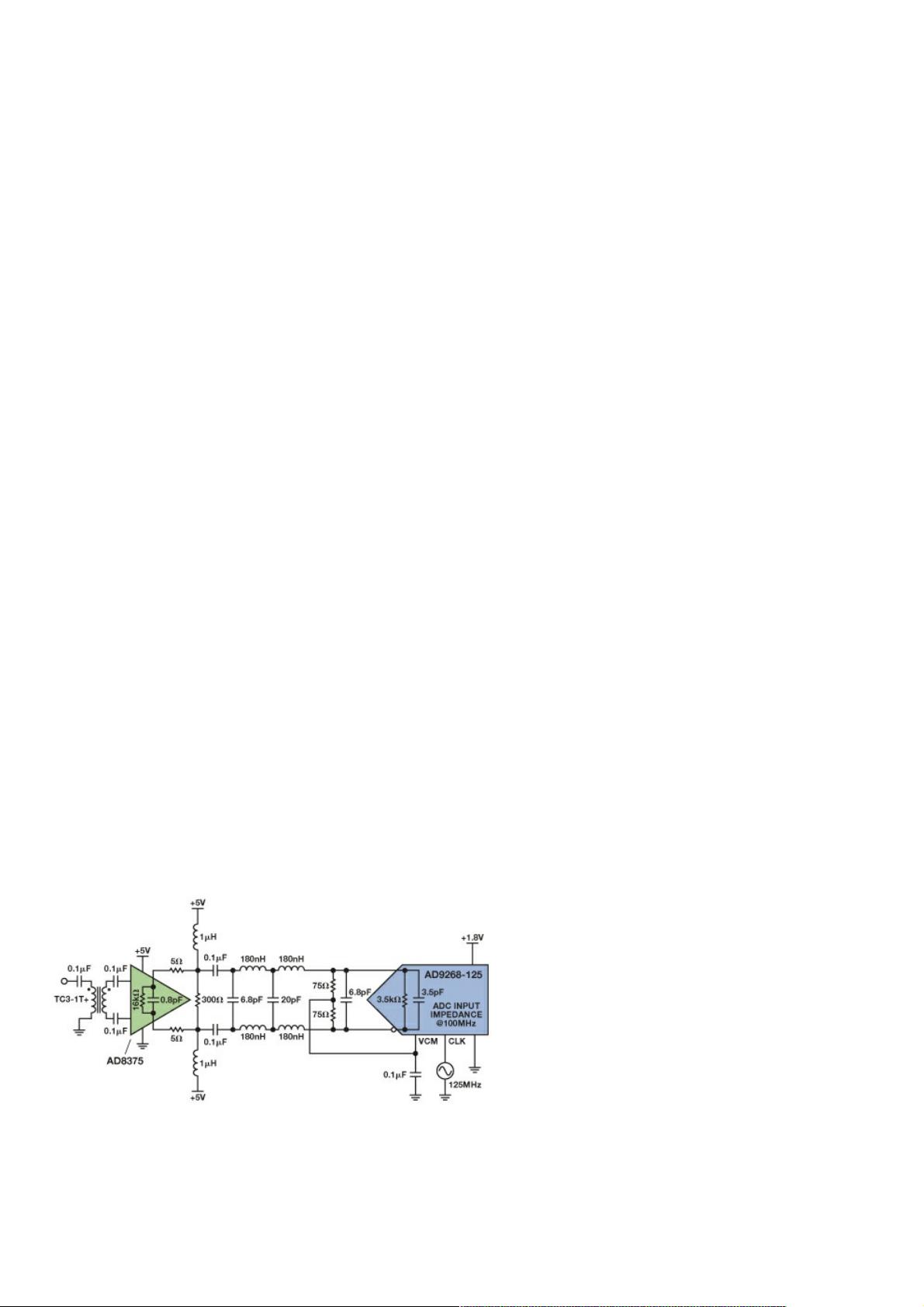

本文深入探讨了在ADC信号链中,放大器噪声对于总噪声的影响及其对系统性能的关键作用。具体分析了一个采用双通道16位、125/105/80 MSPS的流水线ADC AD9268和超低失真中频VGA AD8375的电路。信号链的设计包括VGA(在+6 dB增益设置下运行),配合五阶巴特沃兹低通滤波器(带宽滚降频率为100 MHz),旨在确保在目标频段内获得理想的动态性能。

在实际应用中,如高速ADC系统,信号源的驱动和放大是非常关键的步骤。VGA作为增益可调设备,能够根据需要扩展输入信号,以便使其达到ADC的最大输入范围,从而提高信噪比(SNR)和无杂散动态范围(SFDR)。例如,AD9268 ADC在70 MHz的中频下表现出优异的性能,提供高达78.2 dBFS的SNR和88 dBc的SFDR,特别适合需要高动态范围和高分辨率的应用。

然而,放大器作为有源器件,不可避免地会产生噪声,尤其是在工作带宽内。这些噪声累积会导致转换性能下降。因此,选择合适的放大器时,需要综合考虑模拟输入范围、输入频率/带宽、分辨率需求、以及所需的SFDR等因素。AD8375 VGA不仅具备将单端信号转换为差分信号的能力,还能保持高线性度和一致的噪声特性,是驱动ADC的理想选择,特别是在高频操作中。

文章的重点在于噪声计算,特别是放大器和滤波器的噪声贡献,这对于理解ADC的整体性能至关重要。通过精确评估这些噪声源,工程师能够优化信号链设计,确保在实际应用中达到预期的性能指标,避免由于噪声引入的潜在问题。

本文提供了一套详细的理论与实践相结合的方法,帮助读者理解和处理ADC信号链中放大器噪声对总噪声的影响,从而在设计和优化高性能电子系统时做出明智的决策。

154 浏览量

124 浏览量

124 浏览量

154 浏览量

233 浏览量

168 浏览量

2012-11-26 上传

2023-03-01 上传

168 浏览量

weixin_38660813

- 粉丝: 5

- 资源: 982

最新资源

- 紫黄扁平化工作总结图表大全PPT模板

- stuntz-strategies.github.io:stuntzstrategies.com

- GitRainbow-crx插件

- 煤渣:干净,响应Swift的MkDocs主题

- 基于modbus协议的大屏数据监控,使用modbus slave模拟数据,串口服务器获取温湿度.zip

- office2007驱动AccessDatabaseEngine.zip

- sample-quarkus-speaker:这是一个如何使用JAX-RS RESOURCES,Hibernate Panache以及如何准备在Openshift中使用S2I的项目的示例。

- Free fire generator-crx插件

- farmaciaJS:法玛西亚

- AngularJs-and-grunt-with-java-spring

- 数据结构课后答案

- sqlite-utils:用于操纵SQLite数据库的Python CLI实用程序和库

- SpringBoot-atguigu-resource:Bilibili SpringBoot_2019权威教程CRUD实验静态资源文件

- 蓝色复古花卉文艺范图表下载PPT模板

- duplichecker for chrome-crx插件

- binwalk-master.zip