FPGA实现IIR数字滤波器:比较与设计方法

"FIR数字滤波器设计3 - FPGA实现IIR数字滤波器"

在数字信号处理领域,FIR(Finite Impulse Response,有限冲激响应)和IIR(Infinite Impulse Response,无限冲激响应)数字滤波器是两种常用的滤波技术。本资源主要关注的是在CPLD或FPGA上实现IIR数字滤波器的方法。

IIR滤波器相比FIR滤波器有其独特的优势。首先,IIR滤波器可以通过设置传输函数的极点位置来实现较高的选择性,这通常只需要较低的阶数,减少了所需的存储单元数量,因此在经济性和效率方面更具优势。相比之下,FIR滤波器为了达到同样的设计指标,可能需要更高的阶数,这不仅增加了成本,也导致了更大的信号延迟。

在设计工具方面,IIR滤波器的设计可以直接借鉴模拟滤波器的成果,通常有封闭形式的设计公式,计算工作量相对较小,对计算工具的要求不高。这使得IIR滤波器在实现卷积、相关和自适应滤波等任务时广泛应用。

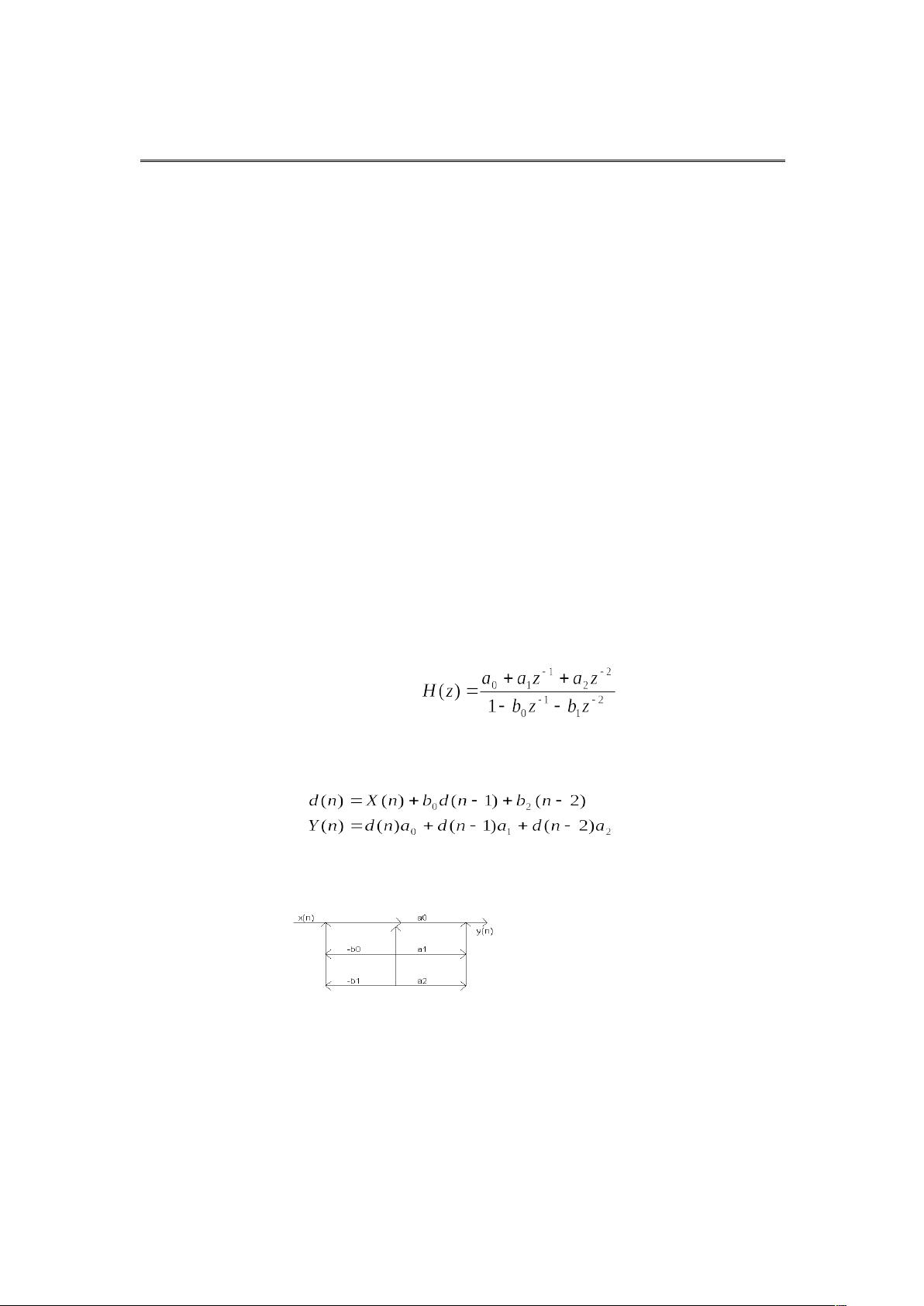

IIR滤波器在FPGA上的实现主要有两种方案:

1. 直接相乘累加式(Direct Form II):这是最直观的实现方式,适用于二阶IIR滤波器。其传递函数可以通过乘法和加法运算来实现,但这种方式需要较多的硬件乘法器和加法器,对FPGA资源消耗较大。例如,一个二阶IIR滤波器需要5个乘法器和6个加法器。

2. 基于ROM查表法的VHDL结构化设计:这种方法旨在避免使用硬件乘法器,通过预计算并存储系数,然后在运行时通过查表来完成滤波运算。对于二阶IIR滤波器,输入序列可以转换成固定点表示,通过ROM查找得到所需的结果。这种方案虽然节省了乘法器资源,但需要较大的ROM存储空间,且设计过程更复杂。

IIR滤波器在FPGA上的实现需要权衡资源利用率和性能需求。直接相乘累加式简单直观,但资源消耗大;而ROM查表法虽然节省资源,但设计和实现过程更为复杂。在实际应用中,设计者需要根据具体需求和FPGA资源限制来选择合适的方法。

phd11

- 粉丝: 0

- 资源: 12