TSC695sparcv7处理器用户手册:航天级CPU解析

"TSC695sparcv7处理器——这是一本关于SPARCV7处理器的手册,专注于航空航天应用,提供了TSC695F型号的详细信息,涵盖了处理器的特性、架构、产品描述和各种内置功能模块。"

在本文档中,SPARCV7处理器被详细介绍,它是32位的太空级处理器,适用于严苛的航天环境。手册分为多个部分,详细阐述了该处理器的关键特性、架构以及产品描述。

**第一部分:特点**

1.1 描述:这部分提供处理器的基本概述,包括其设计目的和应用场景。

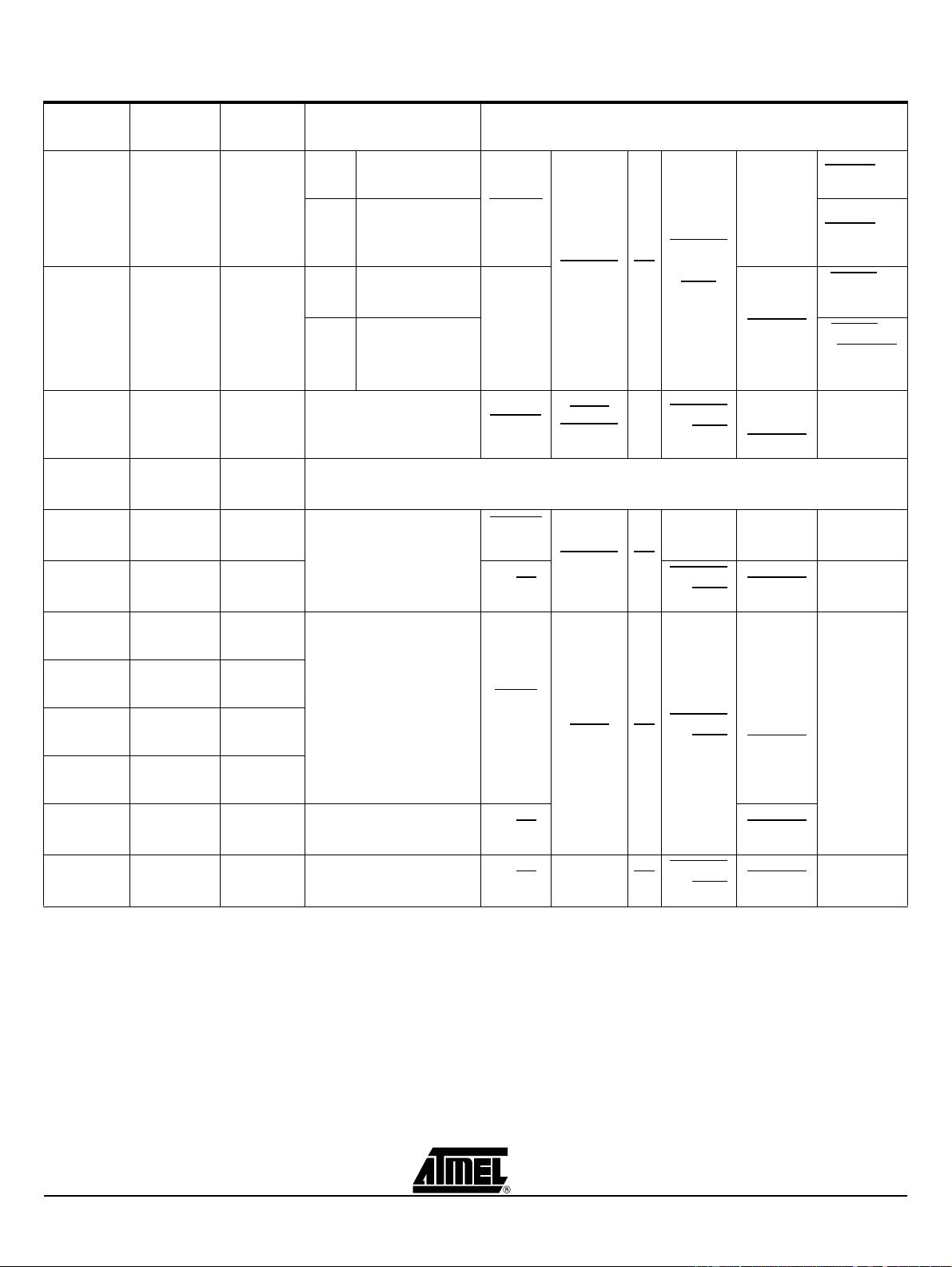

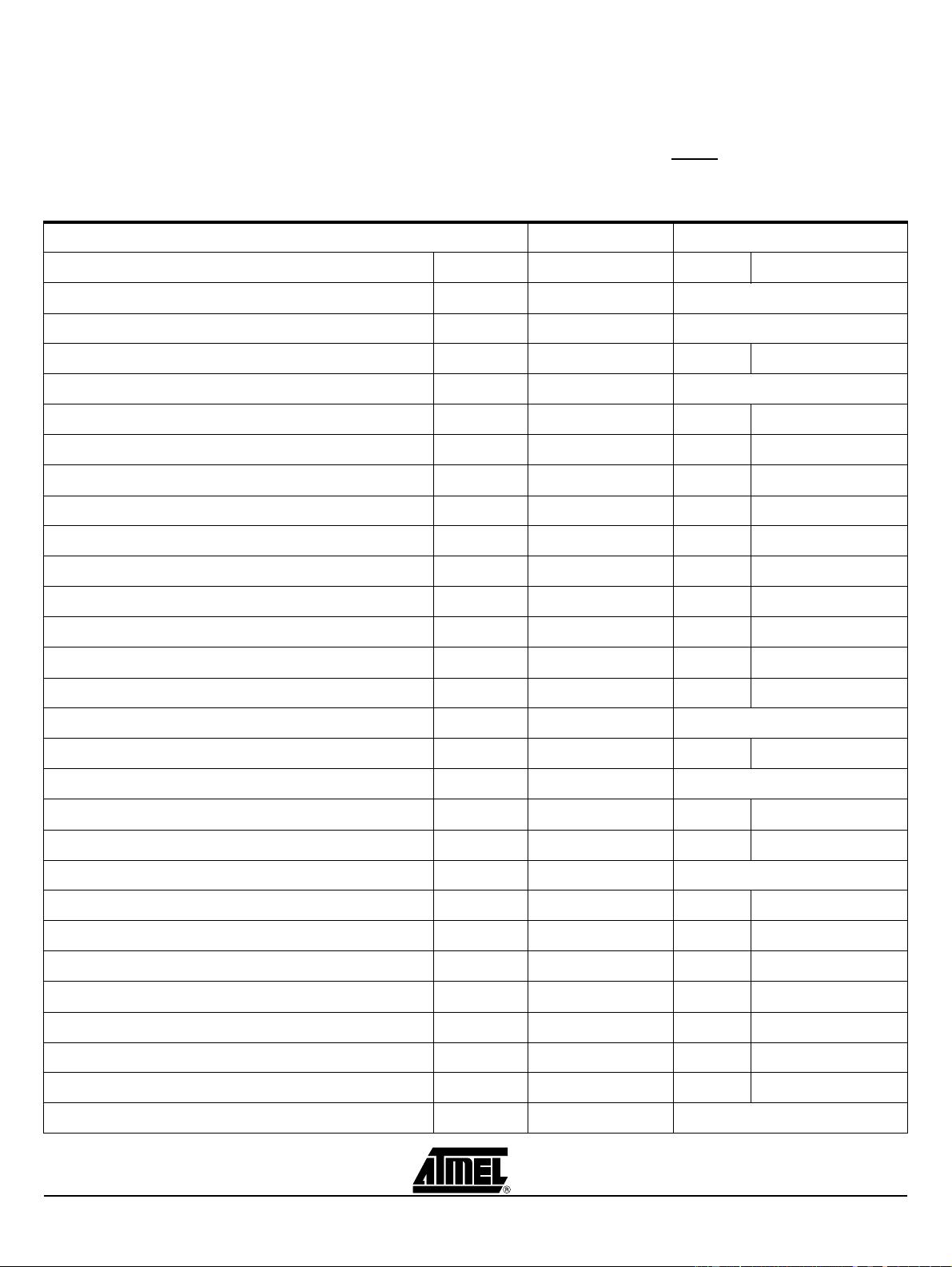

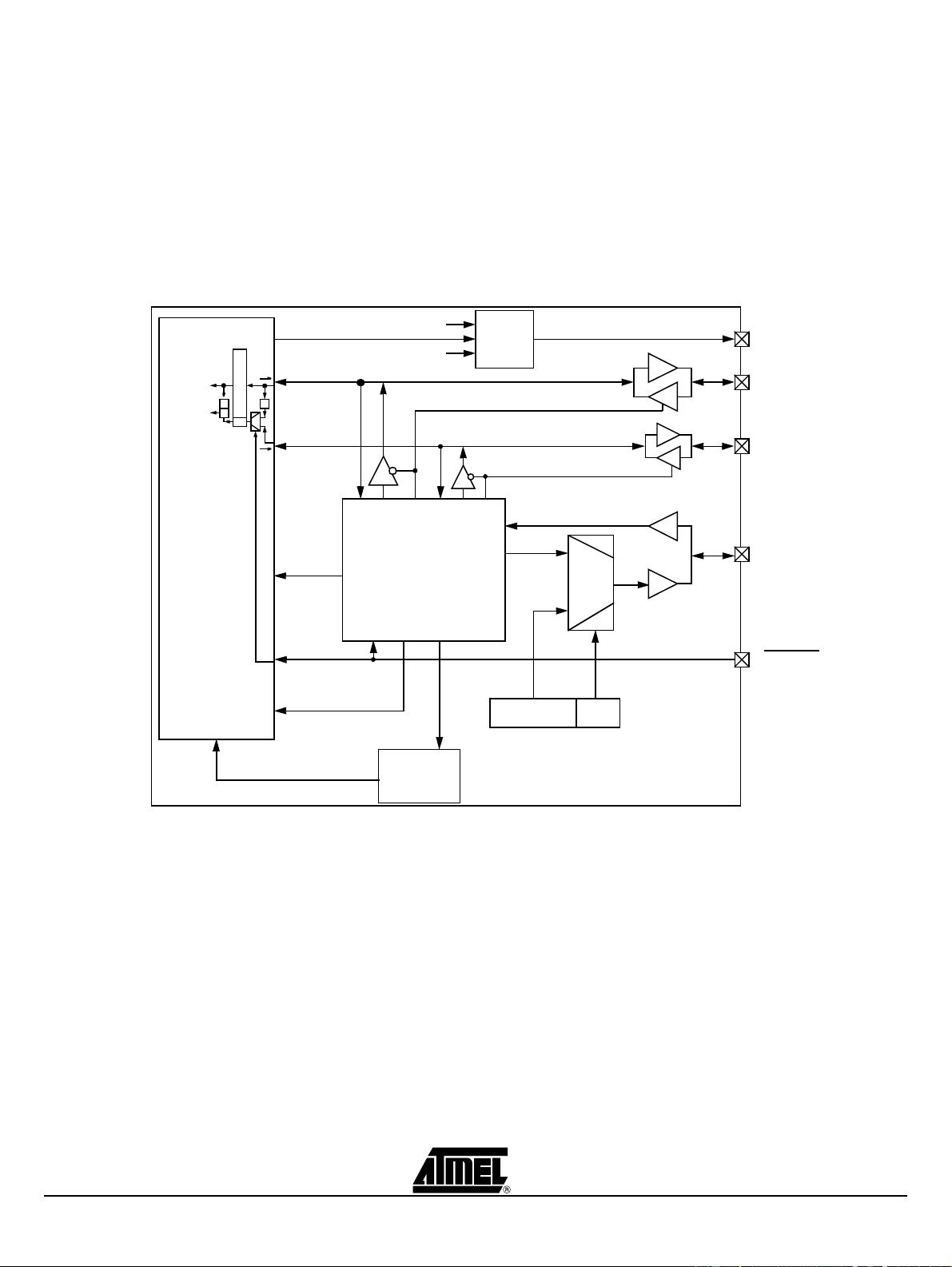

1.2 块图:展示了处理器内部不同组件的连接和工作方式。

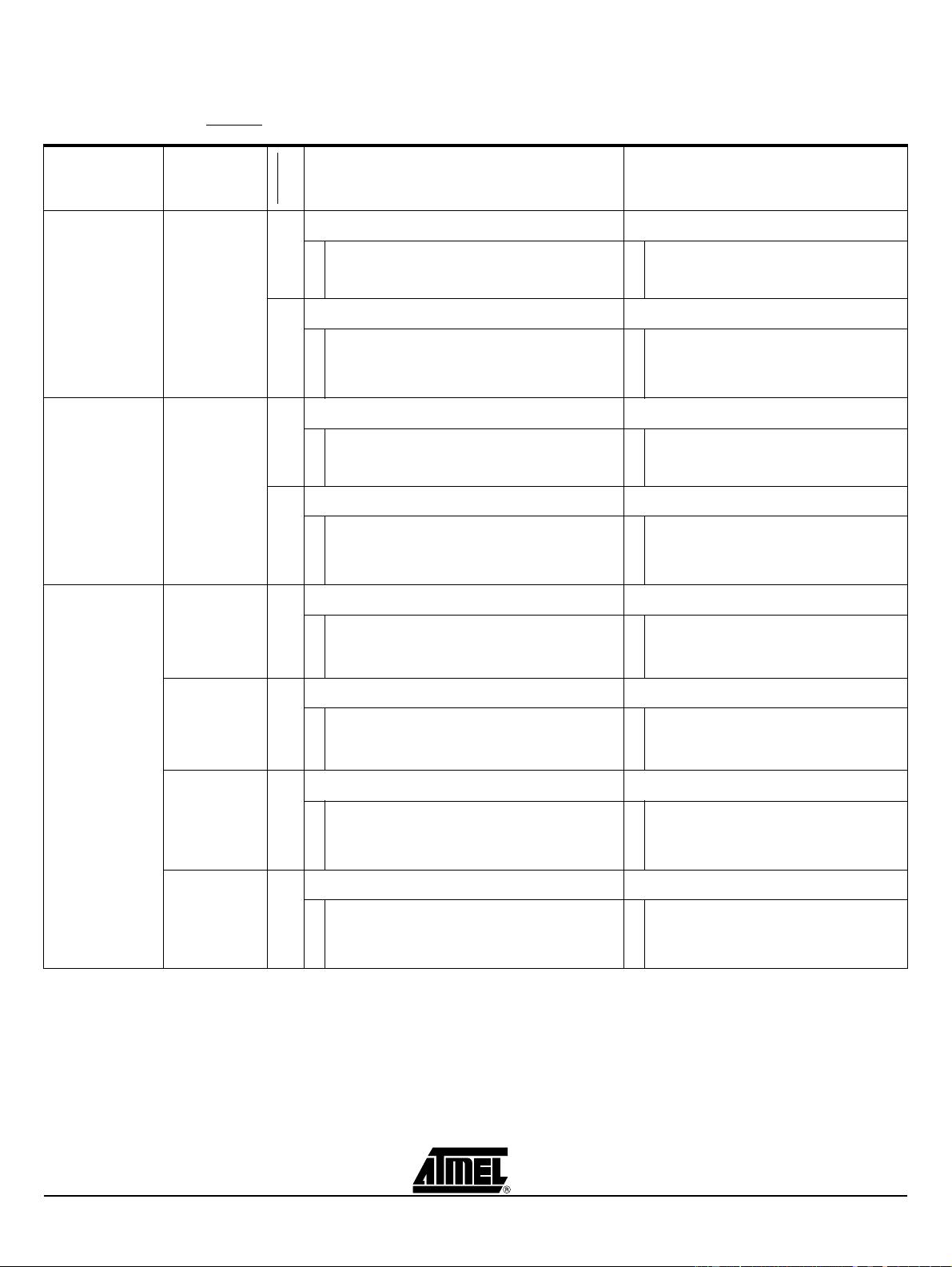

1.3 引脚描述:详细列出了每个引脚的功能,这对于硬件集成至关重要。

1.4 系统架构:探讨了处理器如何与外部系统交互和组织其内部结构。

**第二部分:架构**

2.1 RISC机器:SPARCV7是基于精简指令集计算(RISC)原则的,简化了指令集,提高了执行效率。

2.2 RISC的特点:强调了RISC的优势,如高吞吐量、更少的指令周期和更高效的内存管理。

2.2.1 RISC的优势:详细讨论了RISC架构在性能和能效方面的优点。

2.3 SPARC架构:SPARC是一种广泛使用的架构,具有特定的特性,如:

**第三部分:产品描述**

3.1 概念:概述了TSC695F处理器的设计理念和目标。

3.2 整数单元:处理整数运算的核心部分。

3.3 浮点单元:专为浮点运算优化,支持科学计算和图形处理。

3.4协处理器单元:扩展了处理器的功能,可以处理特定任务,如浮点运算或专门的数学运算。

3.5 指令集:描述了处理器支持的指令集合,包括数据处理、分支、内存访问等。

3.6 内置外围设备:

- 内存映射:定义了内存区域和外设地址空间的关系。

- 系统寄存器:控制处理器状态和行为的关键元素。

- 等待状态和超时生成器:用于优化内存访问速度。

- EDAC(错误检测和校正):增强了数据的可靠性。

- 内存和I/O奇偶校验:用于检测和预防数据错误。

- DMA(直接存储器访问):允许高效的数据传输。

- 中断和陷阱:处理异常和系统调用。

- 定时器:用于计时和事件调度。

- UARTs(通用异步收发传输器):实现串行通信。

- 通用接口:提供灵活的外设连接选项。

- 执行模式:处理器的不同操作状态,如用户模式、内核模式等。

- 错误处理程序:处理硬件和软件错误。

- 奇偶校验检查:增强数据完整性。

- 系统时钟:管理处理器和其他组件的工作节奏。

- 系统可用性:讨论了处理器的可靠性和耐久性。

- 测试模式:用于诊断和测试目的。

**总结**

TSC695F SPARCV7处理器是一个专门为航空航天应用设计的高性能处理器,其RISC架构和丰富的内置功能使其在复杂环境中表现出色。手册通过详细的技术规格和功能描述,为设计者和工程师提供了全面的参考资料,以确保在系统集成和维护过程中能够充分利用该处理器的能力。

431 浏览量

113 浏览量

236 浏览量

127 浏览量

125 浏览量

2021-09-25 上传

2021-09-24 上传

115 浏览量

2024-11-04 上传

lanxiao029

- 粉丝: 0

- 资源: 1

最新资源

- chat-app-master

- MAST-MOBILE:MAST Android应用程序源代码-Android application source code

- nanodegree-p3-classic-arcade-game:nanodegree-p3-classic-arcade-game

- Just_Java-app:这是我的第一拳Android项目,通过该项目,我通过Just Java应用程序了解了android的各种基础知识

- SIXSIGMA六标准差——教练级黑带师、黑带、绿带培训方案

- 数据营项目

- tool-conventions:支持使用WebAssembly的工具之间的互操作性的约定

- learn-bootstrap:这个 repo 是为我创建的,用于通过 tutorialls 学习引导程序

- FitJournal:Fit Journal应用程序的源代码-Android application source code

- 计时器

- 金融筹资管理

- thunderboard-android:这是Android的Thunderboard应用程序的源代码-Android application source code

- 网址缩短API登陆页面

- silverstripe-email_reminder:Silverstripe CMS的模块。 在用户的成员资格(或类似权限)即将到期时向用户发送提醒

- nodeschool.io:我对 NodeSchool.io 练习的解决方案

- ASCII-ART:产生与图像相对应的ASCII符号