340 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 42, NO. 2, FEBRUARY 2007

An Agile VCO Frequency Calibration Technique

for a 10-GHz CMOS PLL

Tsung-Hsien Lin, Member, IEEE, and Yu-Jen Lai

Abstract—This paper reports an agile VCO frequency calibra-

tion technique and its application on a 10-GHz CMOS integer-N

phase-locked loop. The proposed calibration method accomplishes

efficient search for an optimum VCO discrete tuning curve among

a group of frequency sub-bands. The agility is attributed to a pro-

posed frequency comparison technique which is based on mea-

suring the period difference between two signals. Other mixed-

signal circuits are also developed to facilitate this approach. The

PLL incorporating the proposed calibration technique is imple-

mented in a 0.18-

m CMOS process. The measured PLL phase

noise at 10 GHz is

102 dBc/Hz at 1-MHz offset frequency and

the reference spurs are lower than

48 dBc. The PLL consumes

44 mW in the low-current mode. The calibration time is less than

4

s.

Index Terms—Calibration, CMOS integrated circuits, frequency

synthesizer, period-based frequency comparison, phase detector,

phase-locked loop (PLL), voltage-controlled oscillator (VCO).

I. INTRODUCTION

P

HASE-LOCKED loops (PLLs) are important building

blocks for communication systems. In many applications,

they are implemented with wide tuning ranges in order to

cover desired operating frequency bands and to accommodate

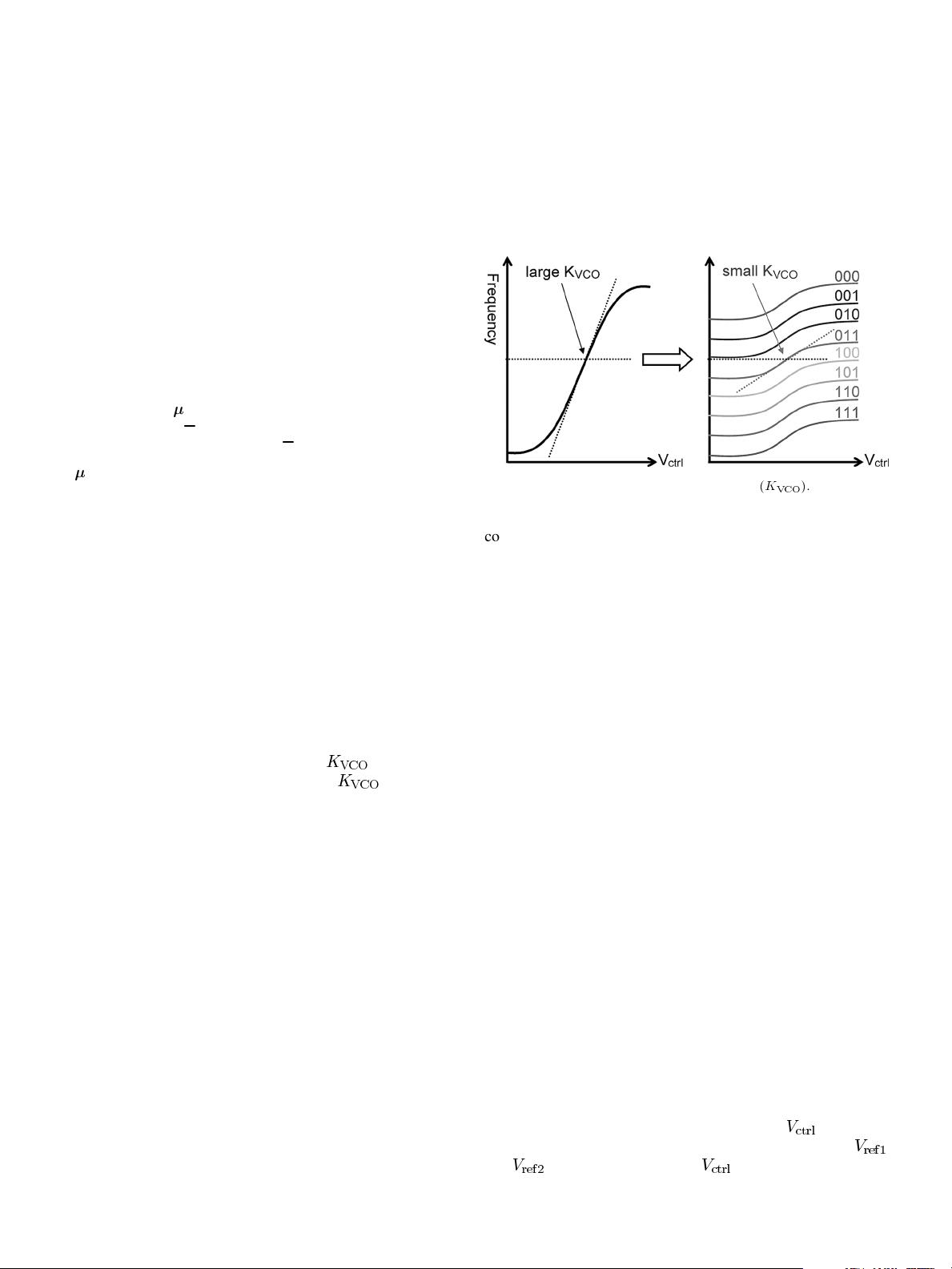

process, voltage, and temperature (PVT) variations. As the PLL

operating frequencies increase while the supply voltages scale

down with advanced CMOS technologies, the voltage-con-

trolled oscillator (VCO) tuning gain (

, expressed in

MHz/V) increases considerably. A large

can degrade

the PLL phase noise and spur performance severely. This issue

can be addressed by employing both discrete and continuous

tuning mechanisms in the VCO design. The implementation is

conceptually illustrated in Fig. 1 [1]–[3]. It employs multiple

overlapped tuning sub-bands to cover the desired frequency

range, instead of using just a single tuning curve. Such topology

achieves low VCO gain while still covering a wide frequency

tuning range. However, this method requires a VCO calibra-

tion (also called coarse tuning) circuit to select the optimum

frequency sub-band that covers the desired frequency. The

time spent on the calibration is in addition to the intrinsic

PLL settling or locking time, and presents an overhead to a

Manuscript received January 11, 2006; revised August 23, 2006. This work

was supported in part by the National Science Council, Taiwan, R.O.C. under

contract number NSC93-2215-E-002-031.

T.-H. Lin is with Graduate Institute of Electronics Engineering and Depart-

ment of Electrical Engineering, National Taiwan University, Taipei 106, Taiwan,

R.O.C. (e-mail: thlin@cc.ee.ntu.edu.tw).

Y.-J. Lai is with the Taiwan Semiconductor Manufacturing Company,

Hsinchu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/JSSC.2006.889360

Fig. 1. Technique for reducing the VCO tuning gain

(

K

)

.

communication system. This may result in a reduced data

throughput. For many communication applications, especially

for frequency hopping systems, such overhead must be kept to

a minimum. To address this issue, an agile VCO calibration

(coarse tuning) method is proposed in the paper.

This paper is organized as follows. In Section II, the existing

VCO calibration techniques are briefly reviewed. The concept

of the time-domain calibration method and the proposed ap-

proaches are detailed in Section III. The circuit implementa-

tion of the 10-GHz integer-

N PLL is described in Section IV,

and the chip results are presented in Section V. Section VI dis-

cusses the advantages of the proposed technique and compares

with other conventional methods. Finally, a conclusion is given

in Section VII.

II. VCO C

ALIBRATION TECHNIQUES

The purpose of performing VCO calibration is to determine

an optimum VCO sub-band under which the PLL can acquire

locking to a reference signal properly. During calibration, com-

parison between the VCO (or its derivative signal) frequency

and the reference frequency is involved. The process of fre-

quency comparison can be carried out when the PLL loop is

either closed or opened. Therefore, the VCO calibration tech-

niques can be categorized into two types according to the PLL

status during calibration.

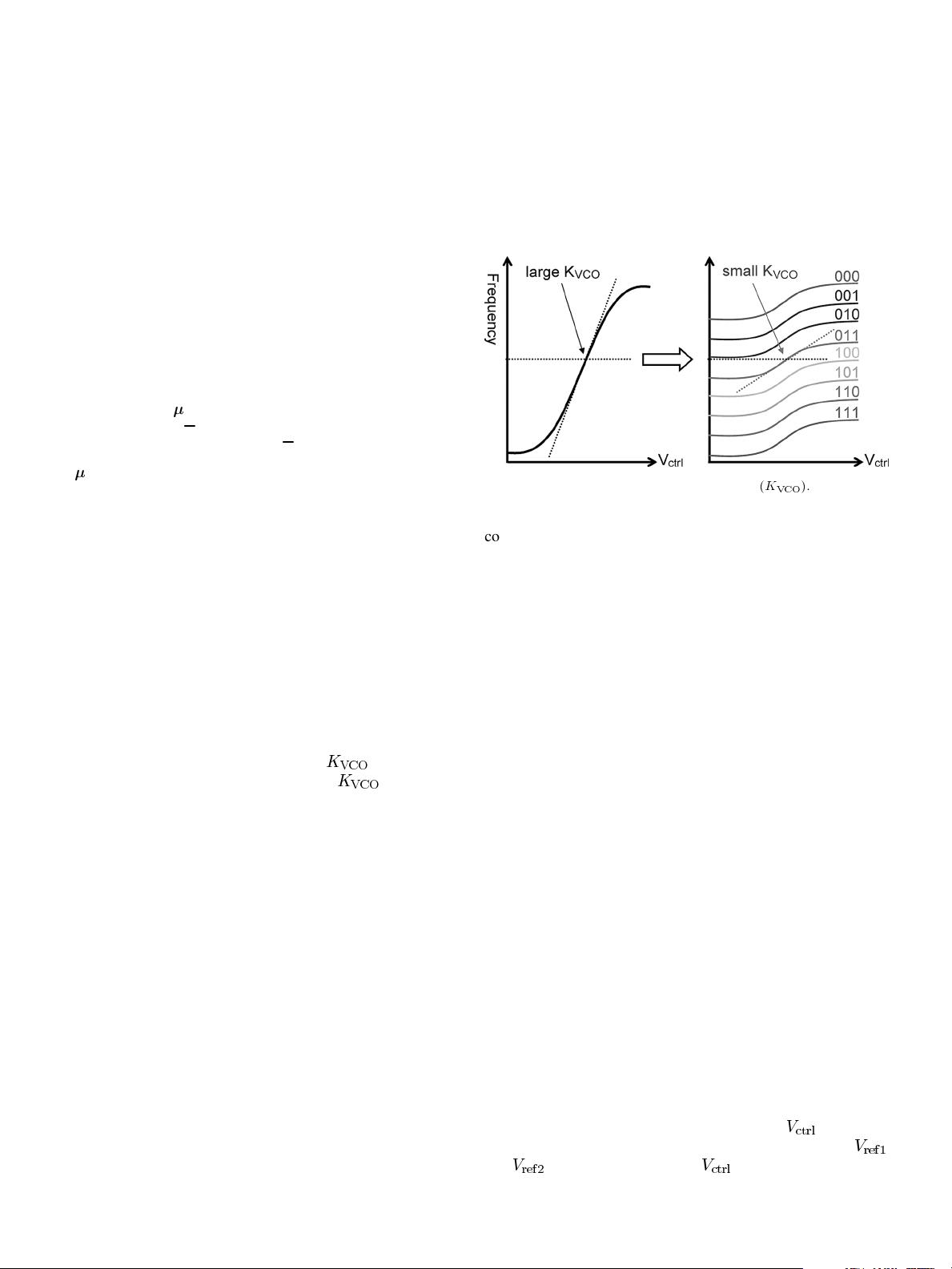

A. Closed-Loop VCO Calibration Technique

The closed-loop VCO calibration approach is depicted in

Fig. 2(a), where the PLL remains closed during calibration [1],

[2]. For a VCO embedded in a PLL, the loop works to lock

the VCO to a desired frequency under a given VCO frequency

sub-band setting. When the loop settles, the

voltage is

compared against a predefined voltage range (between

and ). If the settled value of falls outside this range,

the PLL is considered unable to lock the VCO properly. This

0018-9200/$25.00 © 2007 IEEE