Avalon总线驱动的FPGA TFT LCD控制器设计与实现

需积分: 9 57 浏览量

更新于2024-09-12

收藏 258KB DOC 举报

"该文介绍了基于FPGA的TFT LCD控制器设计,利用Avalon总线连接Altera的SOPC系统,与Nios II处理器和SDRAM控制器协同工作,实现640*480分辨率,16bit色深的图像显示。设计包括了系统工作原理和LCD控制器的工作原理,特别强调了总线冲突的解决策略以及如何优化带宽占用。"

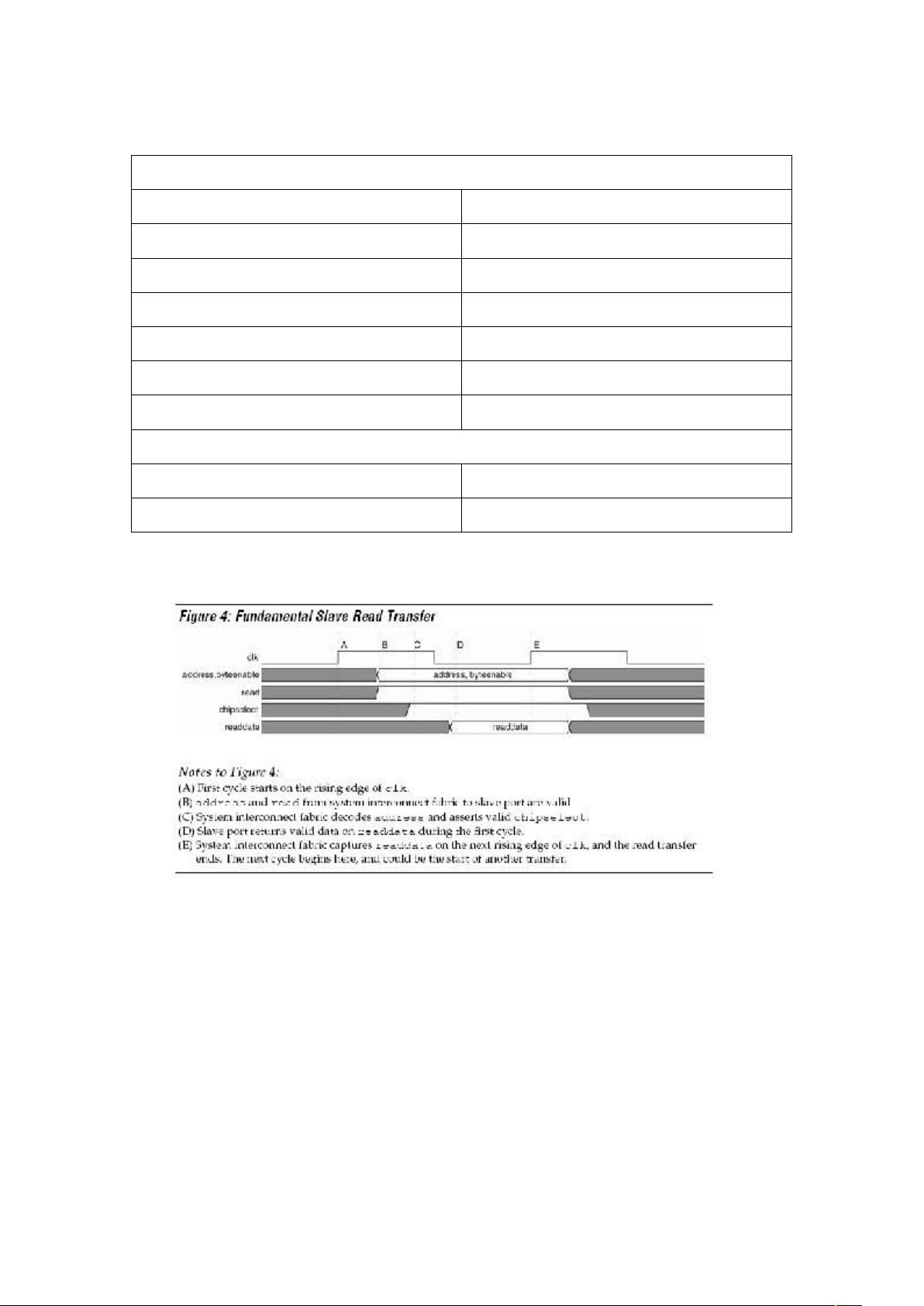

本文主要探讨了一个基于FPGA的TFT LCD控制器设计,该设计采用了Altera的System-On-a-Programmable-Chip (SOPC)解决方案,并利用Avalon总线作为通信接口。Avalon总线是一种简洁的总线架构,使得Nios II软核处理器能够与各种外设,包括SDRAM控制器和LCD控制器,进行高效的数据交换。

设计的目标是创建一个能显示640像素宽乘以480像素高,颜色深度为16位(RGB565格式)的LCD控制器,这适合于TFT液晶显示屏的输出标准。在系统工作原理中,Nios II处理器在SDRAM中分配帧缓冲区,无论是单缓冲还是双缓冲,然后将图像数据写入缓冲区,通过Avalon总线将首地址传递给LCD控制器。控制器随后自动读取这些数据并按TFT格式输出。

在系统中,由于Avalon总线连接多个模块,可能出现总线冲突。为了解决这个问题,Avalon总线内置了仲裁器,可以根据各模块的权重分配总线使用权。关键在于,SDRAM控制器的带宽管理,特别是当处理高分辨率的LCD显示和其他任务时。为缓解带宽压力,文中建议使用专用的SDRAM作为帧缓冲区,从而降低对系统总线带宽的需求。

LCD控制器自身由多个部分构成,包括Avalon总线接口、寄存器组、控制模块、DMA(Direct Memory Access)、FIFO(First-In-First-Out)缓冲区以及时序生成模块。寄存器组允许Nios II处理器通过Avalon总线读写控制参数,以配置和控制LCD控制器的工作状态。

这个设计展示了如何利用FPGA技术构建高效的TFT LCD控制器,通过合理的系统架构和总线管理策略,实现了高分辨率图像的流畅显示,同时也考虑到了系统资源的优化使用。

点击了解资源详情

2022-09-22 上传

2020-10-18 上传

104 浏览量

2020-12-05 上传

2021-07-13 上传

senco_zheng

- 粉丝: 0

最新资源

- Oracle数据库深度探索:体系结构与编程艺术

- 日语计算机词汇解析

- 理解JavaScript基础与HTML DOM操作

- 英语六级翻译核心词组与句子

- UNICODE:统一字符编码的全球解决方案

- 正则表达式详解:匹配与操作

- Together初学者指南:从零创建项目

- 《330 Java Tips》:汇集众多编程智慧

- 2005年中国系统分析员年第1期:软件开发模型比较与项目管理探讨

- 2008年4月四级计算机考试试卷回顾:数据库与SQL Server知识点梳理

- 配置Nokia Kjava开发环境指南

- 软件测试全解析:黑盒、白盒、灰盒及更多

- 基于CTT的通用试题库管理系统开发

- 精通Linux:从新手到高手的进阶教程

- C语言实现队列数据结构与源码详解

- 智能火灾报警系统:无线远程监控技术探索