华为Xilinx HDL代码规范与优化技巧

需积分: 10 37 浏览量

更新于2024-07-25

1

收藏 682KB PDF 举报

本文档主要探讨了华为在Xilinx开发中的代码编写技巧,旨在帮助开发者了解和学习专业级的代码风格,从而提升设计质量和效率。文档涵盖了多个关键主题,包括HDL编码规范、语言子集的选择、设计验证方法以及与合成相关的技术独立性。

在HDL编码风格方面,文档提到了几个核心点:

1. HDLCodingStyle4-1和4-2:这部分可能详细介绍了华为对HDL(硬件描述语言)编码的一般原则和结构,包括代码的可读性、可维护性和可合成性。

2. IEEE1076:这是VHDL的标准,用于模型描述。而IEEE1076(synthesis)部分则可能强调了符合标准的语法以确保代码的工具无关性。

3. Tool & Vendor Specific NPZ(None Portability Zone):建议避免大量使用特定工具的构造,以提高代码的可移植性。

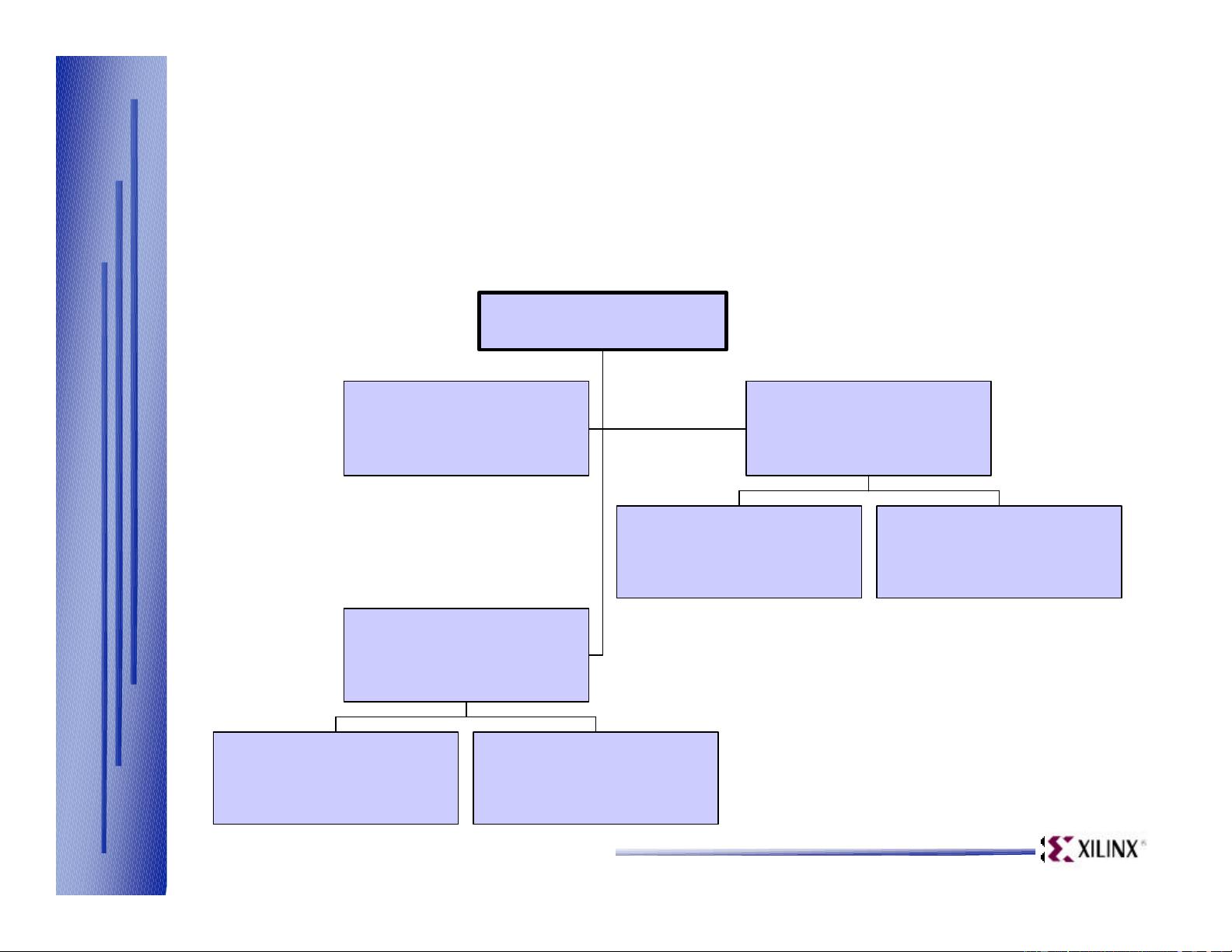

4. HDLCodingStyle4-4:讨论了设计验证的重要性,特别是使用HDL进行设计时,可以进行的行为仿真、门级功能验证和门级时序验证,这些都是基于VHDL模块和测试平台驱动的验证流程。

设计验证是关键的一环,包括:

1. VHDL模块的合成验证,确保设计在逻辑层面上的正确性。

2. Place & Route阶段后的门级功能验证,检查网络列表驱动的功能正确性。

3. Gate-Level Timing验证,通过回注时延信息确保时序满足要求。

4. VITAL (VHDL Initiative Toward ASIC Libraries) 和SDF (Standard Delay Format) 提供了延迟信息的标准化表示,有助于实现更精确的时序分析。

在合成过程中,文档强调了技术独立性和优化:

1. 合成过程分为两步:首先是技术及约束无关的合成,然后是根据具体技术及约束进行的优化。

2. 这种分离确保了设计在不同工艺下的适应性,并允许在满足性能目标的同时保持设计的灵活性。

通过学习这些华为的Xilinx代码技巧,开发者能够更好地理解如何编写高效、高质量的HDL代码,同时掌握设计验证的最佳实践,提升整体设计流程的效率和可靠性。对于希望在华为或其他Xilinx相关项目中工作的工程师来说,这些知识和技巧是至关重要的。

676 浏览量

282 浏览量

135 浏览量

点击了解资源详情

点击了解资源详情

196 浏览量

2009-12-24 上传

点击了解资源详情

点击了解资源详情

芯片验证日记作者

- 粉丝: 8

- 资源: 16

最新资源

- 测试一下

- 倒霉熊图标下载

- SETFSB.zip

- marathon_3:免费的智力马拉松HTML-学院

- BlenderGEResourceKit:Blender游戏引擎的即用型组件集合

- winsdksetup.zip

- Aikatsu LGTM-crx插件

- dsm-htpc-群集

- simple-password-manager:Flutter制作的简单密码管理应用

- 精美蝴蝶图标下载

- 电信设备-带身份核验的物联网移动终端及人证合一核验方法.zip

- 初级java笔试题-cs-study:https://github.com/jwasham/coding-interview-universi

- MinGW压缩包省去繁琐的官网下载

- SYIPAGeneratedScript:make a ipa by script——使用脚本生成ipa包

- VTS Testing Version 2-crx插件

- 帮手