6

线上的。 PD工 USBD12的软连接 (SoftConnet) 技术使得在电路设计中可以省去此电阻,并可以通过软

件设置。

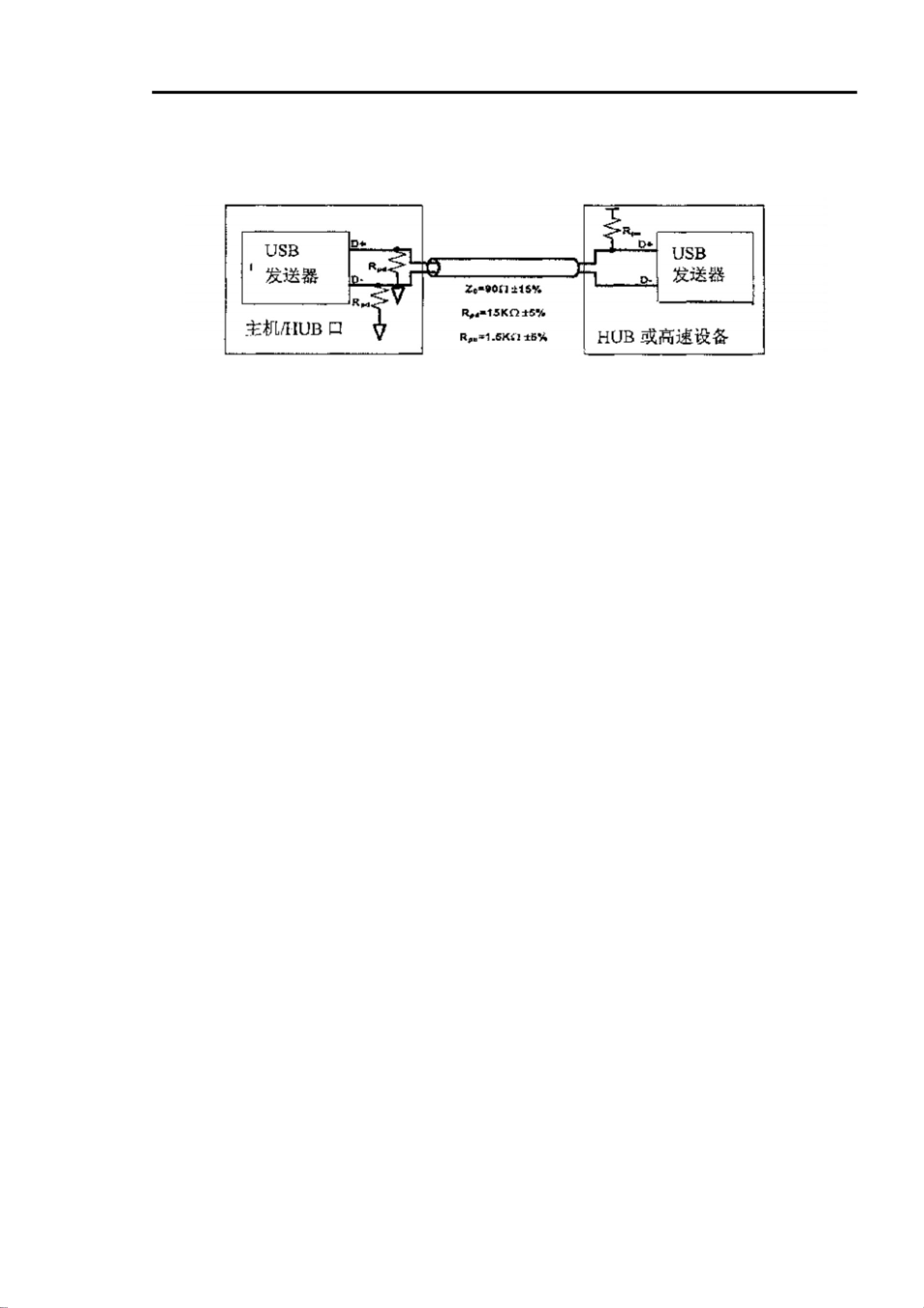

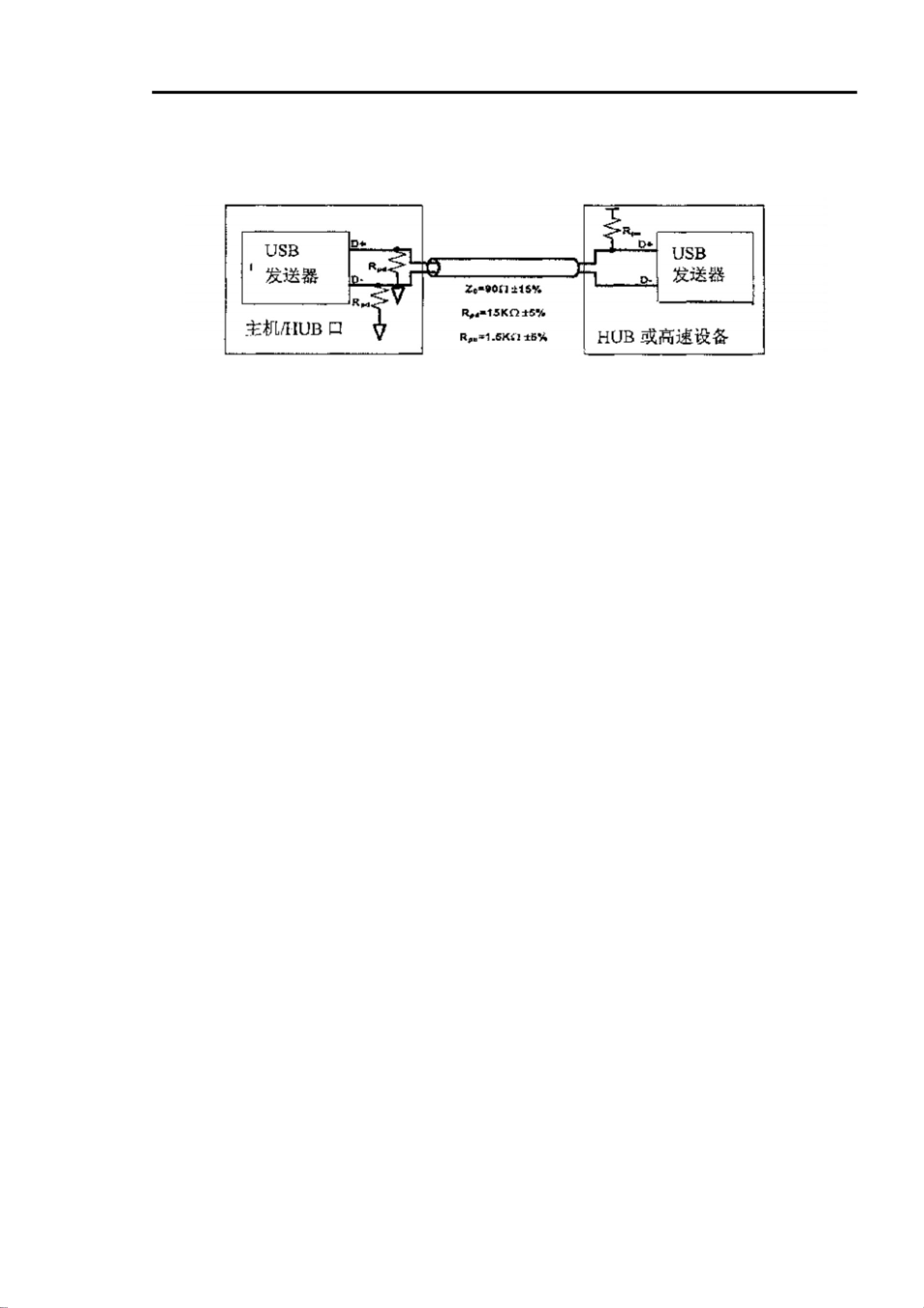

图 2 PDIUSBD12 的原理图

(1) 模拟收发器 : 集成的收发器接口可通过终端电阻直接与 USB电缆相连。

(2) 电压调整器 : 片内集成了一个 3. 3V 的调整器用于模拟收发器的供电,该电压还作为输出连

接到外部上拉电阻。可选择 D12提供的带有上拉电阻的软件连接技术。

(3) 倍频电路 (PLL) 片内集成了 6M到 48M时钟乘法 PLL,就可使用低成本的 6M晶振。

(4) 位时钟恢复 : 位时钟恢复电路使用 4X 过采样规则, 从进入的 USB数据流中恢复时钟。 它能跟

踪 USB规定范围内的抖动和频漂。

(5) 串行接口引擎 (SIE): 串行接口引擎实现了全部的 USB协议层,完全由硬件实现而不需要固件

的参与。该模块的功能包括同步模式的识别、并行 / 串行转换、位填充 / 解除填充、 CRC 校验 / 产生、

PID 校验 / 产生、地址识别和握手评估等。

(6)存储器管理单元 (ME) 和集成 RAM: 在进行数据传输并与微处理器的并口相连时, MMU 和集

成 RAM 作为 USB 间传输的缓冲区,允许 MCU 以它自己速率对 USB 信息包读写。

PDIUSBD12 内部结构框图如图 3 所示 :

(1)模拟收发器 (ANALOG TX/RX ): 集成的收发器直接通过终端电阻与 USB 电缆接口。

( 2)电压调整器 :片上集成的 1 个 3.3V 电压调整器为模拟收发器供电,也提供连接到外部 1.5k Q

上拉电阻的输出电压。 PDIUSBDI2 提供集成 1.5k 0 上拉电阻的 SoftConnect 技术。

( 3)PLL( 锁相环 ):片上集成 I 个 6^-48MHz 的倍频 PLL,允许使用 6MHz 的晶振, EMI 也由于使

用低频晶振而减小。 PLL 的工作不需要外部器件。

( 4)位时钟恢复 :位时钟恢复电路用 4 倍过采样原理,从输入的 USB 数据流中恢复时钟,能跟踪

USB 规范中指出的信号抖动和频率漂移。

( 5)串行接口引擎 (S I E): PHILIPS 的 SIE 完全实现 USB 协议层。考虑到速度,它是全硬件的,

不需要固件 (微程序 )介入。这个模块的功能包括 :同步模式识别、并 /串转换、位填充 /不填充、 CRC