VHDL中的FSM状态机优化与优势

需积分: 13 172 浏览量

更新于2024-08-02

收藏 306KB PDF 举报

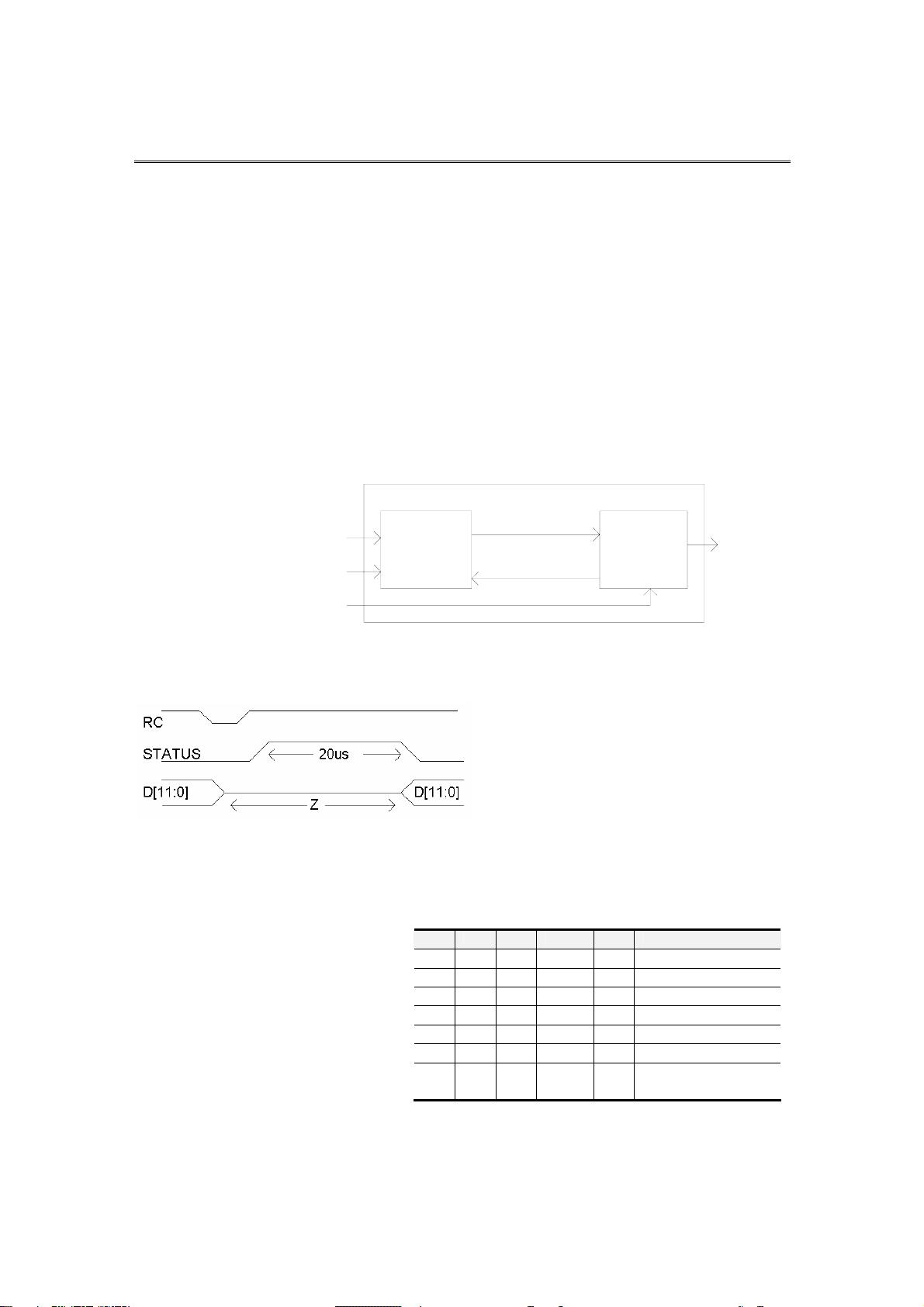

在VHDL编程中,有限状态机(FSM)是一种常用的逻辑设计方法,特别是在需要高效、清晰和易于维护的系统中。FSM的Verilog实现是本章节的核心内容。VHDL中的FSM因其结构简单、设计固定,特别适合利用符号化枚举类型定义状态,使得综合器能够充分利用其优化功能。这些特性使得状态机在性能优化、同步时序逻辑模块构建以及对抗竞争冒险方面表现出色。

首先,状态机作为同步时序逻辑模块,能够有效避免大规模电路设计中的复杂同步问题,通过综合器针对状态机的特殊优化,进一步提升系统的效率。其次,VHDL允许在一个设计实体中嵌套多个状态机,甚至可以支持多个并行运行的状态机,这种并行处理能力使其功能类似高性能微处理器,具有快速运算和控制的优势。一个状态机的执行速度远超单线程CPU,因为它可以在一个时钟周期内完成多项并行操作,降低了程序执行的层级和指令数量。

在可靠性方面,由于状态机的结构和工作方式,相比于依赖于软件指令的CPU,它更易于实现错误检测和恢复机制,从而提供更好的容错能力。例如,状态机可以通过状态转移条件精确控制流程,减少了指令出错导致的连锁反应。此外,状态机的故障隔离和冗余设计也使得系统在遇到个别部件故障时仍能保持稳定运行。

VHDL中的FSM实现是一种强大的工具,它不仅简化了设计过程,提高了系统性能,还提升了系统的可靠性和稳定性。对于初学者来说,由于其清晰的结构和易于理解和调试的特性,使得学习和使用FSM成为一种有效的电路设计策略。因此,掌握FSM在Verilog中的实现,无论是对于开发硬件还是理解高级微处理器工作原理,都是非常有价值的技能。

2012-05-09 上传

2020-04-30 上传

2012-03-02 上传

2022-09-14 上传

2008-04-01 上传

2014-09-09 上传

2022-09-24 上传

edan_yhl

- 粉丝: 0

- 资源: 4

最新资源

- Python库 | rock-0.4.0.tar.gz

- 基于Bootstrap实现的jQuery开关按钮组合源码.zip

- Projects:各种语言的小型项目的集合,目的是增加对几种语言的熟悉程度和流利程度。 我希望使用Java,Go,Python,Objective-C以及Swift来完成此列表

- Scratch少儿编程项目音效音乐素材-【日常生活】音效-扫地.zip

- joseph-circle.zip_数据结构_Visual_C++_

- 【6层】框架办公楼全套设计(含计算书、建筑图,结构图,工程量计算).zip

- 易语言取默认打印机源码-易语言

- comconlabmomoh004_digital_

- 基于HTML5 Canvas超逼真雨滴下落动画特效源码.zip

- R--Programming--Cotton:该存储库包含我在学习语言期间编写的R代码

- 一款漂亮有质感的Layui后台模板SummerAdmin

- luatex-mini:LuaTeX普通TeX的最小包装

- Scratch少儿编程项目音效音乐素材-【声音提示】音效-国风京剧戏鼓版提示音_MP3.zip

- Lib OCX音频处理易语言源码-易语言

- noise_音频信号数据_

- pandas-challenge