"高效并行Turbo码译码器结构设计与FPGA实现"

版权申诉

13 浏览量

更新于2024-03-09

1

收藏 572KB DOCX 举报

本文介绍了一种合并状态度量计算的高效并行Turbo码译码器结构设计及FPGA实现。在无线通信系统中,信道编码技术对于纠正信息传输过程中出现的错误至关重要。Turbo码作为一种先进的迭代信道编码,其译码性能接近香农极限,因此被广泛应用于各个领域,特别是工业物联网中。然而,由于能量受限、译码算法迭代的依赖性和吞吐量的提高成为瓶颈,并且工业物联网中Turbo码译码器的资源占用也是待解决的问题。因此,本文的重点是设计一种降低硬件资源占用并且解决迭代译码算法实现高吞吐量的Turbo码译码器结构。

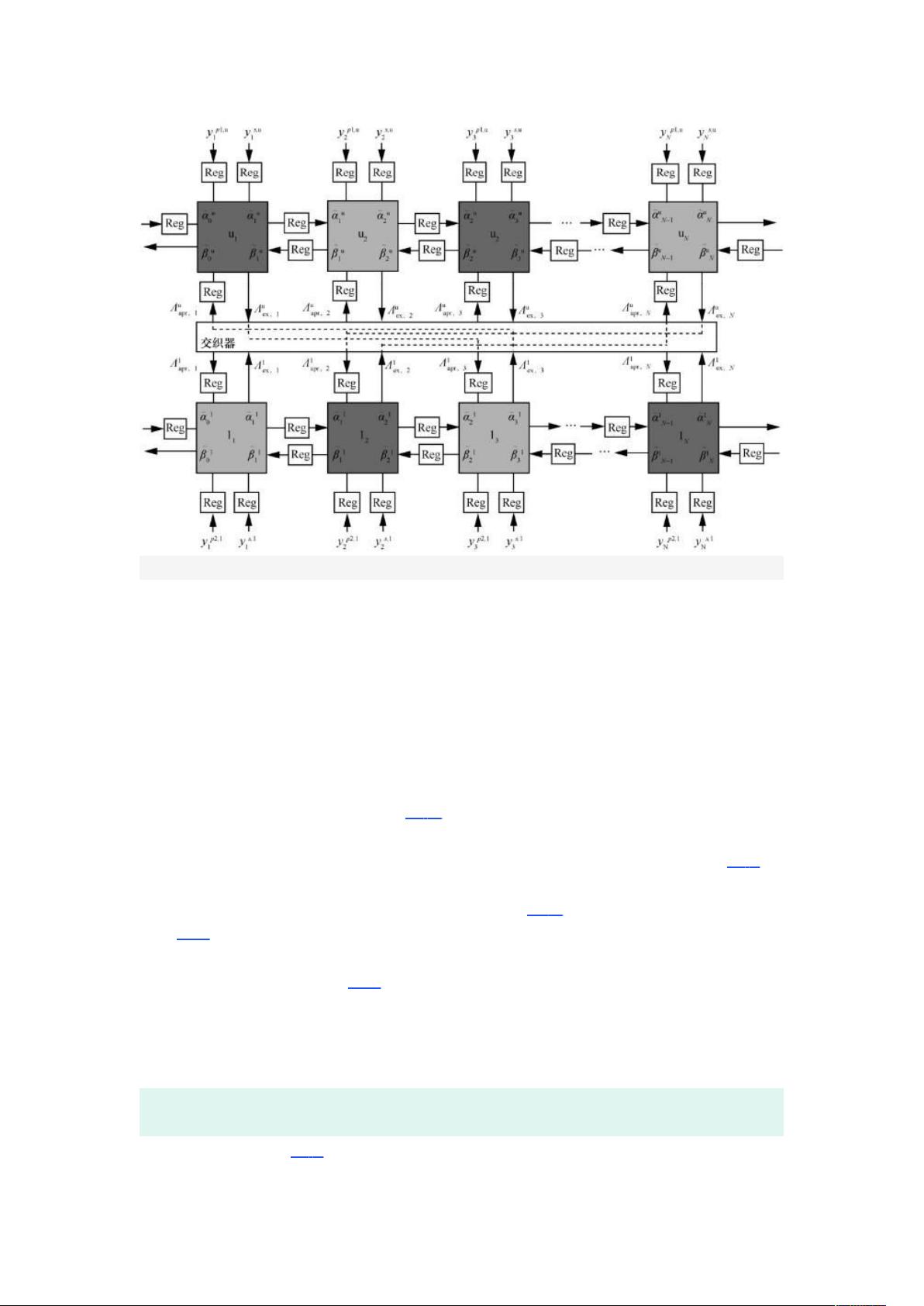

在Turbo码译码器设计的研究中,译码一般采用最大后验概率(MAP)算法,通过交换软信息并且迭代译码的方式获得较好的误码率性能。然而,受限于Turbo码的迭代译码算法MAP算法的复杂性,对数域最大后验概率(Log-MAP)算法成为主要的实现算法。由于Log-MAP算法中对数据的依赖性,因此我们设计了一种合并状态度量计算的高效并行Turbo码译码器结构,以提高译码性能。

在本文中,我们详细介绍了合并状态度量计算的高效并行Turbo码译码器的结构设计及其在FPGA上的实现。首先,我们对Turbo码的原理进行了简要介绍,然后详细描述了Log-MAP算法的原理和实现。接着,我们提出了合并状态度量计算的并行算法,以及相应的硬件结构设计。我们将算法和结构进行了详细的数学推导和分析,证明了其在降低硬件资源占用的同时保持了较高的译码性能。

接下来,我们利用Verilog HDL语言对所提出的Turbo码译码器结构进行了FPGA实现。我们描述了FPGA平台下的系统架构和设计细节,并对其性能进行了实验测试和分析。实验结果表明,所提出的Turbo码译码器结构在FPGA上能够实现高吞吐量和低资源消耗的译码性能,验证了设计的有效性和可行性。

综上所述,本文提出了一种合并状态度量计算的高效并行Turbo码译码器结构设计,并在FPGA平台上进行了实现。该结构在降低硬件资源占用的同时,能够保持较高的译码性能,具有很高的实际应用价值。未来的研究方向可以在进一步优化算法和结构设计的基础上,扩展到其他数字通信系统中的应用。Overall, the key contribution of this work is a novel parallel Turbo code decoder based on a merged state metric calculation. Its efficient design and FPGA implementation demonstrate high decoding performance with reduced hardware resource utilization and potential for practical application. The experimental validation on FPGA platform confirms its effectiveness and feasibility for high-throughput and low-resource consumption in Turbo code decoding, highlighting its potential for practical application in wireless communication systems and industrial IoT. Suggestions for future research include algorithm and design optimization and extension to other digital communication systems.

2011-04-11 上传

2021-07-13 上传

2020-10-15 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

罗伯特之技术屋

- 粉丝: 4502

- 资源: 1万+

最新资源

- Lightweight IDE-开源

- flappy birds,iOS源码.zip

- axure后台管理系统原型rp

- DataStructureAndAlgorithms

- mysql代码-单表查询,多表查询

- ASIO4ALL_2_14_English

- git-app

- exercise-4-teams-room-6:Github Classroom创建的exercise-4-teams-room-6

- bioluigi:基于luigi的生物学分析管道框架

- 机械工程师电子手册.zip

- MobaXterm接管Linux

- react-and-vue

- 网络管理员

- PolaczenieBazaAktualne

- mysql数据库应用.rar

- PyFight:使用pygame的原型格斗游戏