同步/异步计数器设计:J-K触发器实验

需积分: 0 26 浏览量

更新于2024-06-30

收藏 7.63MB DOCX 举报

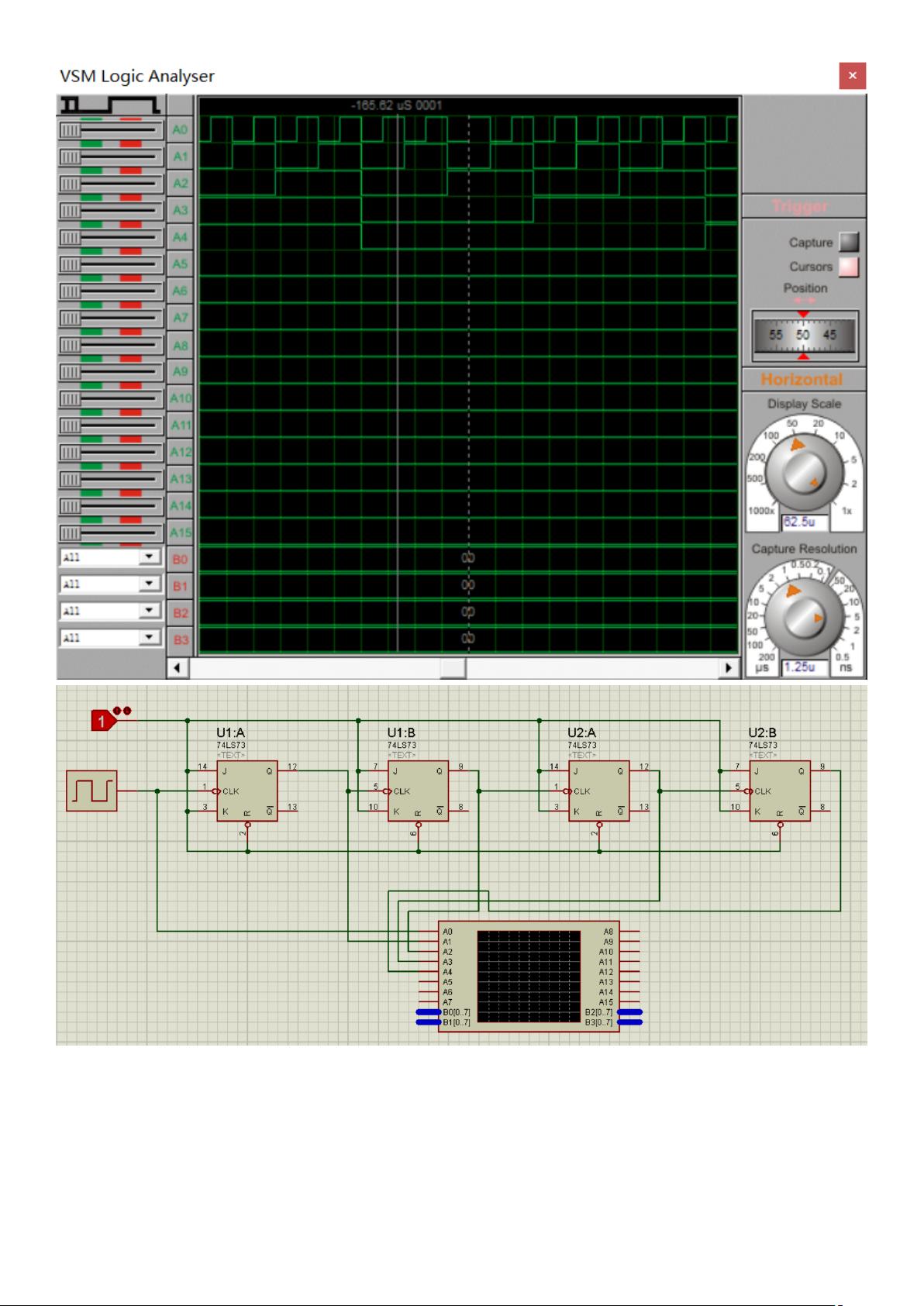

"本次实验是关于同步和异步计数器的实现,主要涉及时序逻辑电路设计,使用了J-K触发器,并通过Proteus软件进行仿真验证。实验包括设计16进制的异步加法计数器和同步计数器,观察其输出波形。"

实验十四的重点在于理解和掌握时序逻辑电路的设计和实现,特别是同步计数器与异步计数器的区别。首先,时序电路设计通常分为几个步骤:分析电路结构,列出输出和控制函数,写出状态方程,构建状态真值表,绘制状态图,以及描述电路特性。在同步时序电路设计中,逻辑抽象和状态转换图的简化尤为重要。

同步计数器和异步计数器的主要区别在于时钟信号的同步性。同步计数器的所有触发器都由同一时钟脉冲控制,而异步计数器的各触发器可能由不同时钟信号驱动,导致状态变化不同步,可能会有触发器逐级延迟的问题。同步计数器的优点在于输出变化平滑,没有尖峰,但实现起来较为复杂;异步计数器则相对简单,但输出可能存在延迟不一致的情况。

实验中,学生需要利用J-K触发器来设计16进制的计数器。J-K触发器是一种重要的时序逻辑器件,具有多种逻辑功能,可以用于构建不同类型的计数器。异步加法计数器的状态变化遵循二进制加法规则,而同步计数器则在所有触发器同时翻转时改变状态。

在Proteus软件中进行仿真,可以帮助学生直观地观察计数器的运行情况,包括时钟信号CP和计数器输出Q3、Q2、Q1、Q0的波形。这有助于理解计数器的工作原理,验证设计的正确性,并进一步优化设计。

实验内容一是设计16进制异步加法计数器,其状态变化从0000依次增加到1111,然后回零,形成循环。而实验内容二是设计16进制同步计数器,同样从0000开始,每次时钟脉冲后,状态按顺序增加,直至1111后重新回到0000。

这个实验旨在深化对时序逻辑电路的理解,尤其是同步和异步计数器的工作机制,通过实践操作和仿真实验,提高学生的电路设计能力和分析能力。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

永远的12

- 粉丝: 935

- 资源: 320

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍