计算机组成与设计第三版答案:硬件软件接口设计与实现

需积分: 9 156 浏览量

更新于2024-07-24

1

收藏 106KB PDF 举报

计算机组成与设计硬件软件接口 第三版 答案(part5)

计算机组成与设计硬件软件接口是计算机科学领域中的一门重要课程,本课题涵盖计算机系统的各个方面,包括硬件、软件、接口等。下面是根据给定文件信息生成的相关知识点:

一、计算机组成

计算机组成是指计算机系统的硬件结构,包括中央处理器(CPU)、存储器、输入/输出设备等。计算机组成的设计是计算机科学领域中的一门重要课程,涵盖了计算机系统的设计、实现和优化等方面。

在计算机组成中,指令系统是指计算机执行指令的方式和顺序。指令系统包括R-format指令、I-format指令和J-format指令等。R-format指令是指计算机执行算术逻辑单元(ALU)操作的指令,I-format指令是指计算机执行立即数操作的指令,J-format指令是指计算机执行跳转操作的指令。

二、硬件软件接口

硬件软件接口是指计算机系统中硬件和软件之间的交互方式。硬件软件接口的设计是计算机科学领域中的一门重要课程,涵盖了计算机系统的设计、实现和优化等方面。

在硬件软件接口中,寄存器(Register)是指计算机中用于存储数据的硬件组件。寄存器可以分为通用寄存器、浮点寄存器、索引寄存器等。寄存器的设计是计算机科学领域中的一门重要课程,涵盖了计算机系统的设计、实现和优化等方面。

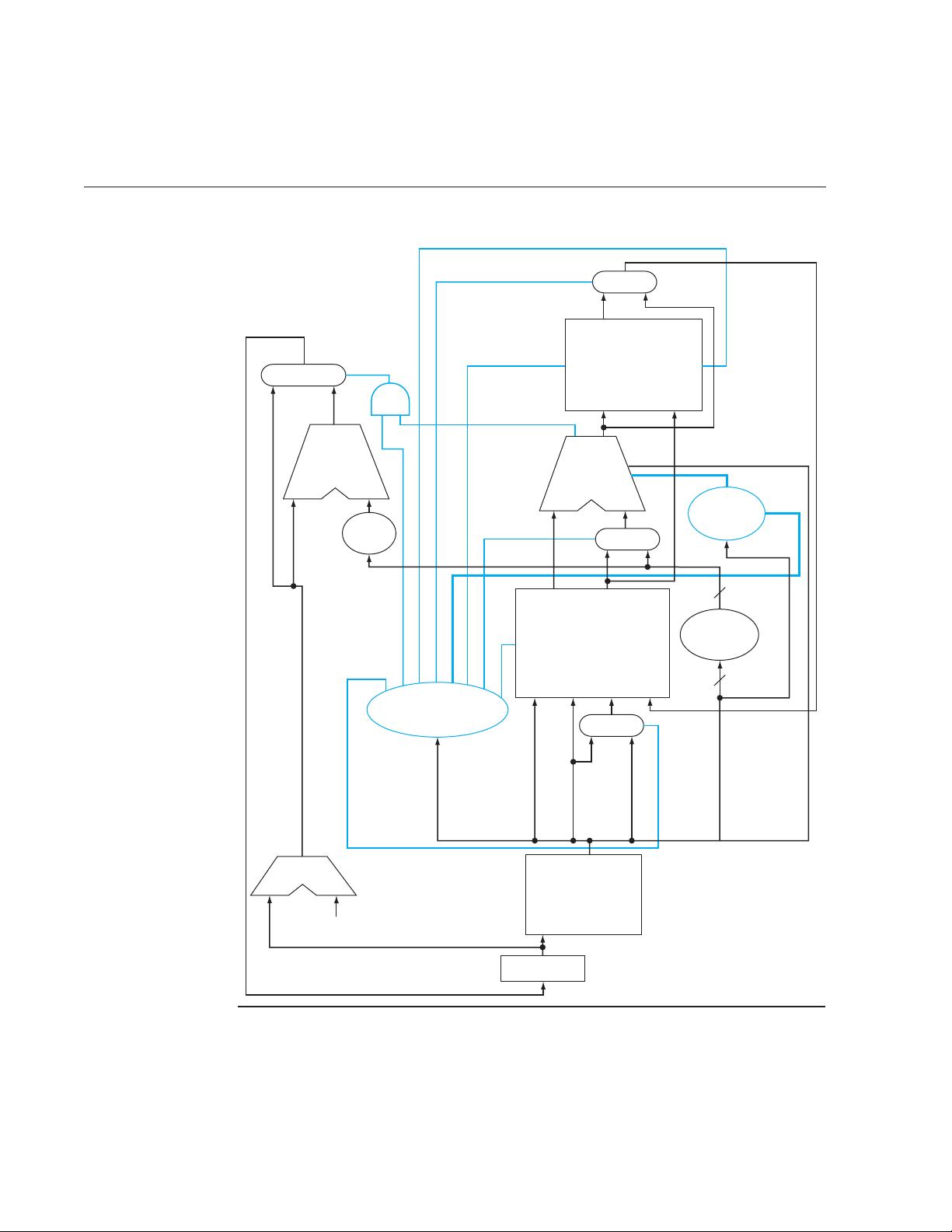

三、 Mixed sequential and combinational logic

Mixed sequential and combinational logic是指计算机系统中同时使用顺序逻辑和组合逻辑的设计方法。顺序逻辑是指计算机系统中使用 flip-flop 等寄存器来存储数据的设计方法,而组合逻辑是指计算机系统中使用逻辑门来实现逻辑操作的设计方法。

在 Mixed sequential and combinational logic中,ALU(算术逻辑单元)是指计算机系统中执行算术逻辑操作的硬件组件。ALU 的设计是计算机科学领域中的一门重要课程,涵盖了计算机系统的设计、实现和优化等方面。

四、Exercise Solutions

在给定的文件信息中,有多个练习题的答案,涵盖了计算机组成、硬件软件接口、Mixed sequential and combinational logic等方面的知识点。这些答案可以帮助学生更好地理解计算机科学领域中的相关概念和技术。

例如,在第5.1节中,练习题要求学生确定哪些指令类型属于组合逻辑、顺序逻辑或 Mixed sequential and combinational logic。答案显示,a、b、c、h、i 属于组合逻辑,f、g、j 属于顺序逻辑,而 d、e、k 属于 Mixed sequential and combinational logic。

在第5.2节中,练习题要求学生确定哪些指令类型在 RegWrite=0、ALUop1=0、ALUop0=0、Branch (or PCSrc)=0、MemRead=0、MemWrite=0 等情况下无法正确执行。答案显示,RegWrite=0 时,R-format 指令无法正确执行;ALUop1=0 时,R-format 指令除 subtract 外无法正确执行;ALUop0=0 时,beq 指令无法正确执行;Branch (or PCSrc)=0 时,beq 指令无法正确执行;MemRead=0 时,lw 指令无法正确执行;MemWrite=0 时,sw 指令无法正确执行。

计算机组成与设计硬件软件接口 第三版 答案(part5)涵盖了计算机科学领域中的多个方面,包括计算机组成、硬件软件接口、Mixed sequential and combinational logic 等。通过学习这些知识点,学生可以更好地理解计算机科学领域中的相关概念和技术。

2019-03-10 上传

2013-12-11 上传

lzhen04

- 粉丝: 2

- 资源: 6

最新资源

- small-calculator.zip_Windows编程_Visual_C++_

- book-js

- machine-learning:Java机器学习算法库

- 街机游戏项目

- CodePlayer:使用Html,Css和jQuery制作的项目。 CodePlayer是一种工具,可让您实时使用网络技术进行学习,实验和教学

- 人工智能深度学习flask服务框架.zip

- flume-http-handler:该项目适用于flume http源处理程序

- matlab人脸检测框脸代码-face-detected-opencv-nodejs:与libopencv4nodejs

- flutter-curves

- chap7.zip_VHDL/FPGA/Verilog_VHDL_

- news-extractor

- Export for Trello-crx插件

- cody:Weavora代码约定

- 项目:Primeiros passo com o projeto

- 人工智能大作业-Fashion数据集 分类.zip

- laravel_testoviy_zadaniye