FPGA优化的数字匹配滤波器在DS-CDMA同步中的应用与设计

107 浏览量

更新于2024-08-29

收藏 359KB PDF 举报

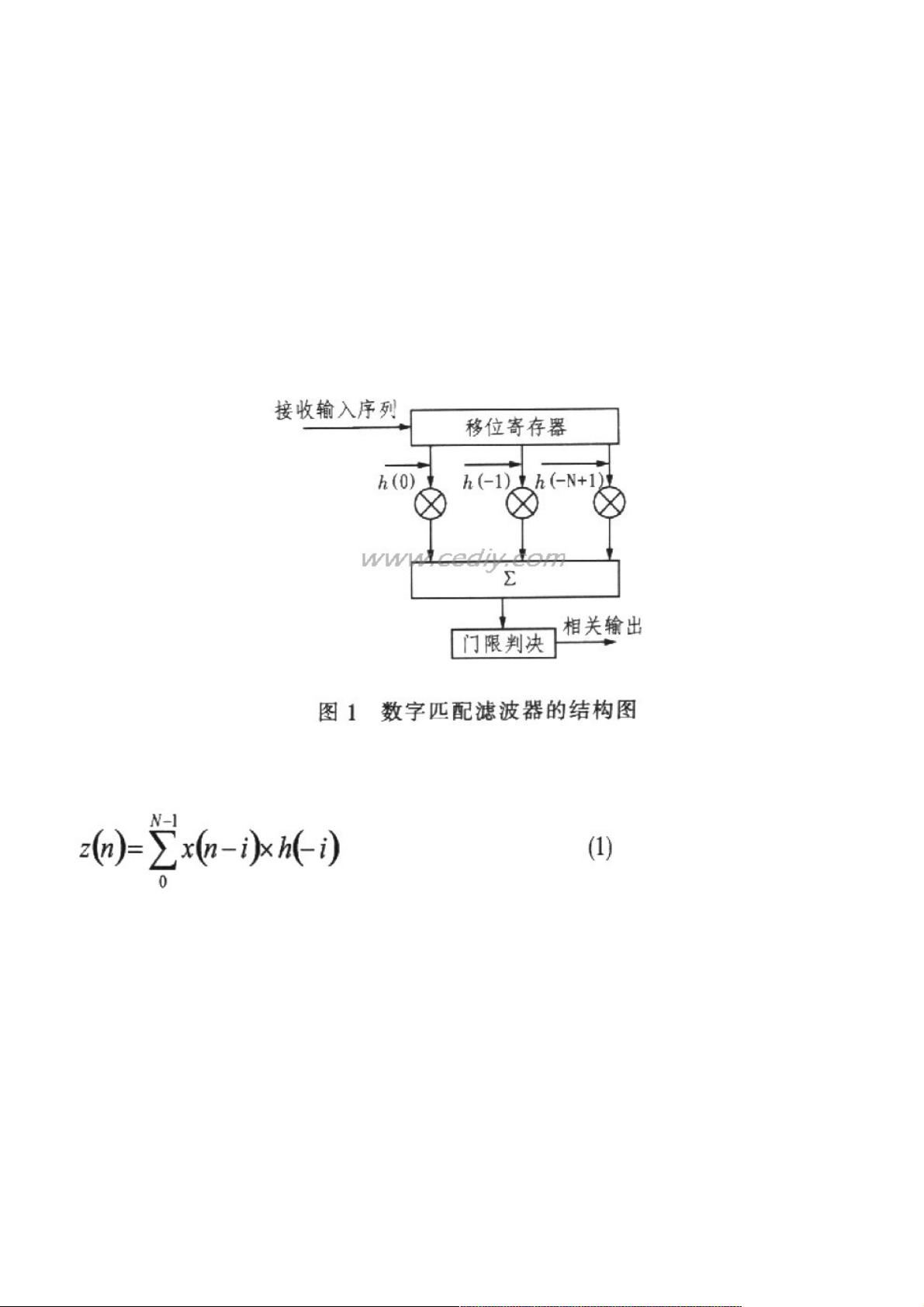

数字匹配滤波器在现代通信系统,特别是直接序列扩频(DS-CDMA)中扮演着至关重要的角色。它是一种特殊的数字滤波器,用于同步接收端与发射端的伪随机序列,如m序列,确保通信的准确性和可靠性。本文主要关注数字匹配滤波器的优化设计以及在FPGA(现场可编程门阵列)上的实现。

首先,FPGA的优势在于其灵活性和并行处理能力,使得数字匹配滤波器的设计能够在硬件层面上得到高效且资源节省的实现。在FPGA上,通过使用数字信号处理器(DSP)模块,可以实现快速的乘法和累加操作,这两个操作是数字匹配滤波器的核心,负责处理输入信号与本地扩频码的相位跟踪和同步检测。

在设计过程中,关键是要优化滤波器的长度N,即扩频比,这决定了所需的计算复杂度。理想情况下,选择合适的N可以平衡滤波精度和硬件资源消耗。此外,通过使用高效的硬件乘法器和流水线设计,可以进一步降低延迟,提升系统的实时性。

移位寄存器在数字匹配滤波器中虽然主要起到数据暂存的作用,但其在FPGA中的实现可以通过简单的时钟驱动逐位移位来完成,对资源占用的影响相对较小。然而,乘法器和累加器的优化设计则是优化整体性能的关键,因为它们直接影响到系统的性能指标,如吞吐量和功耗。

在基于FPGA的实现中,通过硬件级别的并行处理和优化的算法设计,可以显著减少硬件资源的需求,比如LUTs(Look-Up Tables)、FFs(Flip-Flops)和BRAMs(Block RAMs)。这不仅可以降低电路成本,还可以减少散热需求,从而提高整个系统的能效比。

此外,考虑到实际应用中可能遇到的多任务和实时性要求,设计者还需考虑FPGA的流水线技术和预取机制,以充分利用硬件资源,避免数据瓶颈。同时,为了确保系统的稳定性和可靠性,设计时需要进行严格的验证,包括功能验证、时序分析和温度、供电等环境适应性测试。

总结来说,数字匹配滤波器的优化设计与FPGA实现是一项结合理论与实践的复杂工作,需要对滤波器原理有深入理解,同时掌握硬件设计技巧,以期在满足性能需求的同时,最大限度地利用FPGA的特性,降低系统成本和提高效率。

101 浏览量

263 浏览量

162 浏览量

361 浏览量

145 浏览量

168 浏览量

105 浏览量

114 浏览量

132 浏览量

weixin_38618315

- 粉丝: 1

最新资源

- Ruby语言集成Mandrill API的gem开发

- 开源嵌入式qt软键盘SYSZUXpinyin可移植源代码

- Kinect2.0实现高清面部特征精确对齐技术

- React与GitHub Jobs API整合的就业搜索应用

- MATLAB傅里叶变换函数应用实例分析

- 探索鼠标悬停特效的实现与应用

- 工行捷德U盾64位驱动程序安装指南

- Apache与Tomcat整合集群配置教程

- 成为JavaScript英雄:掌握be-the-hero-master技巧

- 深入实践Java编程珠玑:第13章源代码解析

- Proficy Maintenance Gateway软件:实时维护策略助力业务变革

- HTML5图片上传与编辑控件的实现

- RTDS环境下电网STATCOM模型的应用与分析

- 掌握Matlab下偏微分方程的有限元方法解析

- Aop原理与示例程序解读

- projete大语言项目登陆页面设计与实现