Spartan 3E FPGA开发板实验:构建数字时钟发生器

需积分: 10 76 浏览量

更新于2024-09-15

收藏 145KB PDF 举报

"本次实验是基于Spartan 3E Starter Kit FPGA开发板进行的,主要目标是通过熟悉的基本逻辑组件(如触发器、计数器和多路复用器)设计电路,生成用户指定频率的方波。实验完成后,学生将掌握一种可重复使用的知识产权。"

在San Jose State University的电气工程系EE178课程中,Fall 2007学期的Crabill实验室作业第二部分,重点是简单的逻辑设计。这个实验旨在让学员运用以往课程中学到的触发器、计数器和多路复用器知识,构建一个能够根据用户输入产生特定频率方波的电路。这个设计对于理解和应用数字设计原理至关重要。

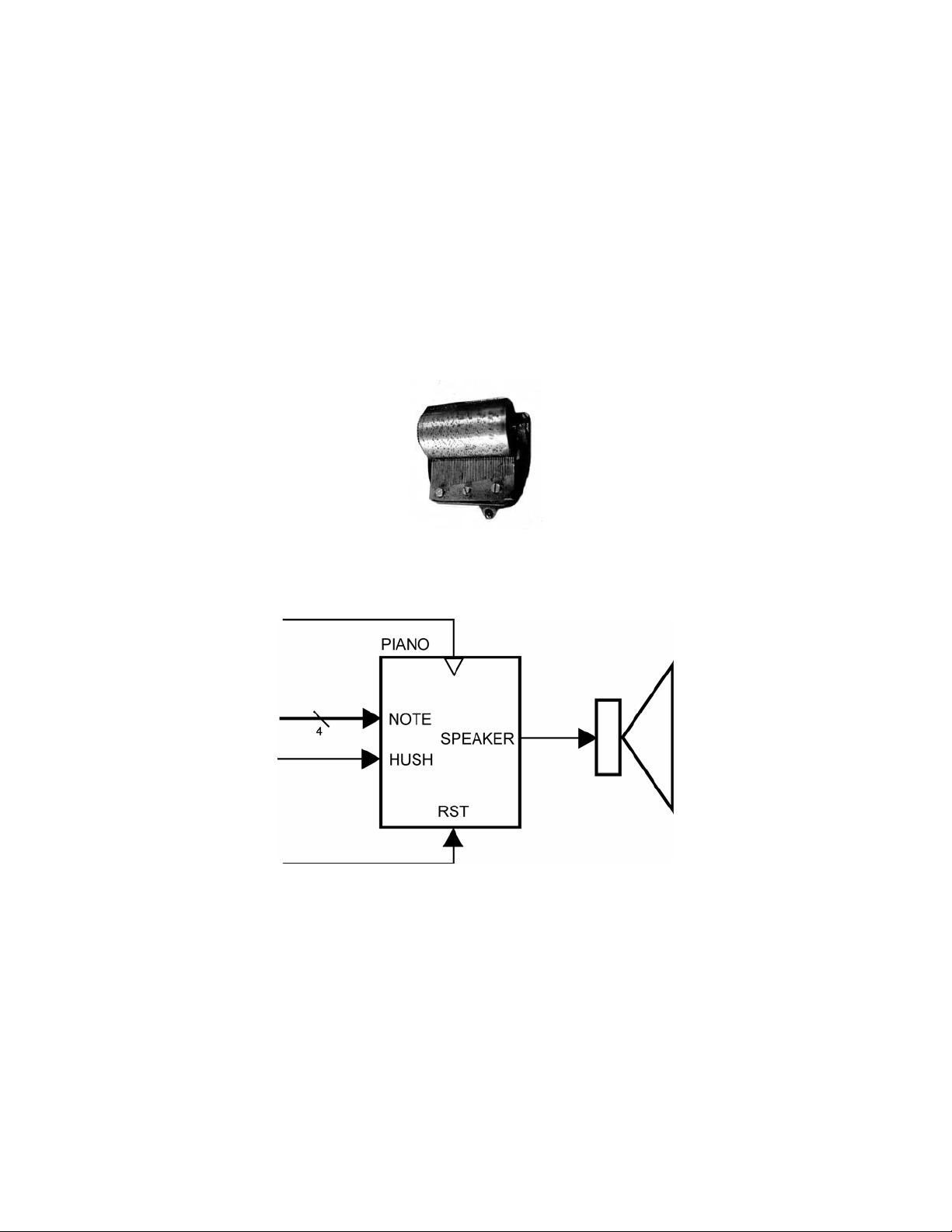

图1展示了一个机械音乐播放器的概念,而图2则提供了即将创建的模块的符号表示。这个模块设计不允许使用锁存器,只能使用一个时钟和一个异步复位信号,这将挑战学员对同步数字系统设计的理解和实践能力。

参考文献中提到了Spartan-3E Starter Kit的用户指南,它是完成这个实验的重要参考资料。在这个设计中,学员需要创建一个模块,该模块能响应时钟和异步复位信号,并且根据输入参数生成不同频率的方波。这一设计要求学员不仅要熟练掌握基本逻辑门的使用,还要理解如何将这些基本单元组合成更复杂的逻辑电路,例如计数器,以便实现频率控制。

实验步骤可能包括以下几点:

1. 理解和分析任务需求,确定所需的基本逻辑单元。

2. 设计并实现一个可以计数的电路,其计数值与生成的方波频率相关。

3. 添加异步复位功能,确保在任何时刻都能复位计数器,回到预设的起始状态。

4. 使用多路复用器根据用户的输入选择不同的计数周期,从而改变方波的频率。

5. 在硬件上验证设计,确保电路按照预期工作,产生正确的方波频率。

通过这个实验,学生不仅能巩固数字逻辑的基础知识,还能提升动手能力和问题解决技巧,为未来更复杂FPGA项目的设计和实现打下坚实基础。同时,这个设计实例也展示了FPGA在自定义逻辑电路中的灵活性,以及它在电子系统中的广泛应用潜力。

2020-12-01 上传

2020-12-05 上传

2020-12-23 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-07-27 上传

点击了解资源详情

jinzi27

- 粉丝: 0

- 资源: 6

最新资源

- Wiki-Definition-crx插件

- python官方3.9.0b4-amd64版本exe安装包

- python:Python书籍和课程

- gh-actions:体验GitHub动作

- Auto-Convert CSV to XLSX-crx插件

- pycrumbs:来自互联网的Python的点点滴滴

- Tag-Cloud-in-TipStory-Explore-Page

- 学习:劳兹的学习阶段

- FingerLock:开源密码保护器应用

- cvxpy:针对凸优化问题的Python嵌入式建模语言

- 仿网易新闻XHNewsFramework开发框架

- 聊天js插件layim.js

- nodejs-certification-training:NodeJS应用程序开发人员认证的培训概念

- gotovimvkusno

- 云雀:云雀是Python的解析工具包,专注于人体工程学,性能和模块化

- Reddit-Effect:交互式图表显示加密货币价格与Reddit上该加密货币的帖子数量