Verilog HDL设计实战:从组合逻辑到时序逻辑

版权申诉

105 浏览量

更新于2024-07-03

收藏 521KB DOCX 举报

"Verilog HDL设计练习文档包含了两个部分,分别是进阶一的组合逻辑设计练习和进阶二的时序逻辑电路设计练习。主要涉及Verilog HDL语言用于描述数字逻辑电路的方法,包括组合逻辑中的数据比较器以及时序逻辑中的基本电路设计。"

在Verilog HDL设计中,组合逻辑电路是基础,它描述了信号间的即时关系,不含有任何存储元件。练习一展示了如何设计一个简单的数据比较器。这个比较器由一个名为`compare`的模块构成,接收两个输入信号`a`和`b`,并产生一个输出`equal`。当`a`和`b`相等时,`equal`输出1,否则输出0。这个功能通过`assign`语句实现,其中`(a==b)?1:0`是条件运算符,用于在Verilog中实现分支判断。`assign`关键字用于定义非阻塞赋值,适合于组合逻辑。

测试模块`comparetest`用于验证`compare`模块的功能。它使用`initial`块来设定和改变输入信号`a`和`b`的值,并通过`#100`延迟模拟时间,使得信号变化可以被观察。`$stop`系统任务用于在特定时刻停止仿真,以便查看仿真波形。此外,练习还提出了设计一个8位字节比较器的任务,要求比较两个字节的大小并输出相应的结果。

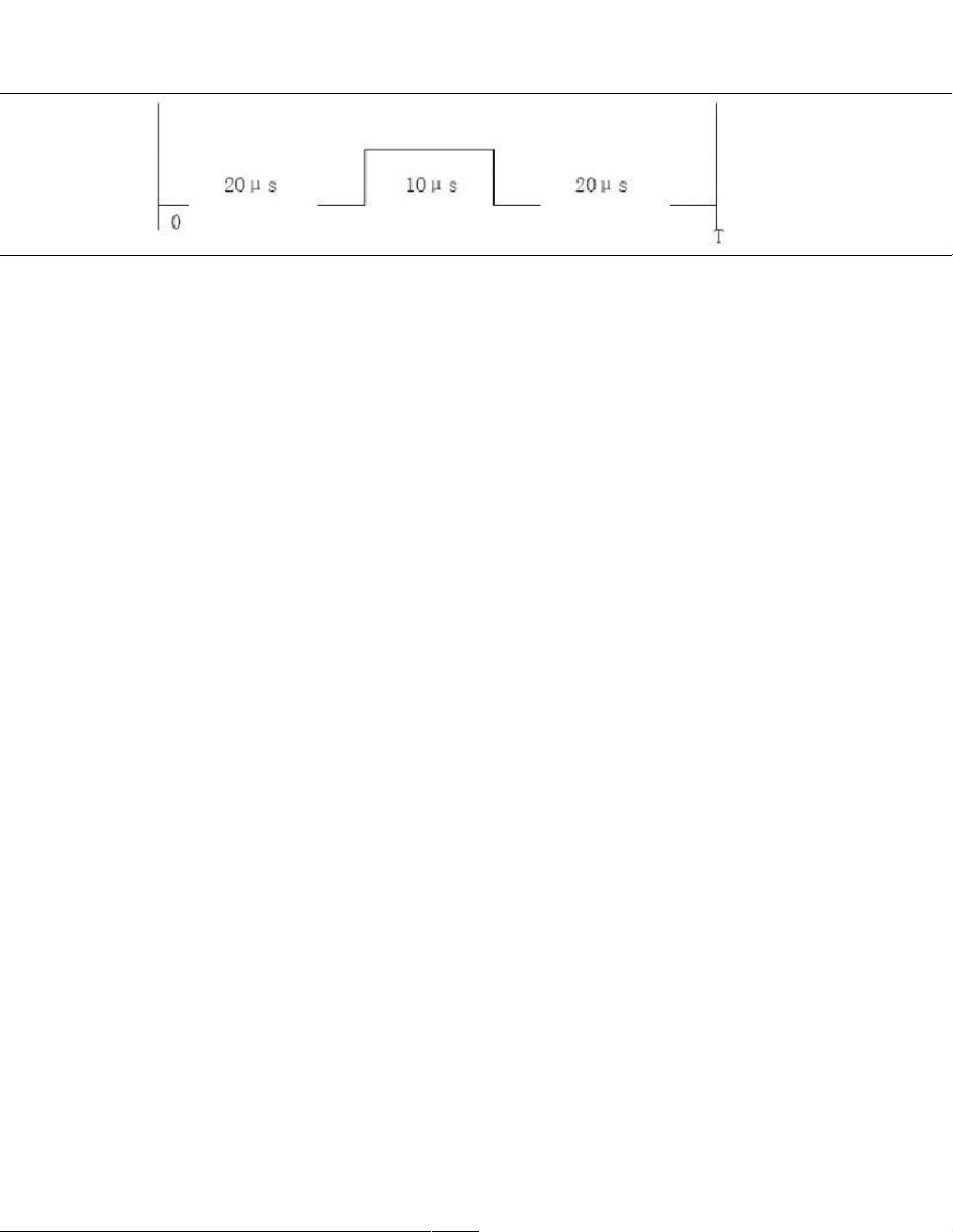

进入Verilog HDL的进阶部分,练习二关注的是时序逻辑电路设计。时序逻辑电路含有状态存储元件,如寄存器或触发器,它们的记忆特性使得设计更加复杂。虽然具体实现没有详细展开,但在Verilog中,描述时序逻辑通常会使用`always`块,尤其是含有敏感列表的`always @(posedge clk)`块,用于在时钟边沿触发更新操作。这种设计方式符合同步时序逻辑的规则,确保了电路在时钟控制下的正确工作。

这份文档提供了一个学习和实践Verilog HDL设计的良好起点,涵盖了从基本的组合逻辑到初步的时序逻辑设计,对于理解和掌握数字集成电路的Verilog描述具有重要意义。通过完成这些练习,设计师能够熟悉Verilog HDL语法,并逐步提高数字逻辑设计能力。

2021-04-25 上传

2023-03-04 上传

2022-06-20 上传

2022-06-20 上传

2022-06-16 上传

2023-03-09 上传

2022-11-02 上传

2024-04-22 上传

2023-03-05 上传

不吃鸳鸯锅

- 粉丝: 8545

- 资源: 2万+

最新资源

- Android应用源码仿支付宝九宫格解锁-IT计算机-毕业设计.zip

- BostonUnderwater:洪水检测网络 - 使用 GoogleMaps 和 Amcharts 集成记录远程洪水

- Elixir_in_action:我对《 Elixir in Action》一书中程序的实现

- 萝拉:萝拉图片网站

- Meta:Python元编程

- 基于Pytorch, 使用强化学习(自博弈+MCTS)训练一个五子棋AI.zip

- AxaTests

- WISE_ML:明智的机器学习模块

- 移动实习——基于移动终端用户画像的大规模数据过滤与性能优化研究 7.17-8.25.zip

- k8s研究

- website:个人网站

- JavaScript-Calculator

- asteroidstest

- 行业文档-设计装置-一种利用牛奶盒制作宣纸配方.zip

- flutter_practice

- nkn-monitoring:PHP(Laravel)上的一个简单的NKN节点监视GUI工具