Vivado设计流程详解:从新建工程到硬件调试

需积分: 9 142 浏览量

更新于2024-07-19

1

收藏 4.33MB PDF 举报

"Vivado设计流程手册,Xilinx全球合作伙伴,依元素科技有限公司,Artix-7核心板,FPGA基本设计流程,仿真流程,在线调试流程,配置文件固化,Vivado安装简介"

Vivado是Xilinx公司推出的一款综合型 FPGA 设计工具,它提供了全面的设计、仿真、实现和调试功能,支持从概念到硬件部署的完整设计流程。本手册重点介绍在Vivado中进行项目设计的基本步骤,适用于新手和经验丰富的开发者,尤其是那些在简单设计中使用Project Mode的用户。

设计流程主要包含以下几个关键步骤:

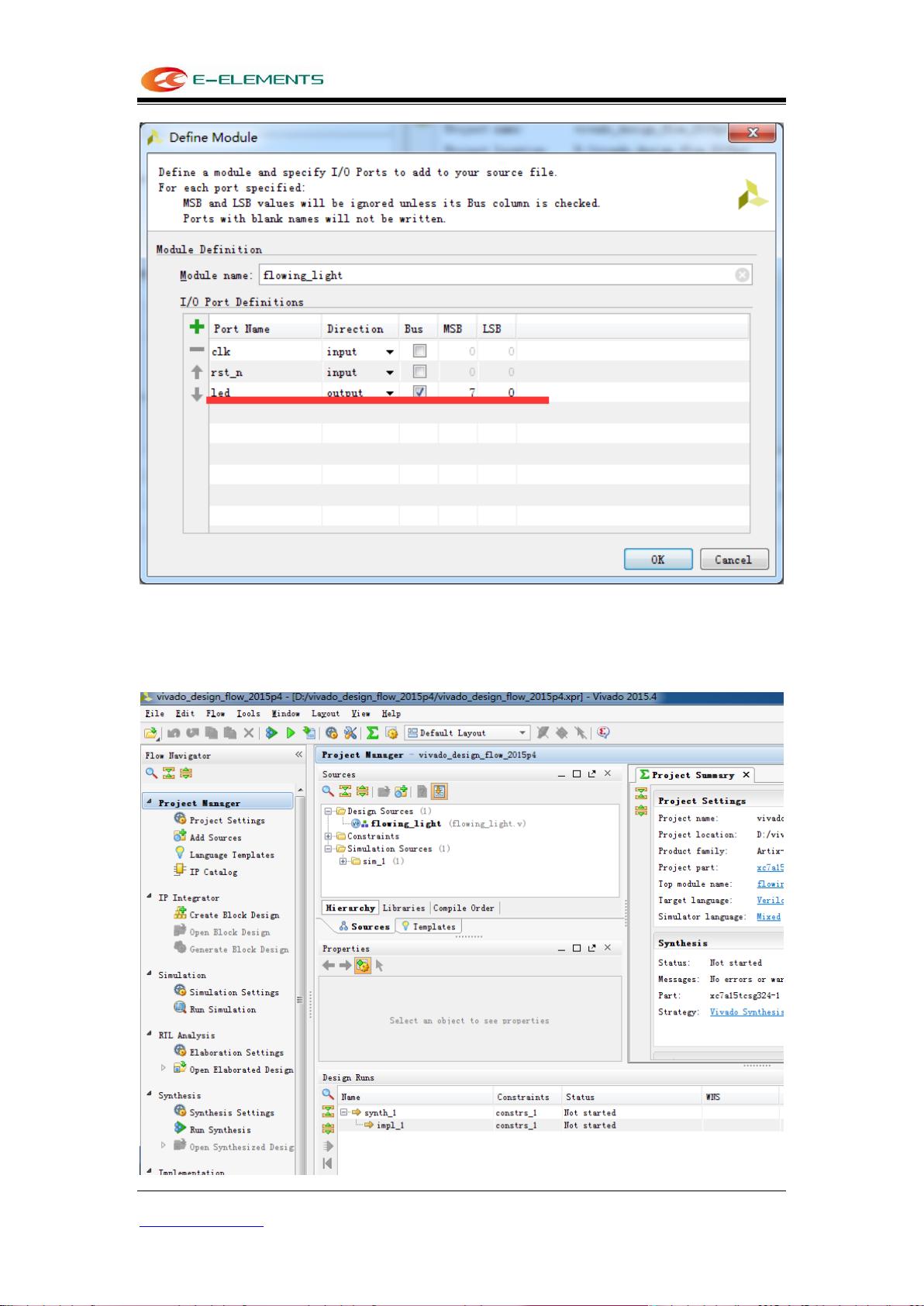

1. **新建工程**

- 启动Vivado 2015.4,通过桌面快捷方式或开始菜单打开软件。

- 点击"Create New Project",在向导中输入工程名称,选择存储路径,并勾选"Create project subdirectory"以在指定路径下创建子目录。

- 注意避免在工程名称和路径中使用中文和空格。

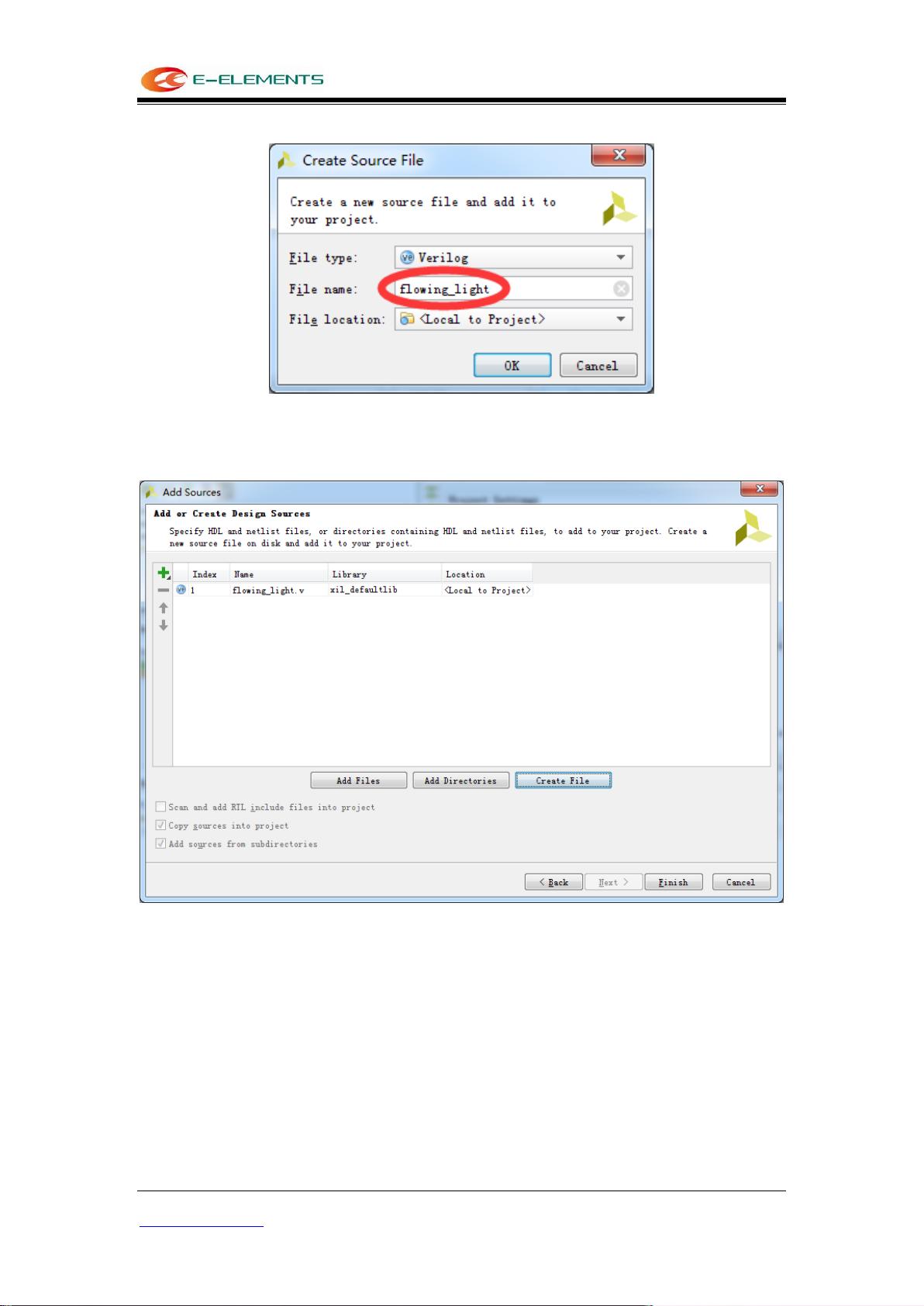

2. **设计文件输入**

- 在新建的工程中,用户可以添加源代码文件,包括VHDL、Verilog等描述硬件逻辑的语言文件。

- Vivado支持IP Integrator,用于集成和配置现成的IP核,简化设计过程。

3. **工程实现及上板验证**

- 完成设计输入后,用户可以进行综合(Synthesis)和布局布线(Place and Route),这将把高级语言描述转化为硬件电路。

- 生成比特流(Bitstream)文件,这是可以直接下载到FPGA的配置文件。

- 为了验证设计的正确性,可以通过Vivado进行硬件描述语言(HDL)仿真或者硬件在环(Hardware-in-the-Loop)仿真。

- 最后,将生成的比特流文件下载到Artix-7核心板上进行实际硬件验证。

4. **利用Vivado进行功能仿真**

- 功能仿真是设计验证的关键步骤,确保在硬件实现前逻辑工作正常。

- 用户可以创建仿真测试平台,模拟输入输出信号,观察设计在不同条件下的行为。

5. **利用Vivado进行硬件调试**

- Vivado提供强大的硬件调试工具,如SignalTap逻辑分析器,可以在运行时监测内部信号状态。

- 通过JTAG或UART等接口,可以进行在线调试,定位设计中的问题。

6. **固化配置文件**

- 配置文件固化(Bitstream Programming)是指将设计的比特流文件写入非易失性存储器,如SPI Flash,使得FPGA在上电时自动加载配置。

此外,手册还包含Vivado软件的安装指南,对于初次使用者来说,这是一个非常重要的部分,因为正确的安装和配置是顺利进行设计的前提。

总结,本手册详尽地介绍了使用Vivado进行FPGA设计的全过程,从创建项目、输入设计、实现、仿真到调试和固化的每一个环节,为读者提供了一个清晰的学习路径,确保能够有效地理解和应用Vivado工具进行FPGA开发。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2015-05-29 上传

2019-04-12 上传

2018-08-12 上传

2023-06-10 上传

2024-05-14 上传

2024-10-14 上传

mr9612

- 粉丝: 0

- 资源: 1

最新资源

- FACTORADIC:获得一个数字的阶乘基数表示。-matlab开发

- APIPlatform:API接口平台主页接口调用网站原始码(含数十项接口)

- morf源代码.zip

- 参考资料-附件2 盖洛普Q12 员工敬业度调查(优秀经理与敬业员工).zip

- MyJobs:Yanhui Wang 使用 itemMirror 和 Dropbox 管理作业的 SPA

- SiFUtilities

- PrivateSchoolManagementApplication:与db连接的控制台应用程序

- python-sdk:MercadoLibre的Python SDK

- Docket-App:笔记本Web应用程序

- Crawler-Parallel:C语言并行爬虫(epoll),爬取服务器的16W个有效网页,通过爬取页面源代码进行确定性自动机匹配和布隆过滤器去重,对链接编号并写入url.txt文件,并通过中间文件和三叉树去除掉状态码非200的链接关系,将正确的链接关系继续写入url.txt

- plotgantt:从 Matlab 结构绘制甘特图。-matlab开发

- 【精品推荐】智慧体育馆大数据智慧体育馆信息化解决方案汇总共5份.zip

- tsu津

- houdini-samples:各种Houdini API的演示

- parser-py:Python的子孙后代工具

- proton:Vue.js的无渲染UI组件的集合