Piccolo™ Microcontrollers TMS320F2803x 技术手册

需积分: 24 186 浏览量

更新于2024-07-09

收藏 1.5MB PDF 举报

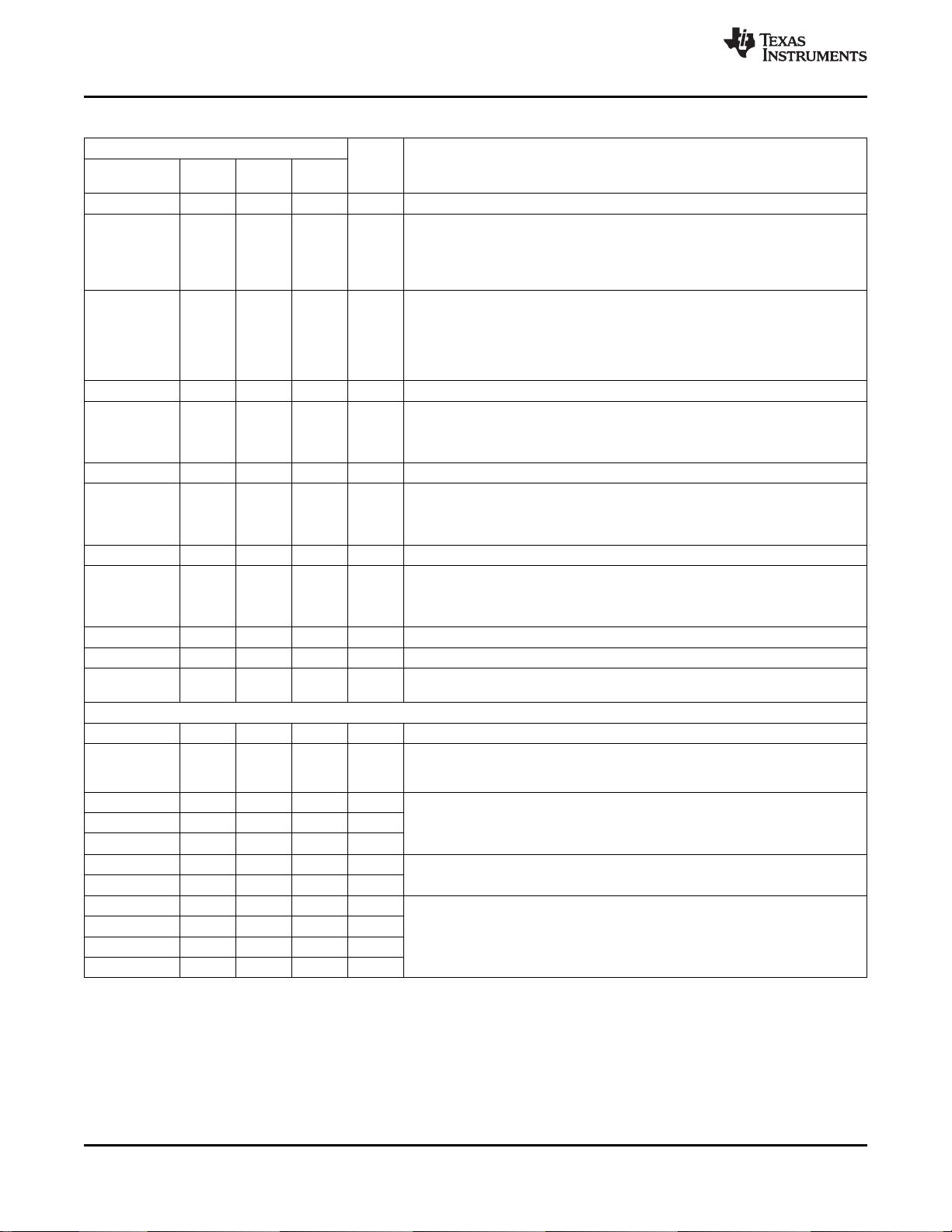

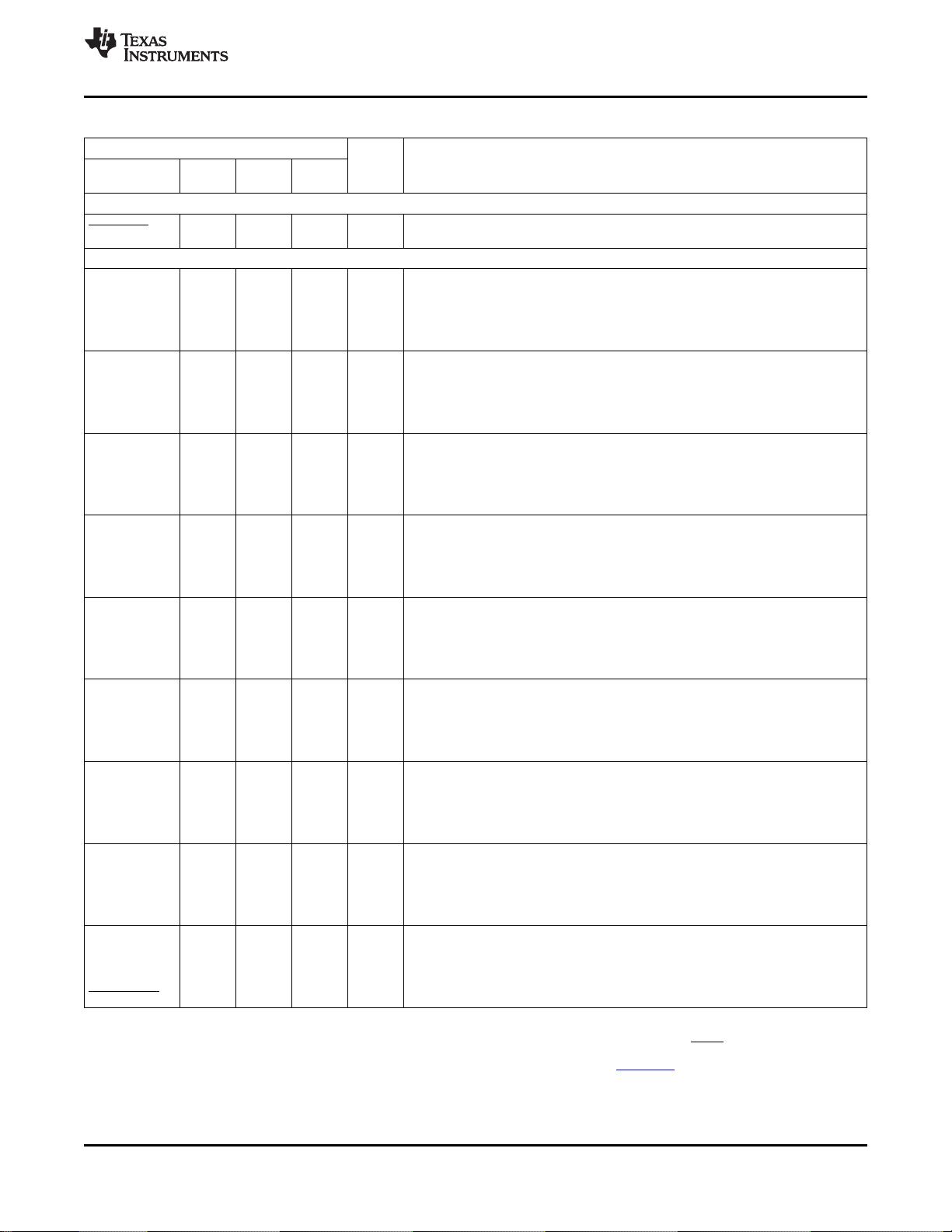

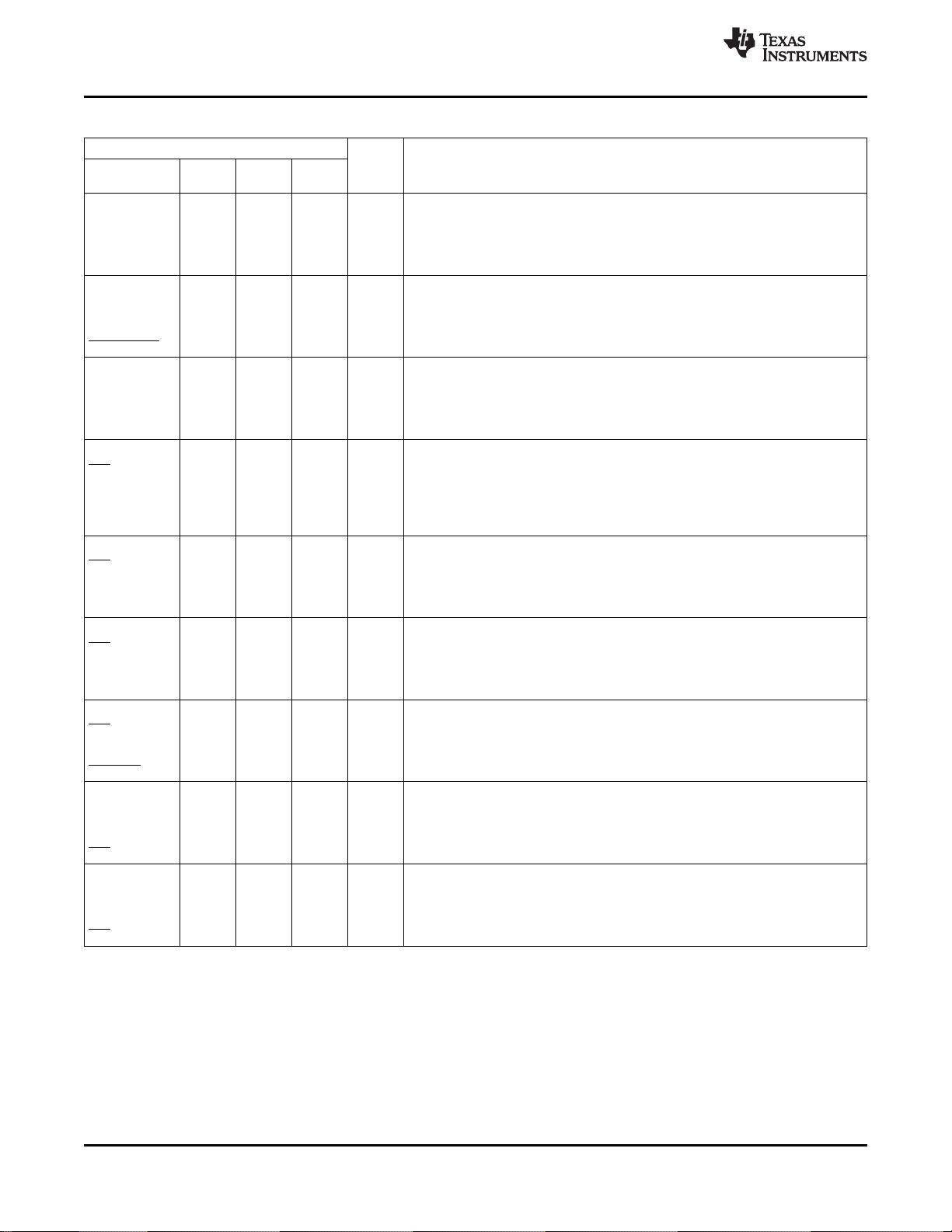

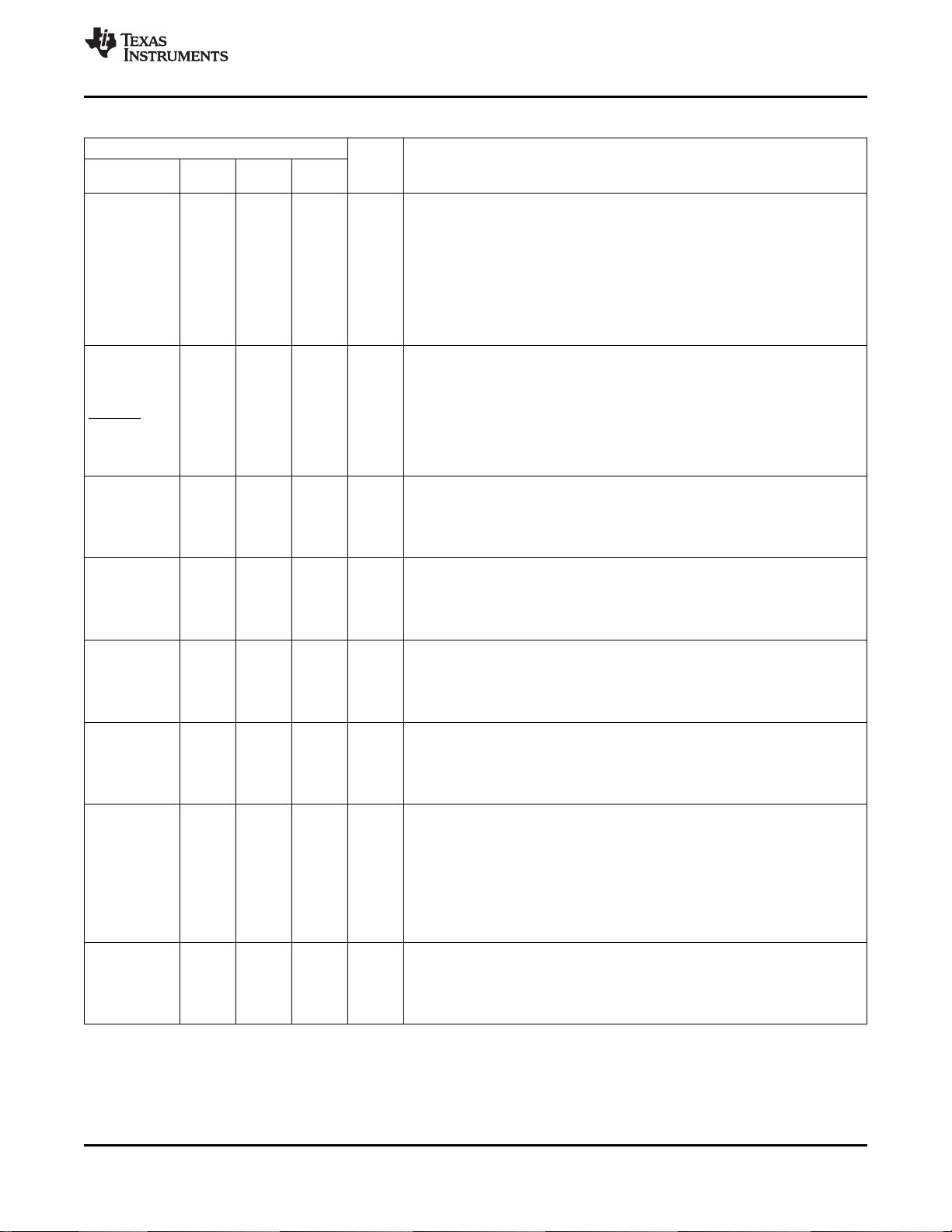

"TMS320F2803x是德州仪器(TI)推出的Piccolo系列微控制器,包括TMS320F28030、TMS320F28031、TMS320F28032、TMS320F28033、TMS320F28034和TMS320F28035等型号。这款微控制器集成了高效的32位TMS320C28x CPU,具有强大的性能和丰富的外设接口。"

TMS320F2803x系列微控制器是TI的Piccolo家族成员,专为高效能应用设计。它们的核心是一个32位TMS320C28x CPU,该CPU以其高效率和快速处理能力著称,能够处理复杂的实时控制任务。该系列微控制器的时钟频率可达60MHz,对应16.67-ns的周期时间,确保了高速的数据处理和响应。

在中断管理方面,TMS320F2803x配备了一个Peripheral Interrupt Expansion (PIE) 块,支持所有外围设备中断。这增强了系统的灵活性和实时性能,能够迅速响应来自不同外设的中断请求。

在定时器功能上,这些微控制器内置了三个32位CPU定时器,支持16x16和32x32的乘法累加操作。每个PWM(脉宽调制)通道还有一个独立的16位定时器,并且包含了16x16双MAC模块。此外,它采用了哈佛总线架构,将程序存储器和数据存储器分开,提高了数据访问速度。

在内存配置上,TMS320F2803x提供了片上Flash、SARAM、OTP和BootROM,支持原子操作。其快速中断响应和处理能力确保了系统的高效运行。同时,微控制器还集成了代码安全模块,以128位安全密钥/锁保护固件,防止逆向工程,确保了代码的安全性和私密性。

TMS320F2803x系列还拥有一个可编程的Control Law Accelerator (CLA),这是一个32位浮点数学加速器,可以在主CPU执行任务的同时独立运行,用于提升计算密集型任务的处理能力。CLA对于实时控制系统如PID控制非常有用,可以显著提高系统的响应速度。

通信接口方面,TMS320F2803x带有串行端口外设,例如SCI(UART),能够实现与外部设备的独立通信,扩展了系统的网络和控制能力。

总体而言,TMS320F2803x微控制器是适用于工业自动化、电机控制、能源管理等多个领域的高性能解决方案,其集成的特性使得开发人员能够在满足严格实时性能需求的同时,兼顾代码的效率和安全性。

2020-05-13 上传

2015-11-24 上传

2023-12-11 上传

2023-07-27 上传

2023-12-31 上传

2023-08-02 上传

2023-09-05 上传

2023-06-24 上传

我的未来不是梦735

- 粉丝: 0

- 资源: 1

最新资源

- SSM动力电池数据管理系统源码及数据库详解

- R语言桑基图绘制与SCI图输入文件代码分析

- Linux下Sakagari Hurricane翻译工作:cpktools的使用教程

- prettybench: 让 Go 基准测试结果更易读

- Python官方文档查询库,提升开发效率与时间节约

- 基于Django的Python就业系统毕设源码

- 高并发下的SpringBoot与Nginx+Redis会话共享解决方案

- 构建问答游戏:Node.js与Express.js实战教程

- MATLAB在旅行商问题中的应用与优化方法研究

- OMAPL138 DSP平台UPP接口编程实践

- 杰克逊维尔非营利地基工程的VMS项目介绍

- 宠物猫企业网站模板PHP源码下载

- 52简易计算器源码解析与下载指南

- 探索Node.js v6.2.1 - 事件驱动的高性能Web服务器环境

- 找回WinSCP密码的神器:winscppasswd工具介绍

- xctools:解析Xcode命令行工具输出的Ruby库