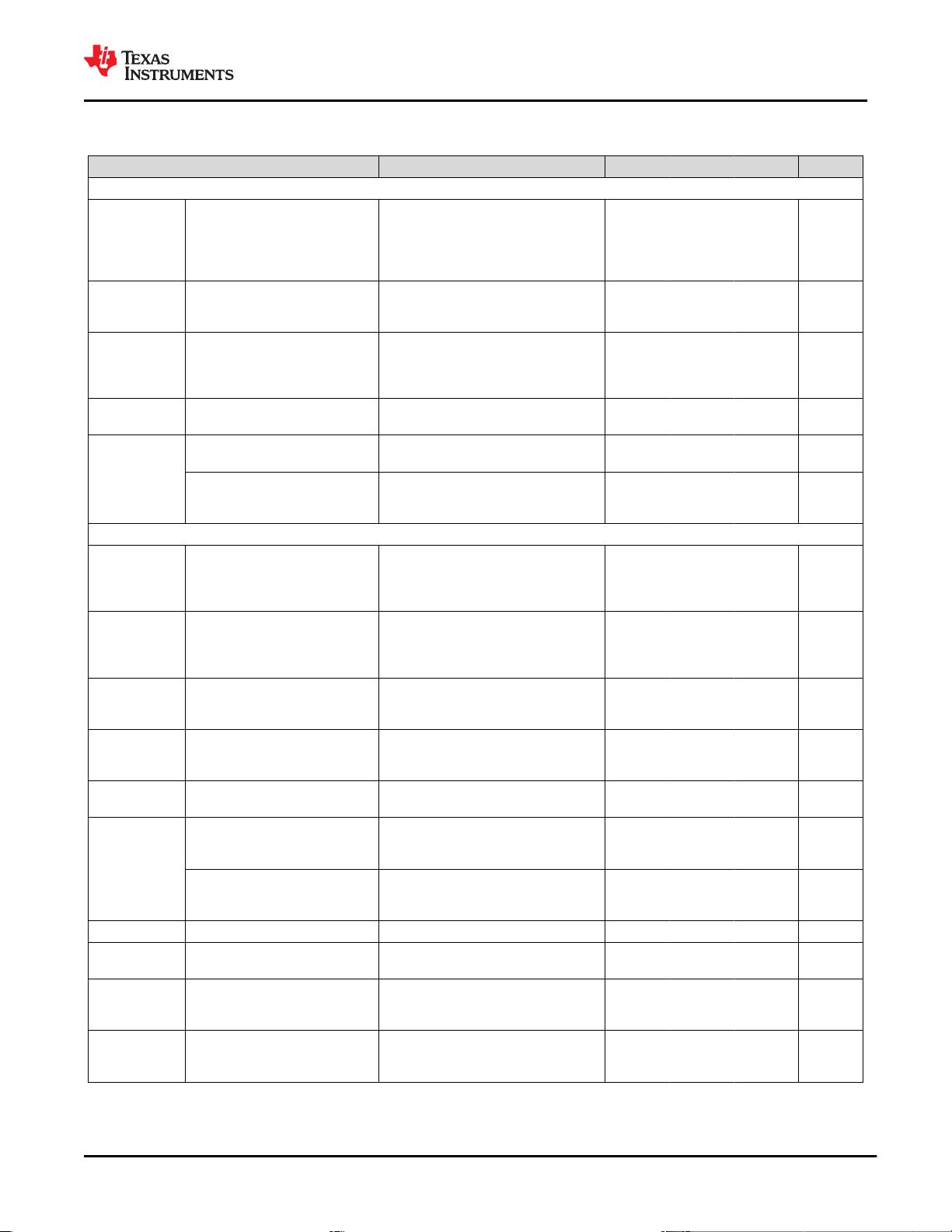

7.5 Electrical Characteristics (continued)

Over Recommended Operating Conditions (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Other Characteristics

t

PHO-VAR

Input-to-output phase offset

variation over PVT

Zero delay mode, RF clocks only, INx =

122.88 MHz, OUTx = 2949.12 MHz or

2457.6 MHz or 1474.56 MHz or 1228.8

MHz or 737.28 MHz or 614.4 MHz or

153.6 MHz or 122.88 MHz

-200 200 ps

t

ANA-DEL-ERR

Analog delay error for any step

setting

(9)

VCBO = 2457.6 MHz, PLL3_PRI_DIV =

÷5, OUTx = 491.52 MHz, Analog Delay

step = 32.8 ps

-16 16 ps

t

DIG-DEL

Digital delay step size on device

clock and SYSREF outputs

SYSREF analog delay off for half cycle

steps and

OUT_x_y_SR_CH_DIV_BYPASS = 1

½ VCO

post

divider

cycle

PSNR

Spur induced by power supply

noise (V

N

= 50 mVpp)

(5)

(6)

Vcc = 3.3V, HSDS, LVDS, and LVPECL

output

-75 dBc

SPUR

Highest Spur level at 100 Hz to

40 MHz offset

(6)

(7)

f

OUTx

= 122.88 MHz from VCO3, VCO2

= 5625 MHz, and VCO1 = 5000 MHz

-90 dBc

Highest spur level within12 kHz to

40 MHz band

(6)

(7)

f

OUTx

= 122.88 MHz, AC-DIFF or LVDS

(all outputs operating with differential

level and no SYSREF)

-75 dBc

PLL Clock Output Performance Characteristics

RJ1

RMS phase jitter of DPLL1/

APLL1 (12 kHz to 20 MHz)

(3)

(7)

XO = 38.88 MHz, APLL1 = 5000 MHz

or 5156.25 MHz, OUTx = 312.5 or

322.265625 MHz, all differential output

types

200 250 fs RMS

RJ2

RMS phase jitter of DPLL2/

APLL2 (12 kHz to 20 MHz)

(3)

(7)

XO = 38.88 MHz, APLL2 = 5898.24

MHz or 5650 MHz, OUTx = 245.76

MHz or 312.5 MHz, all differential

output types

120 180 fs RMS

RJ3

RMS phase jitter of DPLL3/

APLL3 (12 kHz to 20 MHz)

(3)

(7)

XO = 38.88 MHz, APLL3 = 2457.6

MHz, OUTx = 245.76 MHz, all

differential output types

50 80 fs RMS

RJ4

RMS phase jitter of DPLL3/

APLL3 (12 kHz to 20 MHz)

(3)

(7)

XO = 38.88 MHz, APLL3 = 2457.6

MHz, OUTx = 491.52 MHz, all

differential output types

40 70 fs RMS

PN-APLL3

Phase Noise of DPLL3/APLL3 at

800 kHz offset

38.88 MHz XO, VCO3 = 2457.6 MHz,

2457.6 MHz CML output

-147 dBc/Hz

PN

TDC

Output close-in phase noise for

DPLL1 and DPLL2

(f

OFFSET

= 100 Hz)

122.88 MHz AC-DIFF or LVDS, TCXO

= 38.88 MHz, f

TDC

> 20 MHz, DPLL-

BW = 1 kHz

-116 dBc/Hz

Output close-in phase noise for

DPLL3

(f

OFFSET

= 100 Hz)

122.88 MHz AC-DIFF or LVDS, TCXO

= 38.88 MHz, f

TDC

> 20 MHz, DPLL-

BW = 1 kHz

-110 dBc/Hz

BW DPLL bandwidth range

(8)

Programmed bandwidth setting 0.01 4000 Hz

J

PK

DPLL closed-loop jitter

peaking

(11)

f

IN

= 25 MHz, f

OUT

= 10 MHz, DPLL BW

= 0.1 Hz or 10 Hz

0.1 dB

J

TOL

Jitter tolerance

Compliant with G.8262 Options 1 and

2, Jitter modulation = 10 Hz, 25.78125

Gbps

6455 UI p-p

t

HITLESS

Phase transient during hitless

switch

Valid for a single switchover event

between two clock inputs at the same

frequency 122.88 MHz

-100 100 ps

www.ti.com.cn

LMK5C33216

ZHCSMJ6B – NOVEMBER 2020 – REVISED MARCH 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

15

Product Folder Links: LMK5C33216