半导体集成电路考试重点:试题解析与关键概念

版权申诉

《半导体集成电路》是一份包含考试题目及参考答案的学习资料,涵盖了半导体集成电路的基础概念、制造工艺、晶体管寄生效应、无源元件和TTL电路等多个主题。

【知识点详解】

1. **半导体集成电路**:是将大量电子元器件(如晶体管、电阻、电容等)集成在一个小芯片上的电路,显著提高了电子设备的性能和可靠性。

2. **集成度分类**:根据集成度,半导体集成电路可分为小规模集成电路(SSI)、中规模集成电路(MSI)、大规模集成电路(LSI)、超大规模集成电路(VLSI)和极大规模集成电路(ULSI)。对应的英文缩写分别为SSI、MSI、LSI、VLSI、ULSI。

3. **器件类型分类**:主要分为双极型集成电路(BJT)和金属-氧化物-半导体场效应晶体管集成电路(MOSFET),还有二者的混合型——BiCMOS。

4. **按功能或信号类型分类**:包括模拟集成电路、数字集成电路、混合信号集成电路等,分别处理连续变化的模拟信号和离散的数字信号,或两者混合的信号。

5. **特征尺寸**:是集成电路中最小的几何尺寸,直接影响芯片的集成度和性能。随着特征尺寸减小,可实现更高的集成度,但也会带来工艺挑战和量子效应。

6. **集成度、wafer size、die size、摩尔定律**:集成度指单位面积上集成的元器件数量;wafer size是指晶圆的直径,通常用于生产过程;die size是每个集成电路芯片的大小;摩尔定律指出,集成电路上的晶体管数目大约每两年翻一番。

7. **双极型晶体管制造**:隐埋层有助于提高晶体管的电流控制能力和稳定性;衬底材料电阻率的选择影响器件的噪声性能和功耗。

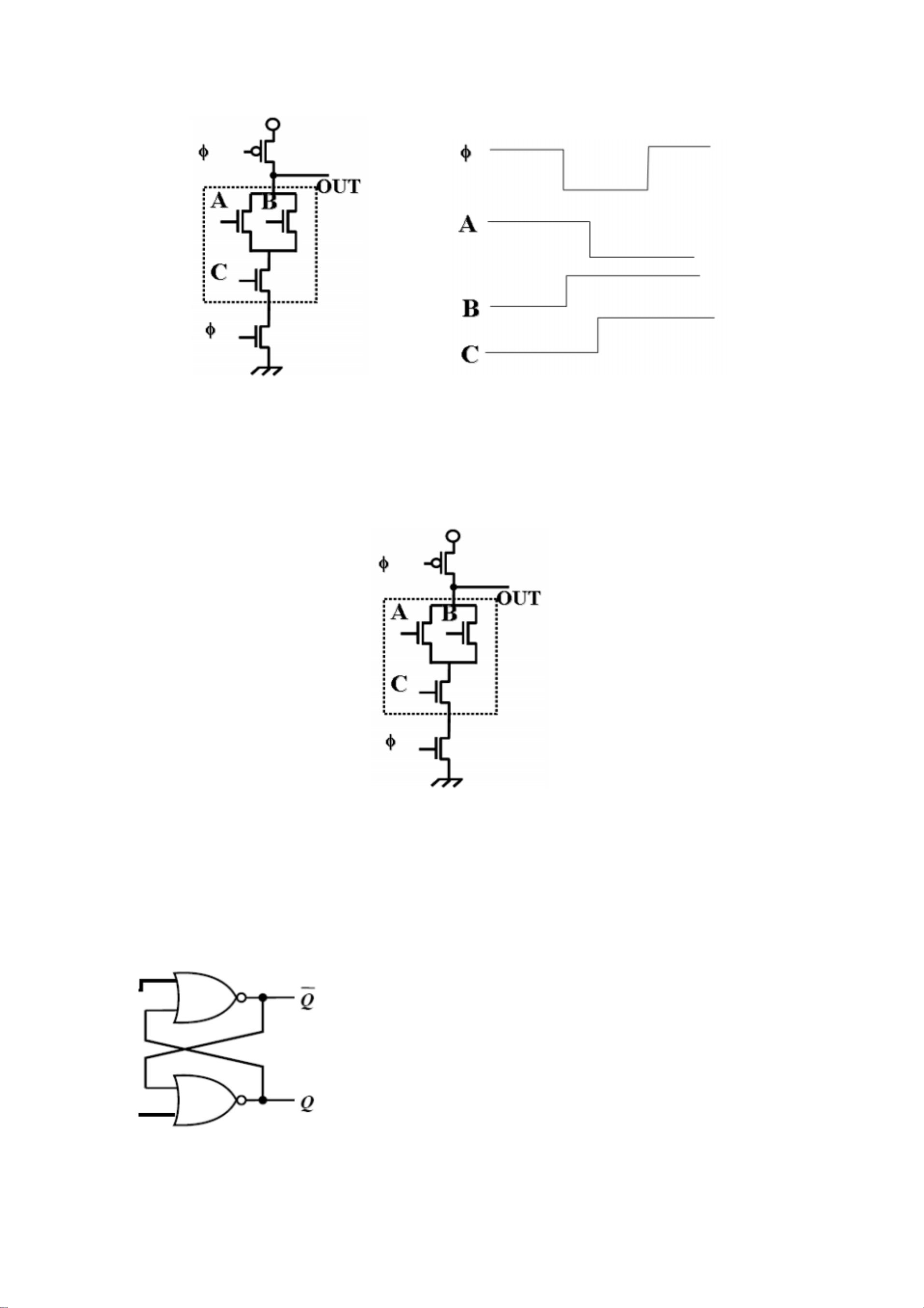

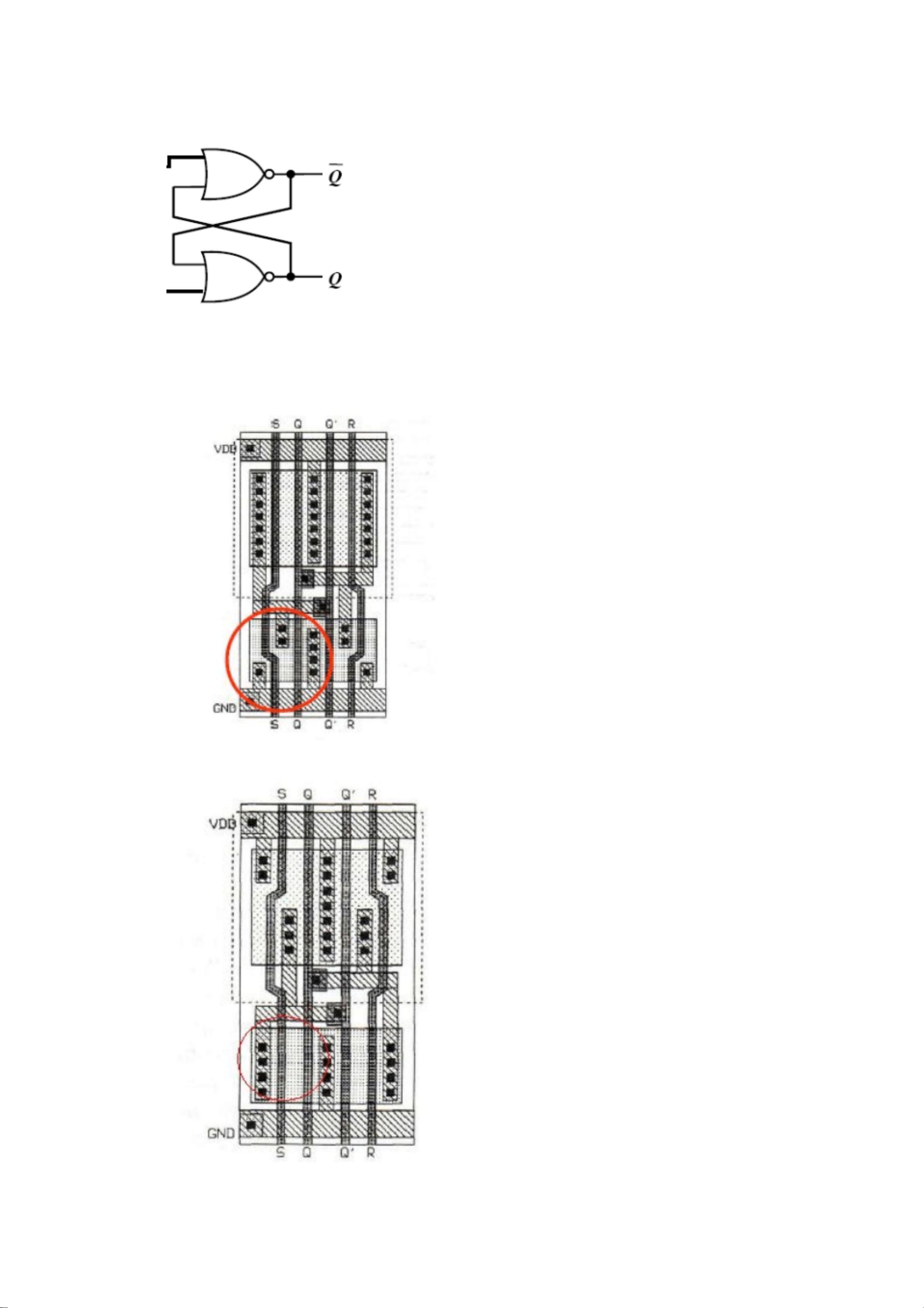

8. **光刻步骤**:pn结隔离的NPN晶体管和硅栅p阱CMOS的光刻过程涉及图形转移、光刻胶涂布、曝光、显影、蚀刻等步骤,用于形成晶体管结构。

9. **BiCMOS工艺**:结合了BJT和MOSFET的优点,但p阱CMOS基底的BiCMOS存在热载流子效应,而N阱CMOS工艺则可能导致阈值电压漂移,改进方法包括优化掺杂和工艺参数。

10. **晶体管寄生效应**:集成双极晶体管和MOS晶体管在工作时可能受到有源和无源寄生效应的影响,如MOS晶体管的闩锁效应,可能导致器件损坏。解决方法包括设计优化和增加保护电路。

11. **无源元件**:双极性集成电路中的电阻多采用基区扩散电阻,MOS集成电路中常用多晶硅电阻。电阻修正考虑了薄层电阻效应;铜布线取代铝布线是因为铜有更好的电导率和抗电迁移能力。

12. **TTL电路**:TTL电路是数字逻辑电路的一种,包括电压传输特性、开关速度参数(如延迟时间)等,四管标准TTL与非门中,输入电平的精确控制对瞬态特性至关重要,而两管与非门在电源噪声和温度变化下性能不稳定,因此常使用更多管子以提高稳定性和抗干扰能力。

这份资料详细介绍了半导体集成电路的各个方面,对于学习者来说,既是复习材料也是深入理解的参考资料。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-12-09 上传

2021-12-09 上传

2021-12-02 上传

2021-11-01 上传

2021-12-01 上传

2021-10-10 上传

lzx13599381087

- 粉丝: 2

- 资源: 9万+

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录