掌握第四章:时序逻辑电路触发器与设计详解

版权申诉

44 浏览量

更新于2024-07-01

收藏 1.63MB PDF 举报

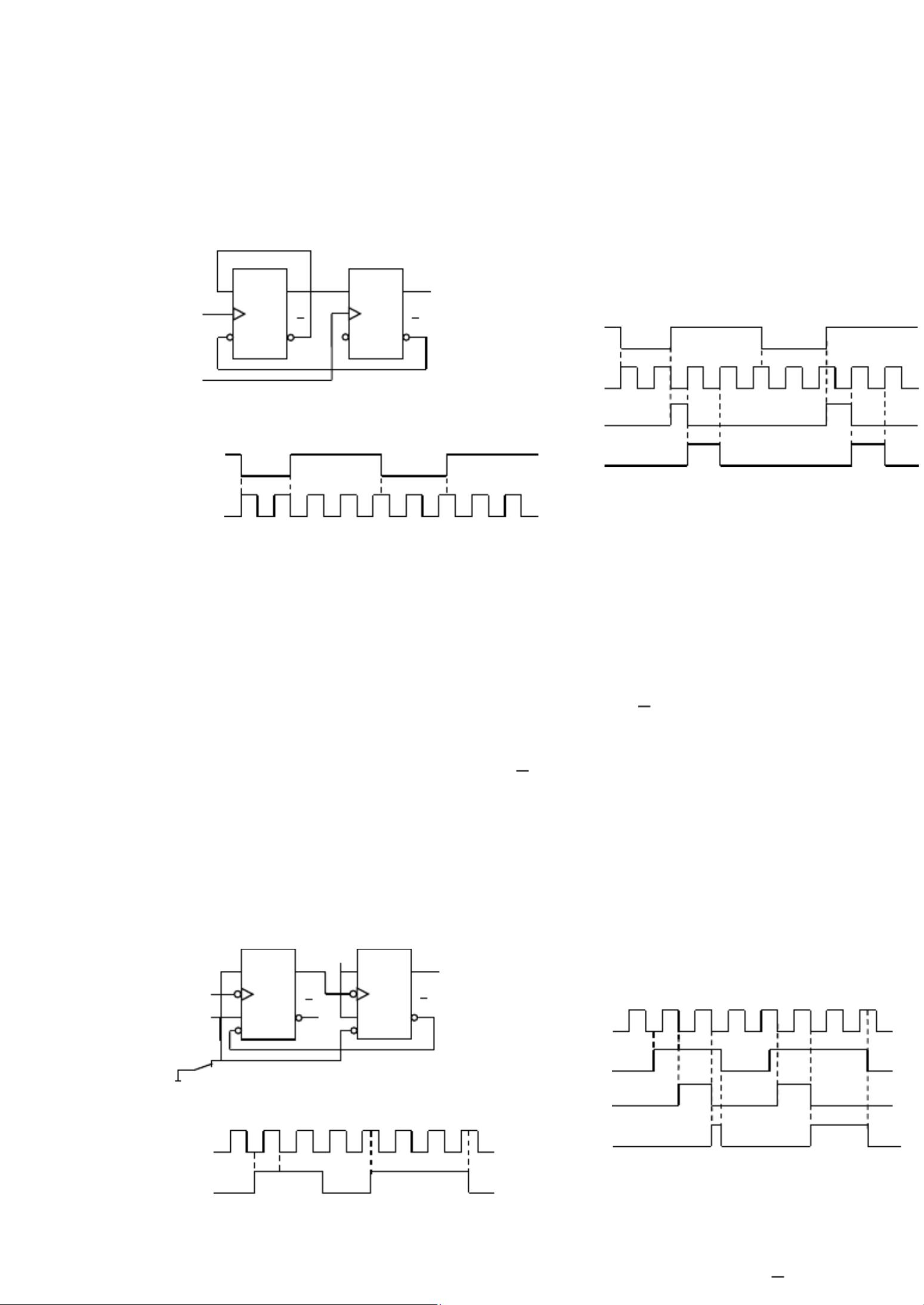

第四章时序逻辑电路是数字电路中的核心部分,它主要探讨了触发器和时序逻辑电路的基础理论及应用。触发器作为时序逻辑电路的基础元件,其特点是具有记忆功能,即输出不仅取决于当前输入信号,还依赖于前一状态。触发器的种类繁多,包括电位触发、主从触发和边沿触发等不同类型,如RS触发器、D触发器、JK触发器和T触发器,它们各自有独特的逻辑功能和工作模式。

其中,基本RS触发器是最简单的形式,没有独立的时钟脉冲,输入信号S和R直接控制输出状态。当输入信号变化时,输出状态会立即响应。同步RS触发器则引入了时钟信号CP,只有在CP为高电平时,触发器才会根据输入信号进行状态更新,避免了"空翻"现象,这是电平触发方式的一个重要特性。主从RS触发器则是由一个主触发器控制多个从触发器,常用于实现复杂的时序逻辑电路。

时序逻辑电路的基本概念涵盖了电路的分析和设计方法,这些方法包括状态转换表、激励表、特征方程、状态转换图和时序图等工具,通过这些手段可以准确描述触发器和其他时序电路的工作过程和行为规律。学习这一章对于理解如何构建和分析具有特定功能的中规模时序电路至关重要,为后续深入研究奠定了坚实的基础。

理解并掌握这些概念和技巧,能够帮助电子工程师设计和调试各种实际应用中的数字电路,例如计数器、寄存器、移位寄存器等,这些都是现代信息技术系统不可或缺的组成部分。因此,对于从事电子工程或者希望深入了解数字电路的人来说,理解时序逻辑电路是必不可少的技能。

2022-07-13 上传

2022-07-09 上传

2022-10-17 上传

2022-07-09 上传

2022-07-13 上传

2021-12-05 上传

2023-08-05 上传

2021-10-04 上传

xxpr_ybgg

- 粉丝: 6718

- 资源: 3万+

最新资源

- C语言快速排序算法的实现与应用

- KityFormula 编辑器压缩包功能解析

- 离线搭建Kubernetes 1.17.0集群教程与资源包分享

- Java毕业设计教学平台完整教程与源码

- 综合数据集汇总:浏览记录与市场研究分析

- STM32智能家居控制系统:创新设计与无线通讯

- 深入浅出C++20标准:四大新特性解析

- Real-ESRGAN: 开源项目提升图像超分辨率技术

- 植物大战僵尸杂交版v2.0.88:新元素新挑战

- 掌握数据分析核心模型,预测未来不是梦

- Android平台蓝牙HC-06/08模块数据交互技巧

- Python源码分享:计算100至200之间的所有素数

- 免费视频修复利器:Digital Video Repair

- Chrome浏览器新版本Adblock Plus插件发布

- GifSplitter:Linux下GIF转BMP的核心工具

- Vue.js开发教程:全面学习资源指南