AXI PCIe Gen3子系统产品指南

需积分: 50 156 浏览量

更新于2024-07-06

收藏 3.05MB PDF 举报

"AXI Bridge for PCI Express Gen3 Subsystem v3.0 是一款基于Vivado Design Suite的IP核,用于在FPGA中实现PCI Express(PCIe)第三世代的接口桥接。该产品指南详细介绍了IP的核心特性、规格、设计流程以及示例设计,帮助用户理解和使用此桥接解决方案。"

此文档详细阐述了AXI Bridge for PCI Express Gen3子系统的各个方面:

1. **特性**:AXI Bridge提供了高速连接,支持PCIe Gen3标准,具有高带宽和低延迟的特性。它允许用户通过AXI接口与FPGA内部逻辑进行通信,同时通过PCIe接口与外部系统交互。

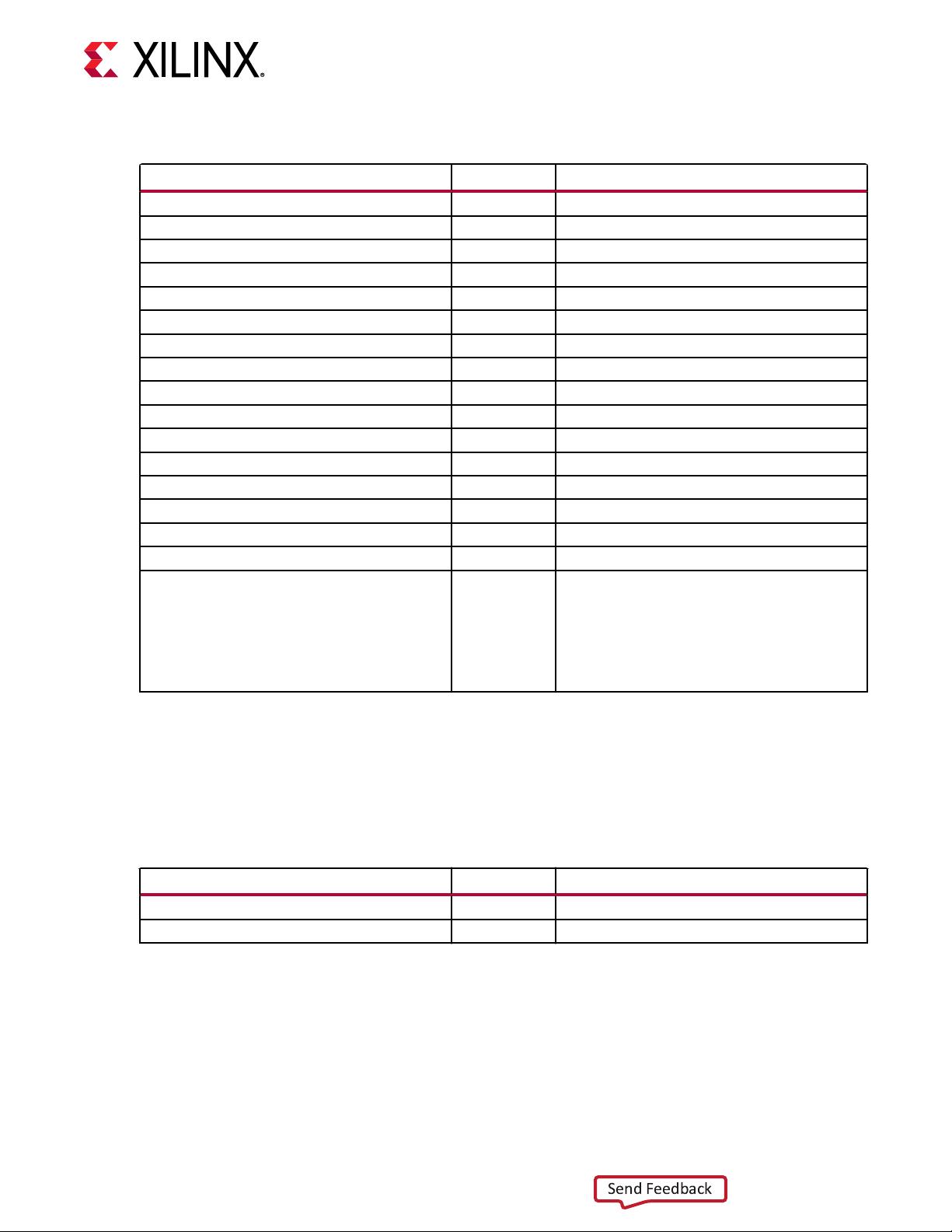

2. **不支持的功能**:文档列出了不支持的特性,这可能包括某些特定的PCIe功能或者特定的系统配置,用户在设计时需要注意这些限制。

3. **限制**:可能包含对最小设备要求的说明,例如需要满足的FPGA资源、时钟速度等限制,确保设计能够正确工作。

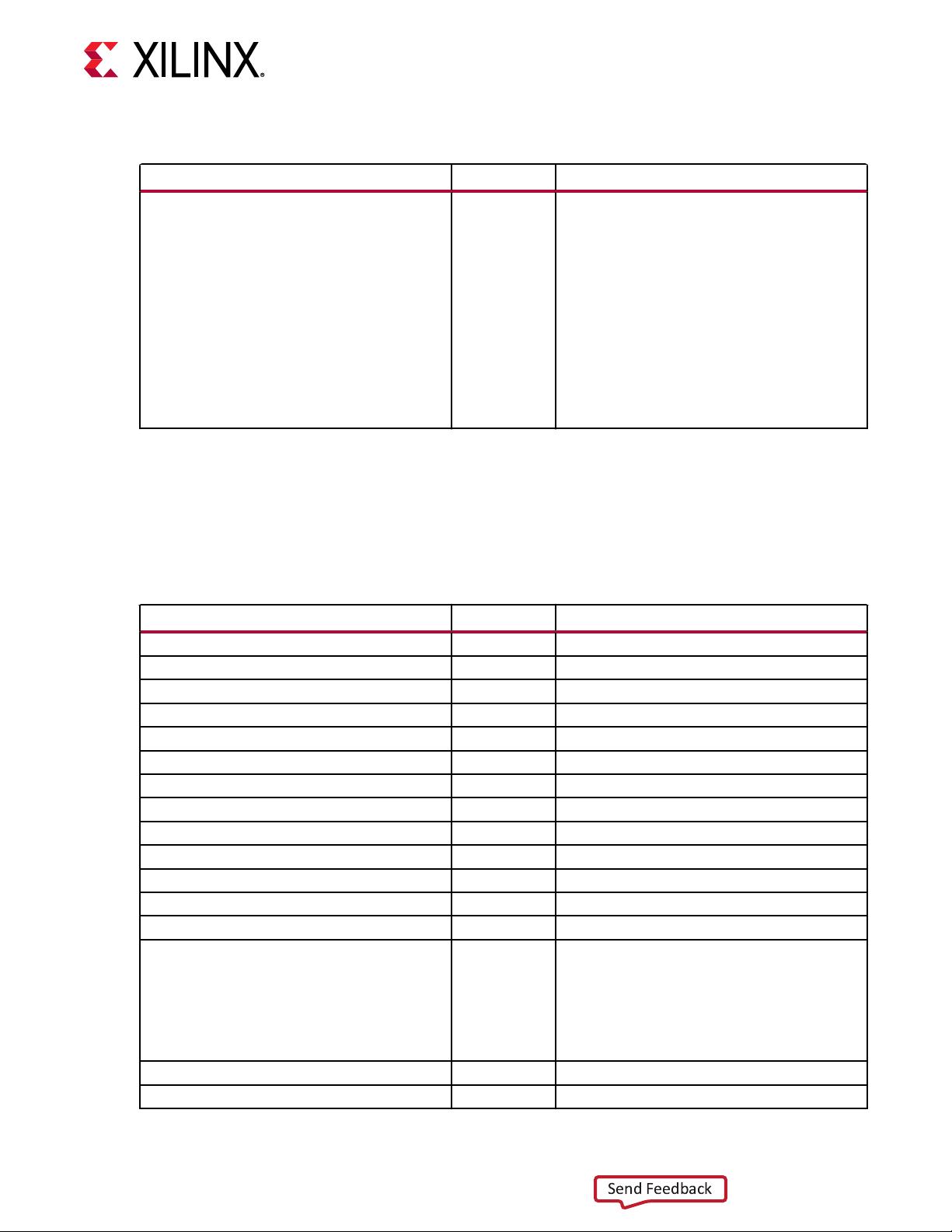

4. **端口描述**:详细介绍了AXI和PCIe端口的配置,包括端口的数量、数据宽度和其他参数,这些信息对于理解如何连接外部设备至关重要。

5. **内存映射**:描述了PCIe地址空间如何映射到FPGA内部的AXI地址空间,这对于理解数据传输路径和地址转换至关重要。

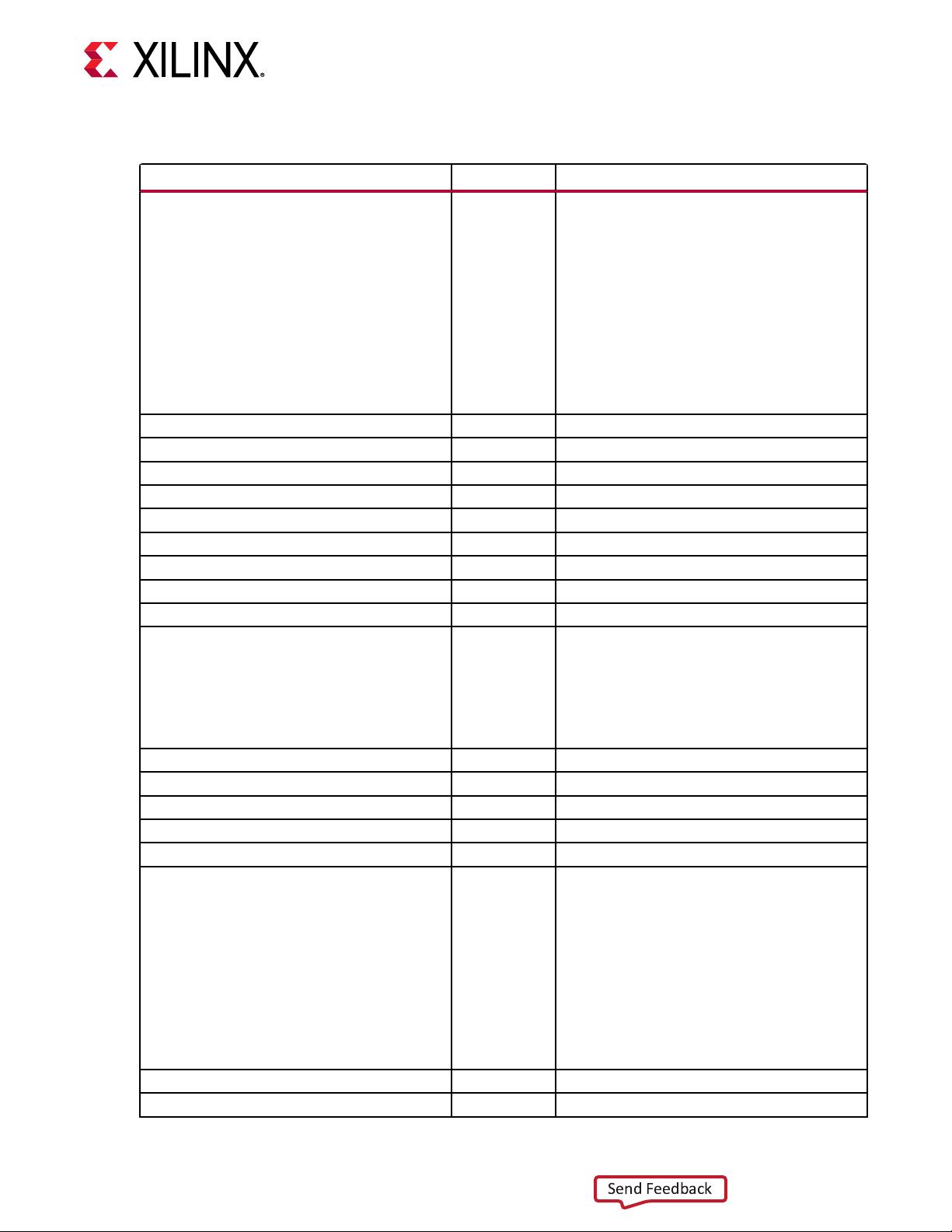

6. **设计指南**:包含了设计时的一般性指导原则,如共享逻辑、时钟管理、复位处理,以及关于AXI到PCIe交易、PCIe的事务排序、基址寄存器(BAR)和地址翻译的详细信息。

7. **异常条件处理**:讨论了在遇到错误或异常情况(如格式错误的TLP数据包)时,IP如何处理和报告问题,确保系统的稳定性。

8. **角色功能**:详细解释了IP作为PCIe终结点(Endpoint)和根端口(Root Port)的角色,以及在串联配置(Tandem Configuration)中的行为。

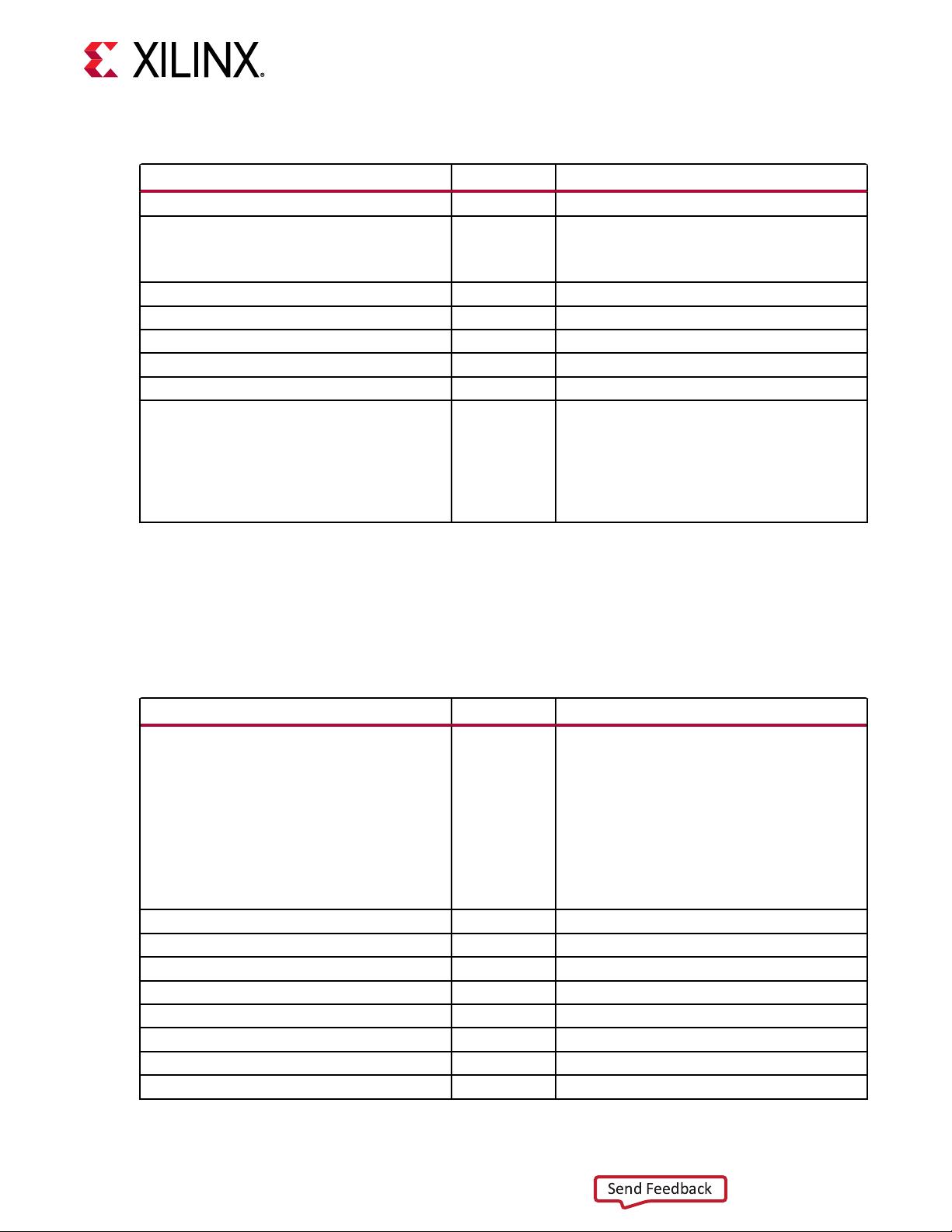

9. **设计流程步骤**:指导用户如何自定义和生成IP,设置约束,进行仿真、综合和实现等设计流程。

10. **示例设计**:提供了一个端点配置的AXI PCIe Block示例,帮助用户了解如何定制和生成IP,并将其应用于实际项目。

AXI Bridge for PCI Express Gen3 Subsystem是Xilinx Vivado Design Suite中的一个重要组件,用于实现高效的FPGA-PCIe接口,支持高性能数据传输。文档详细介绍了从设计到实现的整个过程,是进行相关项目开发的重要参考资料。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-03-22 上传

2021-03-23 上传

2023-11-04 上传

2024-02-21 上传

2022-09-21 上传

2021-08-09 上传

射手Snake357

- 粉丝: 1

- 资源: 12

最新资源

- FooterView,如何阅读java源码,javawebbbs

- caffe2-cpp:使用caffe2库的图像分类和检测C ++示例

- 七彩绚丽背景透明css3模板6126.zip

- mukanren-presentation:关于 µKanren 的演讲

- minutes-api:分分钟项目后端

- 海康监控集成demo web

- R_Packages_Baseball:《 Hardball Times》文章中有关使用R进行棒球分析的代码和数据

- EMD-cc程序,emu,cc,matlab源码.rar

- tick-tock:时间记录应用

- 漂亮的花色背景二栏css3博客模板6125.zip

- (论文+simulink)模型,matlab中histeq函数的源码,matlab源码下载

- global-card-ident:全球发行人的信用卡号的全球JavaScript标识符

- 嵌入式字符设备驱动源代码和Makefile文件和应用层测试文件源代码

- 安卓Android源码——安卓Android 天天动听悬浮歌词源码.zip

- RefluxSimpleApp:非常简单的React + Reflux应用程序

- VectorTuples:使用带有元组的向量类来创建伪优先级队列行为