DDR内存设计基础与硬件要求

版权申诉

201 浏览量

更新于2024-06-18

1

收藏 9.57MB PDF 举报

"DDR设计基础指南.pdf"

DDR设计基础指南是针对内存硬件设计的专业资料,涵盖了DDR内存的基本原理、硬件设计要求、仿真与测试方法。本指南旨在帮助工程师理解和应对DDR内存设计中的挑战,确保在高速发展的CPU技术和严苛应用环境中,内存系统能够稳定运行。

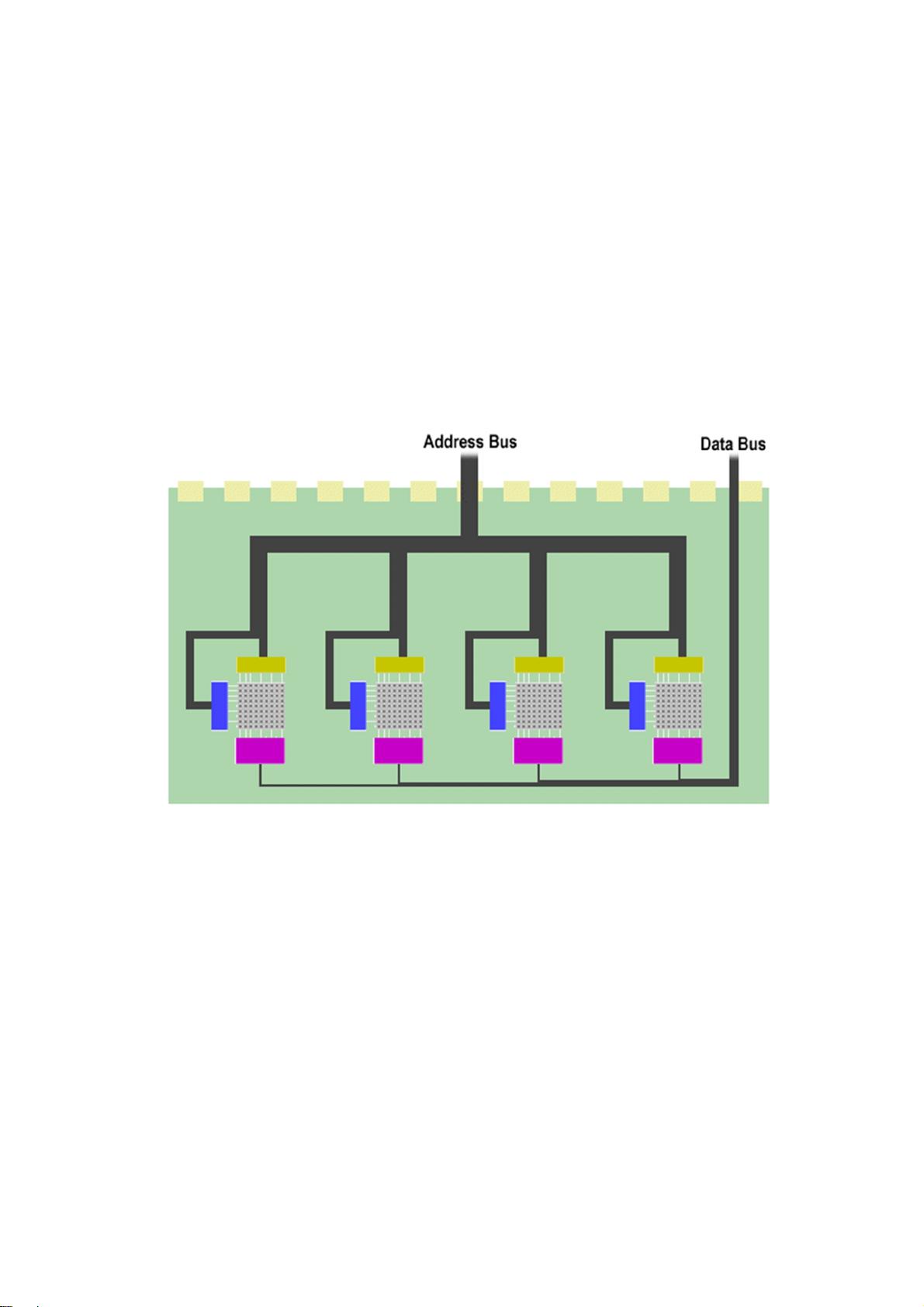

在内存简介部分,介绍了基本存储原理,强调了内存频率的重要性。内存的频率决定了数据传输速率,直接影响系统性能。此外,讲解了内存的几个关键参数,如物理Bank和逻辑Bank,它们影响内存的并行处理能力;tRCD(行地址至列地址延迟)、CL(CAS延迟)和tDQSS(数据有效到DQS strobe的延迟)等时序参数,这些参数定义了数据访问的时间关系;tRP(行预充电有效周期)控制行地址的切换速度;BurstLength(突发长度)决定了连续数据传输的单元大小;DQM(数据掩码)用于选择性地屏蔽数据线上的数据;DQS(数据选取脉冲)是数据同步的关键信号;Refresh(刷新)则是保持内存数据完整性的必要操作。DDR3与DDR2的主要区别在于功耗、速度和信号完整性方面,DDR3更优化。

硬件设计要求章节,重点讨论了电源设计,包括DDR的核心电源VDD和VDDQ以及参考电压Vref的设计,确保电源稳定性对内存性能至关重要。电路设计部分提醒工程师注意信号完整性和电磁兼容性。Vtt是DDR3中的终端电阻电源,其设计影响信号质量。内存的布局也是关键,良好的布局可以减少信号干扰,提高系统稳定性。

在DDR仿真及测试方法中,DDRPCB设计仿真确保在PCB层面的信号质量和时序正确性。DDR测试参数介绍涉及了各种性能指标,如读写速度、时序参数等,以确保内存符合规格。简要可靠性测试方法则提供了一套基础的验证流程,以检测内存系统在不同条件下的稳定性,防止出现EMC问题、高温或低温环境下的不稳定、系统死机或蓝屏等问题。

DDR设计基础指南为工程师提供了全面的DDR内存设计指导,从理论到实践,从参数理解到硬件实现,再到测试验证,全方位覆盖了DDR内存设计的关键环节,有助于构建高效、可靠的内存系统。

2023-08-18 上传

2019-12-05 上传

2019-09-15 上传

2019-09-12 上传

2012-05-11 上传

2021-02-06 上传

2020-03-23 上传

GJZGRB

- 粉丝: 2944

- 资源: 7736

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍